Modelsim SE 问题集锦【原创】

Modelsim版本:Modelsim SE PLUS 6.5

与AE版本在建库时有很大不同。其他操作类似。详见问题一。

另外,有些仿真设置是在Quartus II中进行的,但其属于仿真范围,集中在此博文中。

1.Modelsim 不同版本主要区别http://www.cnblogs.com/Efronc

Modelsim是Model公司开发的目前业内最通用的仿真器之一,它支持Verilog和VHDL混合仿真,仿真精度高,速度快。PC版的仿真速度与工作站版不相上下。

其版本非常多,主要有AE、SE、PE等几种版本,modelsim-altera版本属于AE版本(OEM版本),功能有限,速度慢。只有一些基本功能,不支持Verilog、VHDL混合仿真,定制或改变GUI和集成仿真性能仿真器,加速模块等。但其也有其方便的方面,例如在进行时序仿真时,AE版本的modelsim安装目录下有一个altera的文件夹,里面有各种系列芯片已经编译好的ATOM(底层硬件原语仿真库)文件夹,直接复制到正在仿真目录下即可。但SE版本和PE版本的需要在Quertus II安装目录下找到一个EDA的文件夹,下面sim-lib文件夹下有各种型号芯片的Verilog和VHDL仿真库,即文件名后面是_atom.v(硬件原语仿真库文件)和_mf.v(宏仿真库文件),仿真时需要将他们与testbench一起编译。

SE版本中也有一些更加方便仿真的工具,例如可以自行增加光标等,AE版本中则没有这些工具。

2.波形窗口信号一直是红色的高阻态http://www.cnblogs.com/Efronc

在modelsim中未初始化的引脚或变量是x,对其取反读取等操作是没有意义的。这一点与Quartus II自带的仿真器不同,Quartus II初始化状态是0。以如果要用modelsim来仿真的话一定要把每个变量都初始化,具体设计中需要加一个复位端口。另外,如果在Quartus II中直接调用Modelsim仿真的话可以不初始化,Quartus II会自动处理。

3.vo和sdo是什么文件?http://www.cnblogs.com/Efronc

这两个文件是在设置好的output directory目录下生成的文件。这两个文件是时序仿真所必须的。其中vo文件是此设计的逻辑网表文件,这个大家应该都很熟悉了。sdo文件(或sdf文件)是标准延时文件(standard delay format timing annotation),是由FPGA厂商提供的其物理硬件原语时序特征的表述,包含了元件延时信息的最小值、最大值、典型值等供第三方工具使用(里面不仅有门延时,更有布线延时等,所以跟实际芯片工作的时序十分相似)。

Modelsim仿真时只需编译.VO文件即可。因为在.VO文件中有一句initial $sdf_annotate("test_sim_v.sdo");任务反标了,不需要手动指定。

4.Modelsim预先安装库IEEE

包含预编译的synopsys的IEEE算法包,用于仿真加速等。其他库都有专用用途,初学者不宜更改。

5.Modelsim对Verilog实例的搜寻规则

1.按照vsim命令行中的-Lf(或-L)参数指定的各库逻辑名在命令行中的先后顺序,进行库搜寻。

2.搜寻work库。

3.搜寻在实例名中专门指定的库。

6.AE版本加载库错误http://www.cnblogs.com/Efronc

在使用modelsim-altera的时候,会发现在加载库时,总会出现下面的错误:

# ** Fatal: SDF files require Altera primitive library

# Time: 0 ps Iteration: 0 Instance: /TEST_vlg_vec_tst File:C:/altera/test/test_bench.v

# FATAL ERROR while loading design

原因是缺少altera原语库,解决方式是到QUARTUS目录下如\altera\90\modelsim_ae\altera\verilog\cycloneii中去拷贝已经为modelsim编译好的库,这样就可以正常加载了.

7.无限次实例

# Loading postsim.adder8

# ** Warning: (vsim-3035) Instantiation depth of '/adder8/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1' is 51. This might indicate a recursive instantiation. Increasing limit to 75.

# ** Error: (vsim-3036) Instantiation depth of '/adder8/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1' is 75. Assuming recursive instantiation.

# Region: /adder8/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1/m1

在仿真激励中实例名称和被实例的名称相同,就会出现这种无限次实例化现象。

8.testbench和testvector

自己用Verilog写仿真激励的,那是vector还是bench呢?

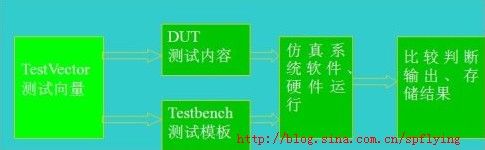

其实,testvector只有在altera这里才有这种说法,因为altera的开发工具Quartus II提供了一种用波形文件来产生激励的方式,而这个波形文件就是进行仿真时的测试向量(testvector)。而我们自己写的激励是testbench,其实testvector可以转换为testbench,testbench用于第三方工具,如modelsim仿真。

9.加载库错误http://www.cnblogs.com/Efronc

# ** Error: (vsim-3033) D:/Programs/Quartus/test_sim/simulation/modelsim/test_sim.vo(137): Instantiation of 'cycloneii_lcell_comb' failed. The design unit was not found.

# Region: /test_sim_sim/a_sim

# Searched libraries:

# D:\Programs\Quartus\test_sim\simulation\modelsim\work

原因是库未加载进来,详见Modelsim SE 进行时序仿真及altera库的添加 【原创】博文中的Modelsim库介绍。