高速互连系统——基本硬件单元

模拟乘法器

模拟乘法器分为二象限乘法器和四象限乘法器

- 二象限乘法器:一个输入电压极性可正可负,另一个只能单一极性。

- 四象限乘法器:两个输入极性都可正可负。

二象限变跨导模拟乘法器

暂无

四象限吉尔伯特模拟乘法器

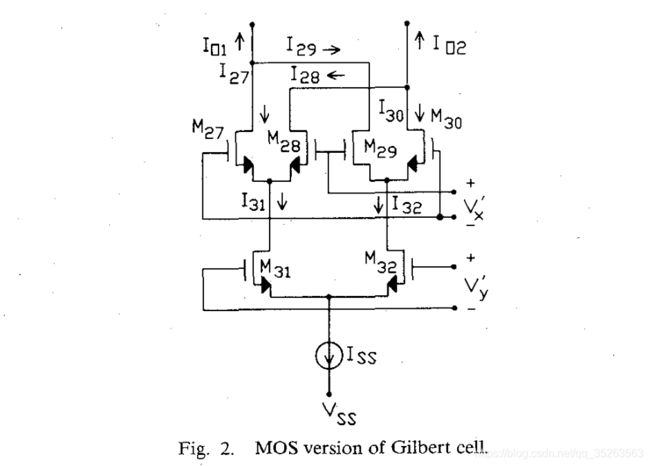

基本吉尔伯特单元

下图参考1

在论文中提到,假设图中所有MOS管工作于饱和区,满足MOS管平方工作规律,尺寸满足跨导 K ∗ K_* K∗相同,即尺寸相同。

K a = K 27 = K 28 = K 29 = K 30 K_a=K_{27}=K_{28}=K_{29}=K_{30} Ka=K27=K28=K29=K30

K b = K 31 = K 32 K_b=K_{31}=K_{32} Kb=K31=K32

I 0 d = 2 K a K b ∗ V x ′ V y ′ I_{0d}=\sqrt{2K_aK_b}*V_x^{'}V_y^{'} I0d=2KaKb∗Vx′Vy′

其中 K a K_a Ka和 K b K_b Kb的参数可自己配置。

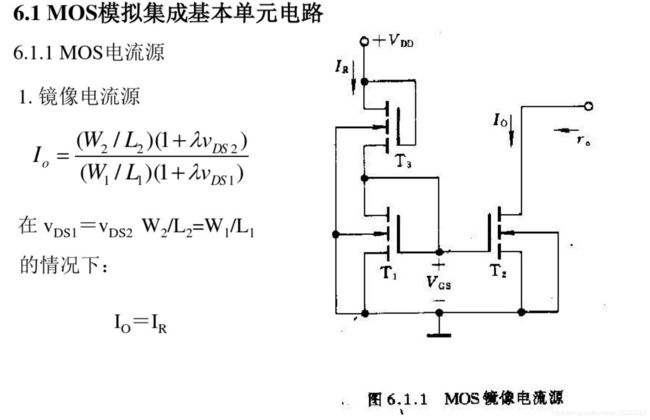

电流源

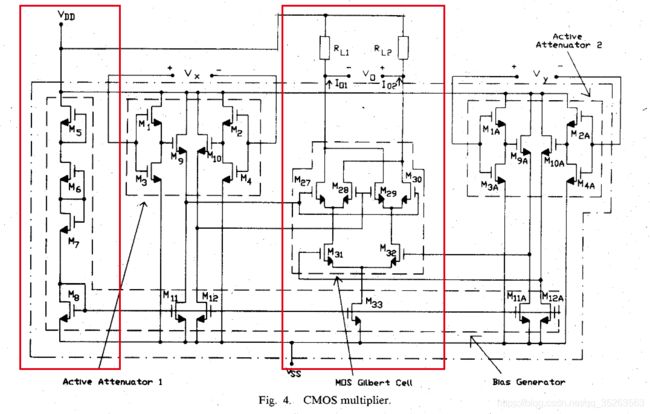

整体结构

只看红色部分,图片来自3。左边为比例电流源,右边为吉尔伯特单元加电阻,将电流转化成电压方式输出。

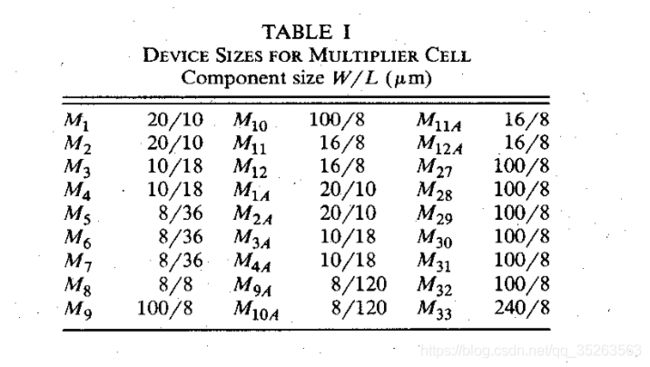

注意:左边电流源上半部分三个MOS管数量只要是为了消耗供电电压裕度,这篇文章 V D D V_{DD} VDD为5V。关于尺寸问题,文章中也单独列出表格。工艺为3 μ m \mu m μm。

cadence搭建

等过段时间回学校

模拟加法器

模拟电压加法器工作思路是:

- 将电压转换为电流:主要运用MOS管或者电阻;

- 电流求和:通过互连线直接相接即可;

- 电流再转换为电压:输出端通过上拉电阻与电源电压实现。

下面举两个例子

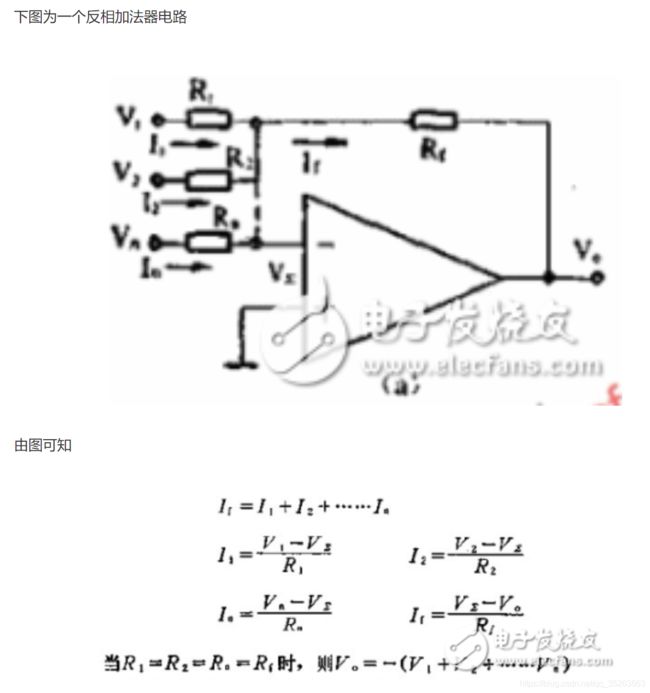

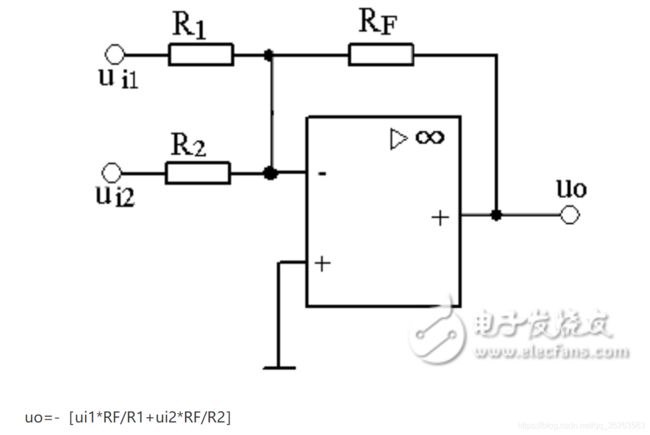

1

从模电的运算放大器入手。根据运算放大器虚短、虚断特性,将电压转化成电流,电流相加,在用电阻转化成电压。下两图参考4。

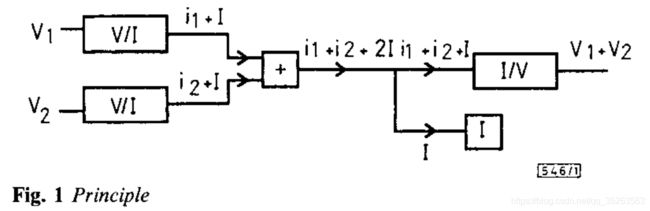

2

参考5。

根据论文中的说明,M9与M10是镜像的,其电流相等。M1-M8尺寸相同,M9-M10为其余的三倍。

延迟单元

主要分三个方面:

- 触发器

- 多级缓冲器

- LC网络

触发器

锁存器(latch)或者触发器(flip-flop)。

下面参考自6。

- filp-flop是触发器,在时钟信号有效时候才检测输入改变输出;latch是锁存器,是组合逻辑,不依赖时钟信号,总是根据输入改变输出。FPGA设计中总是讲到要避免使用latch。

- latch和flip-flop都是时序逻辑,区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

- latch缺点:

1、没有时钟端,不受系统同步时钟的控制,无法实现同步操作;

2、对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生; - 简单回答就是Latch是异步电路,flip-flop是同步电路。

- 既然是同步电路,肯定有clock端了,而latch就没有;但是在IC设计中,latch相对flip-flop只占用其三分之一的面积。

- register一般是由Latch or flip-flop实现的。

缓冲器

主要采用多级反相器组成,根据本人经验,这种延迟结构带宽,工艺PVT等稳定性都会有问题。

LC网络

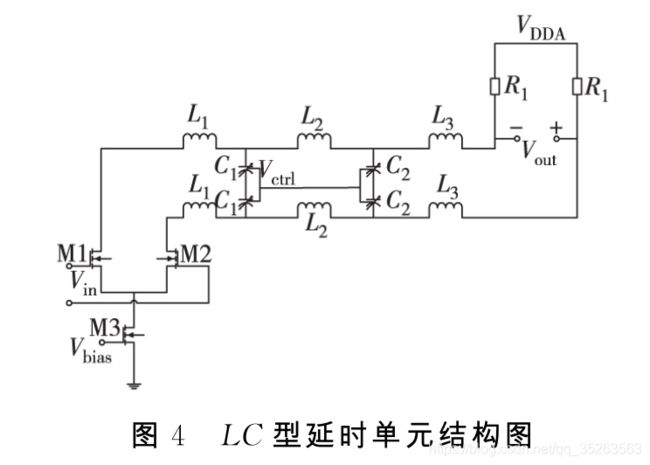

思路为采用电容电感搭建类似传输线结构,图片来自7。

再很多高速传输电路中,精确延迟一个码元时间,缓冲器和触发器结构的延迟单元,无法做到微小延迟。

根据此文章内说明,此结构延迟为

t = ( L C ) 1 / n t=(LC)^{1/n} t=(LC)1/n

n n n为串联 L C LC LC的级数。

具体该结构模型分析计算,可参考8。但是百度学术无法查到这篇文章,关于LC延迟问题,我们可以采用互连线模型分析,当高频信号再互连线上传播时,信号的传播速度与 L C \sqrt{LC} LC乘积成反比。

比如下图的延迟单元,相当于两级延迟,两个 L 1 L_1 L1、两个 L 2 L_2 L2和两个 C 1 C_1 C1组成第一级延迟单元;两个 L 2 L_2 L2、两个 L 3 L_3 L3和两个 C 1 C_1 C1组成第二级延迟单元。单级延迟单元延迟如下计算

t = ( L 1 / / L 2 ) ∗ C t=(L_1//L_2)*C t=(L1//L2)∗C

L 1 L_1 L1与 L 2 L_2 L2为并联;且共一级LC。

B. Gilbert, “A high-performance monolithic multiplier using active feedback,” IEEE J. Solid-State Circuits, vol. SC-9, pp. 364-373, Dec. 1974. ↩︎

https://wenku.baidu.com/view/e1e4e95df02d2af90242a8956bec0975f465a43f.html ↩︎

A +-5-V CMOS Analog Multiplier ↩︎

http://www.elecfans.com/dianlutu/187/20180117617264_4.html ↩︎

Chaoui, H. CMOS analogue adder[J]. Electronics Letters, 1995, 31(3):180-181. ↩︎

https://zhidao.baidu.com/question/1863373259630133187.html ↩︎

一种基于65nm CMOS工艺的3抽头前馈均衡器 ↩︎

吴凌涵.高速串行接口均衡电路关键技术研究 [D].北京:清华大学,2014:15-16. ↩︎