计算机组成原理5----存储器与CPU连接以及存储器校验

1.存储器容量扩展

位扩展 增加存储字长 即增加数据线位数

A0-A9地址线 D0-D3右边芯片,D4-D7左边芯片 CS片选信号 同时选中 WE读写信号

字扩展 增加字数 增加地址线位数

A10地址位与CS0相连,A10非与CS1相连,当A10=1时,右边选中,A10=0时,左边选中

字位扩展

将8片分为4组,每组实现位扩展,四组组合实现字扩展。A10,A11由片选译码产生片选信号,来决定选择哪一组芯片。

2.存储器与CPU连接

存储器与cpu之间需要进行连接,主要包括地址线,数据线,读写命令线以及片选线的连接

地址线由于CPU地址线一般多于存储芯片地址线,因此一般cpu低位地址线与存储芯片相连,高位地址线用作控制信号

如果芯片数据线小于cpu数据线,则需要对于芯片进行位扩展

读写命令线一般直接相连即可,片选信号CS和CPU访存控制线号MREQ

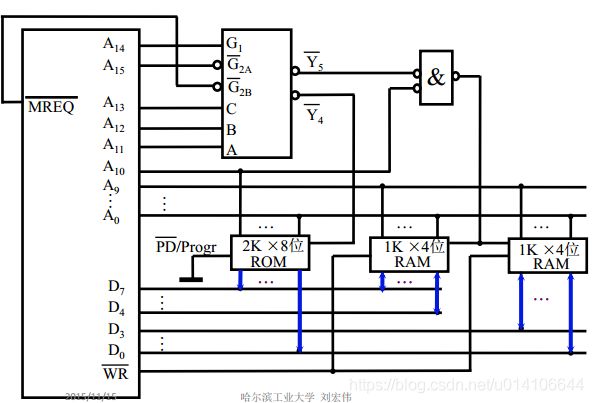

示例1(P94):cpu16位地址线,8位数据线,MREQ低电平访存控制线号,WR读写控制信号(高电平读 低电平写)

实现6000H-67FFH系统程序区,6800H-6BFFH用户程序区

系统程序区应该选择ROM 用户程序区选择RAM

1.写出对应的二进制地址码

2.确定芯片数量及类型

对于系统程序区,地址变化为A0-A10 全0到全1,因此需要一片2Kx8位ROM

对于用户程序区,地址变化A0-A9,需要一片1Kx8位RAM,由于芯片种类限制,这里采用2片1Kx4位RAM进行位扩展

3.分配地址线

4.确定片选信号

A15为0与译码器G2A连接

A14为1与译码器G1连接

A13,A11,A10分别与CBA连接,当输出100=4时应该选中ROM芯片,输出为101=5时应该选中RAM芯片

因此Y4与ROM片选信号CS相连,如果译码器输入CBA=100,则Y4输出低电平,ROM选中开始工作

对于两片RAM来说,可以使用A10来作为片选信号,首先只有当Y5有效时,才表明选中RAM,然后由A10来实现同时选中两片RAM实现位扩展。

MREQ为访存控制线号,只有为低电平才表示访问存储器因此与G2B连接。

3.存储器校验

编码的最小距离:任意两组合法代码之间二进制位数的最小差异

编码的纠错,检错能力与编码的最小距离有关

假定代码集合为{00000,11111},则当出现10000时,可以判断原码为00000,当出现11000时,原码为00000,当出现11100时,无法判断原码为00000或者11111,因此集合编码最小距离为L=5,检错位数D=2,纠错位数C=2

汉明码

汉明码采用奇偶校验,分组校验,给定一串二进制,在1,2,4...位置进行元素插入,然后进行分组,使得每一组都满足奇偶校验

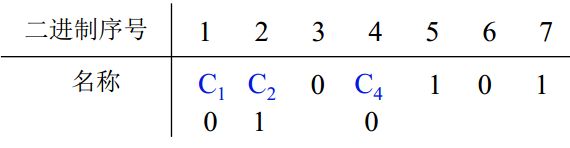

假定数据为1234567,则124为校验位,分成三组:

1357 2367 4567分成三组,假定为偶校验,则正常情况下P3P2P1输出应为000,如果001,则说明第一组出错而二三组没错,因此出错为必为1,同理111说明三组都错即出错为必为7.

汉明码组成如下所示

求0101按偶校验配置汉明码

n=4 可以求得k=3,则有

由于偶校验, 1357=C1011,则C1=0,同理C2=1,C4=0,则最终结果为0100101.

原始数据为0101,编码之后为0100101,则可以实现一位纠错一位检错

求0011按偶校验配置汉明码

n=4 可以求得k=3,则有

最终编码为1000011

偶校验接收编码为0100111,求原始数据

第6位出错。即0100101,去掉124位置,则原始数据为0101。

4.提高访存措施

采用高速器件

采用层次结构 Cache-主存

调整主存结构

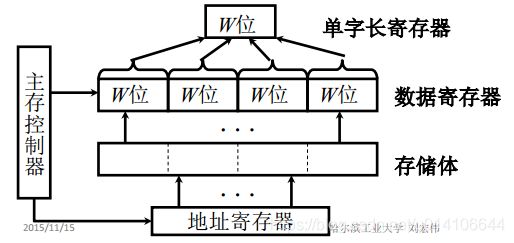

单体多字系统

如果数据和程序连续存放,cpu连续访问信息,则可以一个存取周期取出多个存储单元的数据,增加存储器带宽

多体并行系统

高位交叉 多个存储器顺序编址 数据按照顺序存放 多个请求源同时访问多个存储器

低位交叉 各个体轮流编址

在不改变存储周期前提下,提高存储器带宽

cpu时钟周期要远远快于存储器访存周期,因此在一个单体访存周期,cpu可以轮流访问多个存储器的数据,从实现在一个访存周期,cpu获取多个存储器数据,从而增加存储器带宽。