基于linux5.15.5的IMX 参考手册 --- 7

基于linux5.15.5的IMX 参考手册 — 7

4.8 PCI Express根复合体

4.8.1介绍

包含在i.MX SoC中的PCI Express硬件模块,可以配置为作为根复合体或PCIe端点。本文档用于描述i.MX SoC家族上的PCI Express根复合体实现。它还描述了在i.MX PCI Express设备上配置和操作Root Complex所需的驱动程序。

PCI Express (PCIe)是第三代I/O互连,目标是低成本、高容量、多平台互连使用。它具有较早的PCI和PCI- x的概念,并提供了对现有PCI软件的向后兼容性,但有以下区别:

•PCIe是点对点互连

•设备之间的串行连接

•基于包的通信

•通过从X1到X16的聚合车道实现可扩展性能

•两个以上的PCIe设备需要连接PCIe交换机

4.8.2术语和约定

本文档中使用的术语和约定如下:

•桥

一种功能,通过内部组件互连或与其他PCI/PCI- x总线段或PCI Express Port互连,虚拟或实际连接PCI/PCI- x总线段或PCI Express Port。

•下游

—一个互连/系统元件(端口/组件)相对于根复合体的位置。

交换机上非“上行端口”的端口称为“下行端口”。根交换机上的所有端口均为下行端口。链接上的下游组件是离根复合体更远的组件。

-信息流的方向,信息从根复合体流出。

•端点

几个已定义的系统元素之一。一个具有Type 00h配置空间头的函数。

•主机

由一个(或多个)中央处理单元(CPU)和资源组成的实体,如内存(RAM),可以通过根综合体连接到多个PCIe节点共享。

•车道

一组差分信号对,一对用于传输,一对用于接收。

•链接

两个端口及其相互连接的通道的集合。链路是两个组件之间的双单工通信路径。

•PCIe结构

由各种PCI Express节点(也称为设备)组成的拓扑结构。fabric中的设备可以是Root Complex、Endpoint、pci - pci /PCI-X Bridge或Switch。

•端口

—逻辑上,组件与PCI Express Link之间的接口。

-物理上,位于同一芯片上的一组发射器和接收器定义了一个链路。

•根复合体

一种已定义的系统元素,包括一个主机桥、零个或多个根复杂集成端点、零个或多个根复杂事件收集器以及一个或多个根端口。

•根端口

根综合体上的PCI快速端口,它通过关联的虚拟PCI-PCI桥映射层次结构的一部分。

•上游

—互联/系统元件(端口/组件)离“根Complex”越近的相对位置。交换机拓扑上离根交换机最近的端口为“上行端口”。仅包含端点或桥接功能的组件上的端口称为上游端口。链接上的上游组件是靠近根综合体的组件。

织物的任何元素,相对接近钢筋混凝土被视为“上游”。所有PCIe端点端口(包括桥的终止点)和交换机端口,更接近RC在该设备上被称为上游端口。Upstream Flow是指流向RC的通信。

4.8.3 i.MX上的PCIe拓扑

i.MX上有一个PCIe接口。目前在Linux BSP中只启用了RC模式。

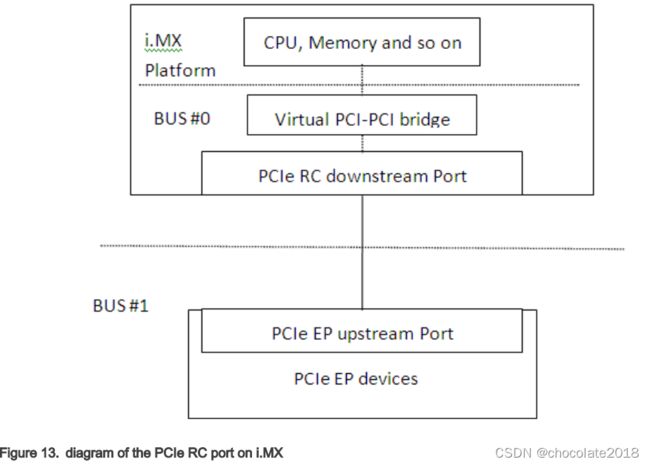

i.MX上的PCIe RC接口示意图如下图所示。

PCI枚举映射

由于PCI Express是点对点拓扑,为了保持与用于软件枚举的旧PCI总线-设备概念的兼容性,我们引入了以下概念,允许在PCI设备/功能方面识别各种节点及其内部(例如PCIe交换机):

•主机网桥: 集成到RC中的网桥,与主机具有PCI兼容的连接。此网桥的PCI端始终为总线#0。这意味着,总线上的设备将是主机本身。

•虚拟PCI-PCI桥:每个PCI Express端口作为RC或Switch的一部分被视为虚拟PCI-PCI桥。

这意味着每个端口都有一个主和从PCI总线,下游被映射到远程配置空间。

•根端口关联的虚拟桥在主端有#0总线,在下游有辅助总线。

•每个PCIe交换机被视为与下行端口数量相同的虚拟PCI-PCI桥的集合,连接到一个虚拟PCI总线,该虚拟PCI总线实际上是构成交换机上游端口的另一个PCI-PCI桥的辅助总线。

•每个EP的上游端口可以是代表交换机下游端口的虚拟PCI-PCI Bridge的次要总线段的一部分,也可以是根端口的一部分。

4.8.4特性

以下是i.MX作为PCI Express根复杂驱动程序所支持的各种特性。

•符合Express Base规范2.0版。

•Gen2操作与x1链路支持5 GT/s的原始传输速率在单一方向。

•支持传统中断(INTx)和MSI。

•最大有效负载大小(128字节)。

•它适合Linux PCI总线框架,提供PCI兼容软件枚举支持。

•此外,它提供了端点驱动程序的接口,以访问各自的设备检测下游。

Linux操作系统中的PCI Express端口总线驱动程序框架可以使用相同的接口来处理AER、ASP等。

•EP驱动的中断处理设施可以是传统中断(INTx)。

•通过Linux PCI子系统中的通用I/O附件访问EP I/O bar。

•无缝处理PCIe错误。

•支持L0 / L0 / L1 / L1.1 ASPM电源管理。

4.8.5 Linux OS PCI子系统及RC驱动

在Linux操作系统中,PCI实现大致可以分为以下几个主要部分:PCI BIOS架构、具体的Linux操作系统实现、主机控制器(RC)模块和核心。

•PCI BIOS架构特定的Linux操作系统实现启动PCI总线初始化。它与PCI主机控制器代码和PCI核心接口,执行总线枚举和资源分配,如内存和中断。BIOS执行的成功完成确保系统中的所有PCI设备都被分配了可用PCI资源的一部分及其各自的驱动程序(称为Slave驱动程序)。PCI可以使用PCI Core提供的设备来控制它们。可以跳过资源分配(如果它们是在Linux操作系统启动之前分配的,例如PC场景)。

•主机控制器(RC)模块处理特定于硬件(SoC+板)的初始化和配置,并调用PCI BIOS。它应该为BIOS和PCI Core提供回调函数,在PCI系统初始化和访问PCI总线进行配置周期时调用这些回调函数。它提供可用的内存/IO空间、INTx中断线、MSI的资源信息。它还应该通过in x () out x()促进IO空间访问(正如支持的那样)。您可能需要通过read x () write x()提供间接内存访问(如果h/w支持)。

•Core为总线设备创建并初始化数据结构树,以及在系统中架桥,处理总线/设备编号,创建设备条目和proc/sysfs信息,为BIOS和从驱动提供服务,并提供热插拔支持(h/w支持可选/)。它针对(EP)驱动程序接口查询,并初始化枚举过程中找到的相应设备。它还提供了MSI中断处理框架和PCI快速端口总线支持。它提供热插拔支持(如果支持)、高级错误报告支持、电源管理事件支持和虚拟通道支持,以在PCI express端口上运行(如果支持)。

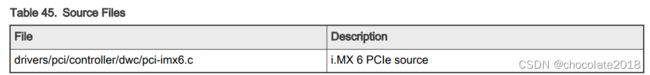

4.8.6 PCIe驱动源文件

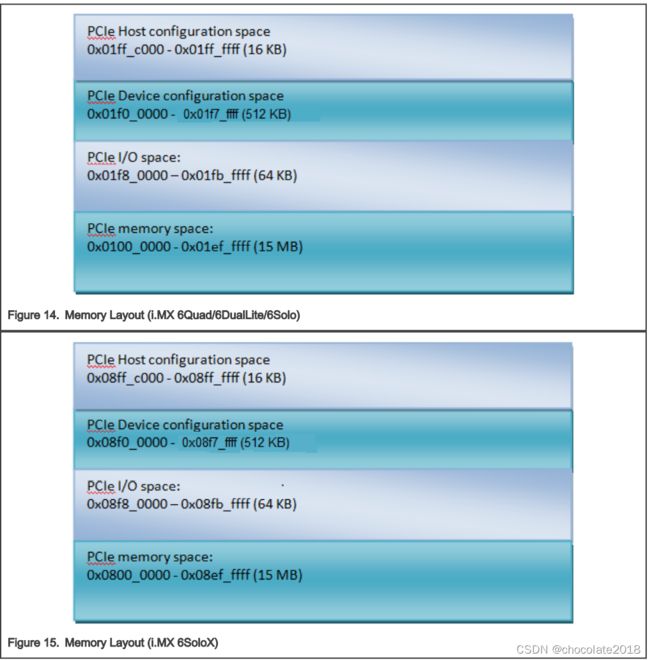

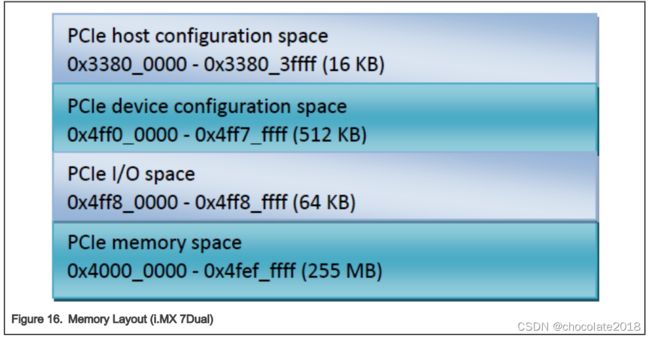

4.8.7系统资源:内存布局

•IO和内存空间是两个地址空间,设备使用它们与运行在Linux内核CPU上的设备驱动程序通信。

•16kb以上PCIe主机配置空间。

—该内存段用于映射PCIe RC的配置空间。SW可以通过DBI接口访问PCIe RC核心配置空间。

•PCIe设备配置空间。

—用于映射插入RC下游端口的PCIe EP设备的配置空间。

i.MX 8 quadmax / 8 quadxplus:

i.MX 8QuadMax同时有PCIeA和PCIeB,而i.MX 8QuadXPlus只有PCIeB。

•PCIeA

—PCIe主机配置空间:0x5f00_0000—0x5f00_ffff (64K bytes)

—PCIe设备配置空间:0x6ff0_0000—0x6ff7_ffff (512K字节)

—PCIe IO空间:0x6ff8_0000—0x6ff8_ffff (64K bytes)

—PCIe内存空间:0x6000_0000—0x6fef_ffff (255M bytes)

•PCIeB

—PCIe主机配置空间:0x5f01_0000—0x5f01_ffff (64K bytes)

—PCIe设备配置空间:0x7ff0_0000—0x7ff7_ffff (512K字节)

—PCIe IO空间:0x7ff8_0000—0x7ff8_ffff (64K字节)

—PCIe内存空间:0x7000_0000—0x7fef_ffff (255M字节)

i.MX 8M Quad:

•PCIe0

—PCIe主机配置空间:0x3380_0000—0x33bf_ffff (4Mbytes)

—PCIe设备配置空间:0x1ff0_0000—0x1ff7_ffff (512K字节)

—PCIe IO空间:0x1ff8_0000—0x1ff8_ffff (64K bytes)

—PCIe内存空间:0x1800_0000—0x1fef_ffff (127M bytes)

•PCIE1

—PCIe主机配置空间:0x33c0_0000—0x33ff_ffff (4Mbytes)

—PCIe设备配置空间:0x27f0_0000—0x27f7_ffff (512K字节)

—PCIe IO空间:0x27f8_0000—0x27f8_ffff (64K bytes)

—PCIe内存空间:0x2000_0000—0x27ef_ffff (127M bytes)

4.8.8系统资源:中断线

i.MX Root Complex驱动程序在i.MX 6平台上为MSI INT使用中断线152,在i.MX 7Dual平台上为MSI INT使用中断线154。

4.9 USB

4.9.1介绍

USB (universal serial bus)驱动实现了与CHIPIDEA USB- hs OTG控制器的标准Linux驱动接口。

USB提供了一种通用链路,可用于各种PC到外围设备的互连。它支持即插即用、端口扩展和任何使用相同类型端口的新USB外围设备。

CHIPIDEA USB控制器符合增强主机控制器接口(EHCI)。这个USB驱动器有以下特点:

•支持高速OTG核心

•高速主机仅支持核心(Host1),支持高速、全速、低设备

•高速芯片间核心(Host2和Host3)

•支持高速主机专用核心(OTG2)、高速、全速和低速设备。默认情况下,USB2Pci网桥连接到OTG2。因此,用户可能无法在此端口上连接其他USB设备。

•高速芯片间核心(Host2)

•主机模式-支持HID(人机界面设备)、MSC(海量存储类)

•外设模式-支持MSC和CDC(通信设备类)驱动程序,包括以太网和串行支持

•嵌入式DMA控制器

4.9.2体系结构概述

USB主机系统由多个硬件和软件层组成。

下图显示了支持USB 2.0的主机系统中构建模块层的概念框图。

4.9.3硬件操作

有关硬件操作的信息,请参阅EHCI规范。EHCI -r10.pdf。

该规范可在USB 2.0增强型主机控制器接口:规范中获得

4.9.4软件操作

Linux操作系统自带USB驱动,用于实现USB协议。对于USB主机,它只实现硬件指定的初始化功能。对于USB外设,它实现了小工具框架。OTG支持ID动态交换机主机/设备模式。目前支持USB运行时挂起,即USB不使用时(主机模式和外设模式),USB将进入低功耗模式。

4.9.5源代码结构

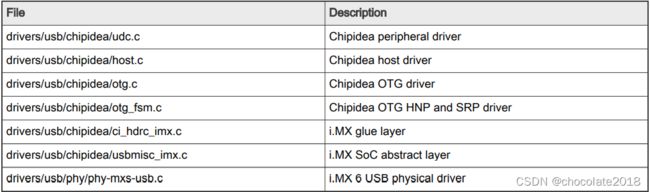

下表描述了驱动程序/ USB中的USB源。

表46. Chipidea USB驱动文件

![]()

4.9.6菜单配置选项

在菜单配置中启用以下模块。

设备驱动程序> []USB支持> EHCI HCD (USB 2.0)支持和ChipIdea高速双角色控制器[]USB物理

层驱动程序- - - >

Device Drivers > USB Physical Layer drivers > Freescale MXS USB PHY support

Device Drivers > USB Gadget Support

1. CONFIG_USB-Build Support for Host-side USB

2. CONFIG_USB_EHCI_HCD EHCI HCD (USB 2.0) support

Default y

3. CONFIG_USB_CHIPIDEA- ChipIdea high-speed Dual Role Controller

Default y

4. CONFIG_USB_CHIPIDEA_UDC - ChipIdea device controller

Default y

5. CONFIG_USB_CHIPIDEA_HOST - ChipIdea host controller

Default y

6. CONFIG_USB_GADGET - USB Gadget Support

Default y

7. CONFIG_USB_MXS_PHY - Freescale MXS USB PHY support

Default y

4.9.7 USB唤醒使用

下面以OTG端口和第一个EHCI设备为例。

控制器唤醒设置,经过以下设置后,VBUS和ID将成为唤醒源。

echo enabled > /sys/bus/platform/devices/20c9000.usbphy/power/wakeup

echo enabled > /sys/bus/platform/devices/2184000.usb/power/wakeup

echo enabled > /sys/bus/platform/devices/ci_hdrc.0/power/wakeup

EHCI唤醒设置,经过以下设置后,主机将具有唤醒能力,如远程唤醒和连接/断开唤醒

echo enabled > /sys/bus/usb/devices/usb1/power/wakeup

echo enabled > /sys/bus/usb/devices/1-1/power/wakeup

4.9.8如何关闭USB子设备电源

以下代码串概述了如何关闭USB子设备电源:

echo auto > /sys/bus/usb/devices/1-1/power/control

echo auto > /sys/bus/usb/devices/1-1.1/power/control (If there is a hub at USB device)

4.9.9修改控制器工作模式

要改变默认设置,可以使用修改DTS文件的方法如下:

dr_mode = "host" /* Set controller as gadget-only mode */

dr_mode = "peripheral" /* Set controller as host-only mode */

dr_mode = "otg" /* Set controller as otg mode */

4.9.10可加载模块支持

modprobe实用程序将自动加载所有模块之间有依赖关系的模块。

加载命令如下:

modprobe phy_mxs_usb

modprobe ci_hdrc_imx

卸载命令如下:

modprobe -r ci_hdrc_imx

modprobe -r phy_mxs_usb

4.9.11 USB充电器检测

i.MX SoC具有USB充电器检测能力,但无充电能力。用户可以通过/sys入口了解USB充电器类型、充电电流、充电器是否存在,如下三行:

cat /sys/class/power_supply/imx6_usb_charger/type

cat /sys/class/power_supply/imx6_usb_charger/current_max

cat /sys/class/power_supply/imx6_usb_charger/present

目前,i.MX 6 Sabre-SD单板不支持USB充电器检测功能。i.MX 6 Sabre-Auto支持该功能.

4.9.12嵌入式主机认证

4.9.12.1添加TPL支持属性

为了通过嵌入式主机USB认证,需要在DTS中添加“TPL -support”来启用目标外设列表(TPL)。例如,在imx6ultralite EVK板(imx6ul-14x14-evk.dts)的主机端口上启用TPL:

&usbotg2 {

dr_mode = "host";

disable-over-current;

tpl-support;

status = "okay";

};

4.9.12.2 VBUS控制

在Linux USB主机功能就绪之前,应关闭VBU。例如,在i.MX 6UltraLite EVK板上,由于引脚与触摸功能多路复用,您需要对该板进行重新设置,以使GPIO(GPIO1\U IO02)选择用于VBUScontrol。

&tsc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_tsc>;

xnur-gpio = <&gpio1 3 0>;

measure_delay_time = <0xffff>;

pre_charge_time = <0xfff>;

status = "disabled";

};

在其DTS文件(imx6ul-14x14-evk.DTS)中禁用触摸功能,如下所示:

pinctrl_usb_otg2: usbotg2grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0xb0

>;

};

reg_usb_otg2_vbus: regulator@2 {

compatible = "regulator-fixed";

reg = <2>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usb_otg2>;

regulator-name = "usb_otg2_vbus";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

gpio = <&gpio1 2 GPIO_ACTIVE_HIGH>;

enable-active-high;

};

&usbotg2 {

vbus-supply = <®_usb_otg2_vbus>;

dr_mode = "host";

disable-over-current;

tpl-support;

status = "okay";

};

4.10 USB3

4.10.1介绍

对于i.MX 8和i.MX 8X家族,一个来自Cadence的超高速USB IP提供支持USB 3.0,其中包括一个新的传输速率称为超级速度(SS) USB具有更高的传输速率和显著快于USB 2.0标准。

支持的特性如下。

•主机模式由Linux操作系统标准XHCI驱动实现,支持并测试了超高速。

•“设备模式”只支持单个队列。支持大容量存储、以太、串行。

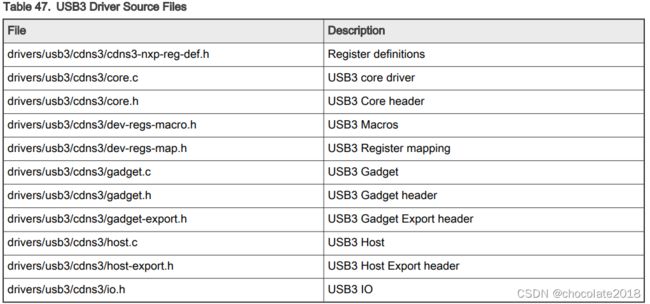

4.10.2源代码结构

4.11低功耗通用异步收发器(LPUART)

4.11.1介绍

低级UART驱动程序将Linux串行驱动程序API接口到所有UART端口。

它具有以下特点:

•中断驱动和eDMA驱动的字符发送/接收

•标准Linux波特率高达4Mbps

•发送和接收7位,8位,9位或10位字符长度的字符

•传输一个或两个停止位

•支持TIOCMGET IOCTL读取调制解调器控制线路。只支持常量TIOCM_CTS和TIOCM_CAR,加上TIOCM_RI仅在DTE模式

•支持TIOCMSET IOCTL设置调制解调器控制线。只支持常量TIOCM_RTS和TIOCM_DTR

•奇偶校验

•XON/XOFF软件流量控制。当通信速度不太高且缓冲区溢出的概率很小时,使用软件流控制的串行通信是可靠的

•CTS/RTS硬件流控制——包括中断驱动的软件控制的硬件流和硬件驱动的硬件控制流

•通过标准的Linux串行API发送和接收中断字符

•识别帧和奇偶校验错误

•能够忽略字符断开,奇偶校验和帧错误

通过TIOCGSSERIAL和TIOCSSERIAL TTY IOCTL获取和设置UART端口信息。一些程序,如setserial和dip使用这个功能,以确保波特率设置正确,并获得设备的一般信息。UART类型应该设置为在serial_core.h头文件中定义的52。

•通过暂停和恢复UART端口的电源管理功能

•标准TTY层IOCTL调用

从设备文件/dev/ttyLP0到/dev/ ttyLP1,可以访问所有UART端口

4.11.2硬件操作

要确定设备上可用的UART模块的数量,请参阅与SoC相关的应用程序处理器参考手册。

每个UART硬件端口都能够进行标准的RS-232串行通信。

每个UART包含一个64字节的发射器FIFO和一个32半字的深度接收器FIFO。当每个FIFO中的数据级别达到程序设定的阈值级别以及调制解调器信号中的状态发生变化时,每个UART还支持各种各样的可屏蔽中断。

4.11.3软件操作

Linux操作系统包含一个核心UART驱动程序,它管理各种平台的UART驱动程序中常见的许多串行操作。

低级UART驱动程序负责向核心UART驱动程序提供诸如UART端口信息和一组控制功能等信息。这些功能是作为Linux操作系统和UART硬件之间的低级接口实现的。

它们不能从其他驱动程序或用户应用程序调用。用于控制硬件的控制函数通过一个名为uart_ops的结构传递给核心驱动程序,端口信息通过一个名为uart_port的结构传递。

低级驱动程序还负责处理UART端口的各种中断,并在必要时提供控制台支持。

通过在DTS文件中启用DMA通道,可以将每个UART配置为使用DMA进行数据传输。

驱动程序为需要DMA传输的uart请求两个DMA通道。在接收事务中,驱动程序将数据从DMA接收缓冲区复制到TTY翻转缓冲区。

当使用DMA进行传输时,驱动程序将数据从UART传输缓冲区复制到DMA传输缓冲区,并将这个缓冲区发送给DMA系统。有关更多信息,请参阅内核源代码树中关于串行驱动程序的Linux文档。

4.11.4驱动特性

UART驱动程序支持以下特性:

•波特率高达4Mbps

•仅在中断驱动模式下识别帧和奇偶校验错误;在DMA驱动模式下不能识别这些错误

•发送、接收并适当处理换行字符

•识别调制解调器控制信号

•如果请求忽略帧、奇偶校验和break错误的字符

•实现对硬件流控制的支持

•获取和设置UART端口信息;在硬件驱动的硬件流量控制模式中,某些流量控制计数信息不可用

•电源管理

•中断驱动和dma驱动数据传输

4.11.5源代码结构

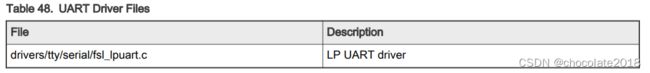

下表显示了UART驱动程序源文件。

对于i.MX 8, i.MX 8X和i.MX 8M的配置选项在位于arch/arm64/boot/dts目录下的设备树中指定。

4.11.6菜单配置选项

UART驱动程序在默认情况下是启用的。

菜单配置选项位于:

Device Drivers > Character devices > Serial drivers > Freescale LPUART serial port support [*] Console on Freescale LPUART serial port

4.11.7编程接口

UART驱动程序实现了Linux串行API与UART端口连接所需的所有方法,并为Linux核心UART驱动程序提供了一组控制方法。有关驱动程序中实现的方法的更多信息,请参见API文档。

4.11.8中断需求

UART驱动程序接口只生成一个中断。

该状态用于确定发生了哪种中断,如RX或TX。