- 「RIA学习力」《第五项修炼》No.06,央央

快乐幸福的央央

今天的内容来自《第5章心灵的转变》正负反馈和延迟系统思考的积木块有两种不同类型的反馈过程:正反馈和负反馈。正反馈(或放大反馈)过程是增长的引擎。只要你处在增长的局面,一定就有正反馈作用。正反馈过程也可以产生加速的衰减,很小的衰减被放大成越来越严重的衰减,就像金融恐慌时银行财产的衰减情况一样。负反馈(稳定反馈)起作用时,就有以目标为导向的表现。如果目标是稳定不动,那么负反馈的作用就像车上的刹车装置。

- 2021年10月15日晚上学习分享

杜娟A

尊敬的老师,同学们大家晚上好!我叫杜娟,是河南龙华牧业有限公司的一位高管,我们从事的是肉种鸡养殖业。今天我分享的主题是“我是如何合理安排我的学习时间的”?我是2018年10月中旬在庹燕的引领下,有幸加入东方书院,在书院学习一年,感觉自己的写作能力提高了,处理问题的方法也比原来多了,脾气变得也柔软了,家庭也更加幸福了,但是后来由于种种原因中断一年多,我深感后悔和愧疚。学习中断后我就越来越感觉得自己的

- java毕业设计-基于Javaweb的家常小菜烹饪学习管理系统的设计与实现(源码+LW+部署文档+全bao+远程调试+代码讲解等)

程序猿刘

vuespringboot毕业设计java课程设计学习

博主介绍:✌️码农一枚,专注于大学生项目实战开发、讲解和毕业文撰写修改等。全栈领域优质创作者,博客之星、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java、小程序技术领域和毕业项目实战✌️技术范围::小程序、SpringBoot、SSM、JSP、Vue、PHP、Java、python、爬虫、数据可视化、大数据、物联网、机器学习等设计与开发。主要内容:免费开题报告、任务书、全bao定制+

- 若辰日记001

若辰读书

Hi你好呀你能看到这篇文,说明在图文打开率越来越低的今天,你还对我不离不弃,特别特别感谢你,隔空笔芯啦从今天开始,我会在公众号更新日记。为什么想写日记?给自己列几条理由:1、昨天参加线下学习,看到波波老师每天写日记,受到了极大的触动,有人说,哎呀那肯定是团队给他写的。其实你如果熟悉一个人,了解一个人,就会知道他的风格是怎样的,文字或许会说谎,风格不会。以前在HW工作,董事会经常发布老板讲话的文章,

- java毕业设计源码案例-基于ssm+协同过滤的个性化小说推荐系统设计与实现(源码+LW+部署文档+全bao+远程调试+代码讲解等)

项目帮

springbootjava计算机毕设java课程设计开发语言

博主介绍:✌️码农一枚,专注于大学生项目实战开发、讲解和毕业文撰写修改等。全栈领域优质创作者,博客之星、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java、小程序技术领域和毕业项目实战✌️技术范围::小程序、SpringBoot、SSM、JSP、Vue、PHP、Java、python、爬虫、数据可视化、大数据、物联网、机器学习等设计与开发。主要内容:免费功能设计,开题报告、任务书、全b

- AI 大模型重塑软件开发流程

万花丛中一抹绿

人工智能

一、AI大模型的定义与发展历史AI大模型是基于海量数据训练的深度学习模型,具备强大的自然语言理解、逻辑推理和知识生成能力。在软件开发领域,以GPT-4、CodeLlama、GitHubCopilotX为代表的大模型,能理解代码语法、语义及业务逻辑,实现代码生成、漏洞检测等复杂任务。其发展可追溯至2017年,谷歌提出Transformer架构,为大模型奠定了核心基础。2018年,GPT-1问世,参数

- 随笔:2021-11-21

磐孚菩提树下

回想自己加入的变现学院有一年了,从中自己多多少少也学到了许多的知识,但是也有自己不足的地方。没有做好自己的社群营销裂变,没有组建好自己的团队,也没有自己的社群组织。从中得到了:几个关系不错的朋友,学到了做社群的思路,也扩大了自己的知识的边界。计划从今天开始,把这个社群组织重新拾起来,继续开始自己的学习。

- 2023-3-21晨间日记 13724-HelenHan88

Helen穗穗

今天在昆明第二天起床:05:50就寝:22:00天气:晴朗心情:平静纪念日:春分春光浪漫时,醉却山河间任务清单昨日完成的任务,最重要的三件事:1、08:50的动车一路从广州抵达昆明站2、美美的逛了一晚上的夜市,悠闲惬意3、没洗澡就睡着了(^^)改进:提前沟通,能去更多的地方?习惯养成:心平气和周目标·完成进度10%名单罗列学习·信息·阅读早读~分享健康·饮食·锻炼徒步忘记打卡了人际·家人·朋友很快

- 机器学习中的数据预处理:从入门到实践

耐思nice~

机器学习由浅入深-吴恩达机器学习人工智能

在当今的智能时代,机器学习已经渗透到我们生活的方方面面。比如我们常用的推荐系统,它能根据我们的浏览记录精准推送喜欢的商品或视频,这背后就离不开机器学习的支撑。而一个优秀的机器学习模型,离不开高质量的数据,数据预处理正是保证数据质量的关键环节,它就像烹饪前的食材处理,直接影响着最终“菜品”的口感,也就是模型的性能。今天,我们就来全面学习机器学习中数据预处理的关键步骤。一、数据预处理的重要性数据预处理

- 鸿蒙开发进阶(HarmonyOS )短距离通信的BLE蓝牙扫描实践案例

你我皆是牛马星人

OpenHarmony鸿蒙开发HarmonyOS1024程序员节华为harmonyos鸿蒙android前端ui

鸿蒙NEXT开发实战往期必看文章:一分钟了解”纯血版!鸿蒙HarmonyOSNext应用开发!“非常详细的”鸿蒙HarmonyOSNext应用开发学习路线!(从零基础入门到精通)HarmonyOSNEXT应用开发案例实践总结合(持续更新......)HarmonyOSNEXT应用开发性能优化实践总结(持续更新......)场景描述蓝牙是一种短距的无线通讯技术,可实现固定设备、移动设备之间的数据交换

- 【静静日记】第391篇:学时间管理,成为人生赢家Day1

静靖的故事

7月5日郑州晴好书《高能要事》一起读!“高能要事”是时间管理的核心!时间管理能力,是不断精进的过程,从今天开始重新学习叶武滨老师时间管理九段,过线上人生!如何如何实现高能?就是每个人每一天都要利用最优质的时间空间和最旺盛的精力,去选择并首先完成对人生有积极影响的事情,如此就可以创造你想要的人生,实现16倍的效能跃升。生活中的三类人,你中枪了吗?第一类,忙死。忙死的人,白天过不好,晚上睡不好,生活一

- 计算机专业大数据毕业设计-基于 Spark 的音乐数据分析项目(源码+LW+部署文档+全bao+远程调试+代码讲解等)

程序猿八哥

数据可视化计算机毕设spark大数据课程设计spark

博主介绍:✌️码农一枚,专注于大学生项目实战开发、讲解和毕业文撰写修改等。全栈领域优质创作者,博客之星、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java、小程序技术领域和毕业项目实战✌️技术范围::小程序、SpringBoot、SSM、JSP、Vue、PHP、Java、python、爬虫、数据可视化、大数据、物联网、机器学习等设计与开发。主要内容:免费功能设计,开题报告、任务书、全b

- 我的暑假见闻分享记

甯甯的花儿

同学们:两个月的暑假,说快不快,说慢也不慢,这两个月的时间里,你们的收获有哪些呢?我先来跟大家说一说,我的暑假见闻吧!众所周知,在期末考试前两天,我被学校临危受命,去参加县里的新课标考试,学校在两百多位教师中,派出语文数学老师各3人,英语一人,一共是七个人参加考试。大家都知道,为了让我们全心备考,我是连监考改卷都没参加,你们放假了,我依然还要来学校学习,最艰难的时候,背了忘忘了背,精神压力特别大,

- 2019.6.8

crescent_新月

鲇鱼效应充分体现了竞争的重要性。竞争对于人的发展和社会的进步都有促进作用。它给我们以直接现实的追求目标,赋予我们压力和动力,能最大限度地激发我们的潜能,提高我们的学习和工作效率,使我们在竞争、比较中客观地评价自己,发现自己的局限性,提高自己的水平。

- DAY4精时力学习日志-【体力】冥想让你更健康更年轻

波斯菊

【精时力学习日志】本训练营:2021年100天精时力营·除法今日主题:1-4【体力】冥想让你更健康更年轻学习日期:2021年12月9日1、[我记]我学(客观)+我思(主观)+正反栗子+行动:1.1睡眠限制疗法&睡眠时间计划法1.1.1[我记]睡眠限制疗法的关键点在于不困就不上床睡觉,睡眠时间计划法的关键点在于推迟就寝时间以提升睡眠质量。1.1.2[我思]检视:这个知识点和我之前的认知是一致的吗?回

- Shell 脚本编程全面学习指南

前言Shell脚本编程是Linux和Unix系统管理、自动化任务的核心工具之一。通过Shell脚本,你可以自动化重复性操作、简化复杂流程、提高系统管理效率,甚至构建完整的自动化运维工具。本文将带你从基础到进阶,全面学习Shell脚本编程,涵盖语法、结构、调试、最佳实践等内容。一、Shell简介与环境搭建1.1什么是Shell?Shell是命令行解释器,是用户与操作系统内核之间的桥梁。它接收用户输入

- Protein FID:AI蛋白质结构生成模型评估新指标

一、引言:蛋白质生成模型面临的评估挑战近年来,AI驱动的蛋白质结构生成模型取得了令人瞩目的进展,但如何有效评估这些模型的质量却一直是一个悬而未决的问题。虽然实验验证仍然是金标准,但计算机模拟评估对于快速开发和比较机器学习模型至关重要。然而,尽管最先进的模型在当前评估指标上表现卓越,但它们在实际设计应用中的成功率仍然相对有限。例如,有研究报告显示生成结构的实验成功率仅为3%,而计算机模拟评分却远高于

- 日精进第140天

妈咪宝贝贵族天使莹莹

敬爱的李老师,智慧的班主任,亲爱的跃友们:大家好!我是东平纽约纽约王莹莹今天是我的日精进行动第141天,给大家分享我今天的进步,我们互相勉励,携手前行,每天进步一点点,距离成功便1.比学习:长大成人,绝不是不要依赖他人,一个人活下去,所谓的自立就是同他人,同随着岁月变得不同以往的他人构建起让自己心情舒畅的人际关系。2、比改变:去引导,去争取,去改变。3、比付出:别让自己永远陷入被动的等待,等待他人

- 【中艺平台】唐浩铭【全球艺术家编码6633】作品雅赏(20201229)

大师之道

现为中学生的唐浩铭,从小具有很强的绘画天赋。他对色彩和线条有着异于常人的敏感,对大千世界专注于物象的特征与细节。他从小生活在南国的深圳,城市的环境,动物园的各种鸟兽鱼虫草木都是他描绘的对象。丰富的想象力是他创作的原动力。唐浩铭在观察到自然物的原形时,往往将自己的童真心灵相通,营造一个新的,抽象艺术图形,一个令人新喜的画面。在经过多年的专业学习后,培养起他对绘画的浓厚兴趣,绘画技巧有了很大的提升。他

- 英雄所见略同

石头在海上

今天有幸结识行业里最顶尖的一些人物,深表荣幸。被一群优秀的人包围的感觉真好。不断学习,精进,一直是我前行的动力。正所谓——物以类聚,人以群分。能够简单明了地阐述观点,推进项目,达成共识,共襄盛举。在他们身上,我能不断地吸收到更多的养分。相由心生,气韵非凡。有这样的Leader,实属三生有幸。长风破浪会有时,直挂云帆济沧海。

- 《翻转课堂与微课程教学法》学习心得 4组11号 孙娜

4组11号孙娜

读完《翻转课堂与微课程教学法》这本书让我对为何要进行翻转课堂,以及如何进行有了一些了解,教学观念和思想有了一种新的认识。对翻转课堂和微课程早有耳闻,也或多或少地在网络上进行过一些查阅,但都是一些零碎的、浅尝辄止的了解,现在静下心来读这本系统的著作,使我对翻转课堂和微课程有了更清晰的认识。这本书共分为上、下两部分,上篇主要是翻转课堂的相关理论和目前翻转课堂进行的一些案例,后半部主要介绍如何实施翻转课

- 在 Conda 中删除环境及所有安装的库

Studying 开龙wu

conda

注意事项1.删除环境前确保你没有在该环境中运行任何程序。2.删除操作是不可逆的,所有该环境中的包和配置都会被永久删除。3.如果你想保留环境的配置信息,可以在删除前使用condaenvexport>environment.yml导出环境配置。关于requirements.txt和environment.yaml文件使用介绍详情可参考以往文章,争对机器学习和深度学习里Python项目开发管理项目依赖的

- ZooKeeper学习专栏(三):ACL权限控制与Zab协议核心原理

文章目录前言一、ACL访问控制列表二、原子广播协议(Zab协议)总结前言在分布式系统中,安全访问控制和一致性保证是两大核心需求。本文将深入探讨Zookeeper的ACL权限控制机制和Zab协议的核心原理,帮助读者理解Zookeeper如何保障数据安全性和系统一致性。一、ACL访问控制列表ACL(AccessControlLists)是Zookeeper保护ZNode数据安全的关键机制,它定义了哪些

- 【学习分享】日精进打卡0042天~静静的教育成长路

静静的教育成长路

来源:好友时长:60分钟“纸上得来终觉浅,绝知此事要躬行”。记得之前分享过这么一句话:任何知识都要转化为一种解决问题的工具,今天,翻看好友的文章,深受启发。这篇文章说的是学生错题本的整理与使用,学生如果合理运用的话,一定能对学生的学习起到很大的帮助作用。这个对于不同年级的学生要求是不一样的。特别适用于高年级或自律的学生。低年级同学可以在家长的指导下使用,也是有好处的。错题本是学生的宝贵财富,孩子们

- nextjs学习笔记

ainuo5213

web前端框架学习nextreactreact服务端渲染next入门

由于本人最近在学习jocky老师的React16.8+Next.js+Koa2开发Github全栈项目关于react的服务端重构项目,然后跟着老师的视频做笔记,记录下自己的所学知识。目录结构pages(必需):pages目录是nextjs中最终要的一个目录,这个目录的每一个文件都会对应到每一个页面,可以根据地址栏的路由进行跳转。若pages下的js文件在一个目录下,那么nextjs默认会将这个

- 学习黄爱华老师有感

1e0826452ddb

黄爱华老师“小学数学精英教师四阶课程培养秋季课程在成都举办”,作为四川人的我非常荣幸能来参加。张文质老师的“学生在前,老师在后”,“教学从学生的身体出发,生活出发;”黄爱华老师的“大问题,大空间,大格局”大道至简的道理引发我的沉思和共鸣!黄老师行云流水的教学背后是他对教育的情怀与追求,是对数学的敏锐,是不懈的努力。反观自己的教育教学工作,需要努力的太多,通过学习也有深深感触。希望自己以后从基础做起

- 理解的证据---追求理解的教学设计9

卌行

达尔文,知道得少,但懂(理解)得多。这真是一句很有意思的话。首先,需要理解“理解得多”是什么意思?书中说我们经常将理解表述为“深入”的或“有深度的”,使之区别于浅层次的认知目标---知道。学习者必须在表面下挖掘,揭示不易发觉的核心观点。所有这些内涵强调的都是要透过表层,挖掘隐藏在内部的精华。我们无法通过灌输概念使其被理解;我们必须揭示它们的价值,事实上,这些概念正是探究和讨论的结果。从这段话的描述

- 预售工作一周小结

小西FineYoga梵音瑜伽

12-13号两天的培训,我清晰了解了梵音的整个发展历程;更清晰预售工作性质以及如何更好的做好预售工作;信息量之大,跨度广,我吸收并不多,希望多跟几次教授的培训,会有不一样的启发!教授是个非常有魅力的天生演讲者,风趣幽默,肢体语言表情丰富,特别有感染力。有着独到的眼光和超强的学习能力,他会从各行各业中取其精华去其糟粕,从每一期预售中不停的去总结,分析,判断,不停优化预售方案14号开始由李白店长带领我

- 什么是Java?想学习却不知道从哪开始?

不熬夜不是好程序员

谈起Java,相信有很多小伙伴们也跟我刚开始一样,对他的了解只有难,学成之后工资高,从入门学到入土,但当你真正开始系统的学习之后才发现其实哪些程序猿们也不过尔尔(刚学习完刚入职那种。。。)什么是Java?Java是一门编程语言,Java是一门掌握了技术就可以拿到高薪的工作岗位。Java这个语言在我国发展的很完善,相当于你掌握了Java技术出来,具备一定的开发经验,既可以在一线城市找到合适的岗位工作

- Unreal Engine开发:Unreal Engine基础入门_C++编程基础v1

chenlz2007

游戏开发虚幻c++javaunity游戏引擎交互lucene

C++编程基础在开始学习UnrealEngine之前,掌握C++编程基础是非常重要的。C++是一种强大的面向对象编程语言,广泛应用于游戏开发、系统软件开发等领域。本节将介绍C++的基本概念、语法和一些常用的功能,为后续的UnrealEngine开发打下坚实的基础。1.C++简介C++是一种静态类型的、编译式的、通用的、中级到高级的编程语言,它支持多种编程范式,包括面向对象编程、泛型编程和过程化编程

- sql统计相同项个数并按名次显示

朱辉辉33

javaoracle

现在有如下这样一个表:

A表

ID Name time

------------------------------

0001 aaa 2006-11-18

0002 ccc 2006-11-18

0003 eee 2006-11-18

0004 aaa 2006-11-18

0005 eee 2006-11-18

0004 aaa 2006-11-18

0002 ccc 20

- Android+Jquery Mobile学习系列-目录

白糖_

JQuery Mobile

最近在研究学习基于Android的移动应用开发,准备给家里人做一个应用程序用用。向公司手机移动团队咨询了下,觉得使用Android的WebView上手最快,因为WebView等于是一个内置浏览器,可以基于html页面开发,不用去学习Android自带的七七八八的控件。然后加上Jquery mobile的样式渲染和事件等,就能非常方便的做动态应用了。

从现在起,往后一段时间,我打算

- 如何给线程池命名

daysinsun

线程池

在系统运行后,在线程快照里总是看到线程池的名字为pool-xx,这样导致很不好定位,怎么给线程池一个有意义的名字呢。参照ThreadPoolExecutor类的ThreadFactory,自己实现ThreadFactory接口,重写newThread方法即可。参考代码如下:

public class Named

- IE 中"HTML Parsing Error:Unable to modify the parent container element before the

周凡杨

html解析errorreadyState

错误: IE 中"HTML Parsing Error:Unable to modify the parent container element before the child element is closed"

现象: 同事之间几个IE 测试情况下,有的报这个错,有的不报。经查询资料后,可归纳以下原因。

- java上传

g21121

java

我们在做web项目中通常会遇到上传文件的情况,用struts等框架的会直接用的自带的标签和组件,今天说的是利用servlet来完成上传。

我们这里利用到commons-fileupload组件,相关jar包可以取apache官网下载:http://commons.apache.org/

下面是servlet的代码:

//定义一个磁盘文件工厂

DiskFileItemFactory fact

- SpringMVC配置学习

510888780

springmvc

spring MVC配置详解

现在主流的Web MVC框架除了Struts这个主力 外,其次就是Spring MVC了,因此这也是作为一名程序员需要掌握的主流框架,框架选择多了,应对多变的需求和业务时,可实行的方案自然就多了。不过要想灵活运用Spring MVC来应对大多数的Web开发,就必须要掌握它的配置及原理。

一、Spring MVC环境搭建:(Spring 2.5.6 + Hi

- spring mvc-jfreeChart 柱图(1)

布衣凌宇

jfreechart

第一步:下载jfreeChart包,注意是jfreeChart文件lib目录下的,jcommon-1.0.23.jar和jfreechart-1.0.19.jar两个包即可;

第二步:配置web.xml;

web.xml代码如下

<servlet>

<servlet-name>jfreechart</servlet-nam

- 我的spring学习笔记13-容器扩展点之PropertyPlaceholderConfigurer

aijuans

Spring3

PropertyPlaceholderConfigurer是个bean工厂后置处理器的实现,也就是BeanFactoryPostProcessor接口的一个实现。关于BeanFactoryPostProcessor和BeanPostProcessor类似。我会在其他地方介绍。PropertyPlaceholderConfigurer可以将上下文(配置文件)中的属性值放在另一个单独的标准java P

- java 线程池使用 Runnable&Callable&Future

antlove

javathreadRunnablecallablefuture

1. 创建线程池

ExecutorService executorService = Executors.newCachedThreadPool();

2. 执行一次线程,调用Runnable接口实现

Future<?> future = executorService.submit(new DefaultRunnable());

System.out.prin

- XML语法元素结构的总结

百合不是茶

xml树结构

1.XML介绍1969年 gml (主要目的是要在不同的机器进行通信的数据规范)1985年 sgml standard generralized markup language1993年 html(www网)1998年 xml extensible markup language

- 改变eclipse编码格式

bijian1013

eclipse编码格式

1.改变整个工作空间的编码格式

改变整个工作空间的编码格式,这样以后新建的文件也是新设置的编码格式。

Eclipse->window->preferences->General->workspace-

- javascript中return的设计缺陷

bijian1013

JavaScriptAngularJS

代码1:

<script>

var gisService = (function(window)

{

return

{

name:function ()

{

alert(1);

}

};

})(this);

gisService.name();

&l

- 【持久化框架MyBatis3八】Spring集成MyBatis3

bit1129

Mybatis3

pom.xml配置

Maven的pom中主要包括:

MyBatis

MyBatis-Spring

Spring

MySQL-Connector-Java

Druid

applicationContext.xml配置

<?xml version="1.0" encoding="UTF-8"?>

&

- java web项目启动时自动加载自定义properties文件

bitray

javaWeb监听器相对路径

创建一个类

public class ContextInitListener implements ServletContextListener

使得该类成为一个监听器。用于监听整个容器生命周期的,主要是初始化和销毁的。

类创建后要在web.xml配置文件中增加一个简单的监听器配置,即刚才我们定义的类。

<listener>

<des

- 用nginx区分文件大小做出不同响应

ronin47

昨晚和前21v的同事聊天,说到我离职后一些技术上的更新。其中有个给某大客户(游戏下载类)的特殊需求设计,因为文件大小差距很大——估计是大版本和补丁的区别——又走的是同一个域名,而squid在响应比较大的文件时,尤其是初次下载的时候,性能比较差,所以拆成两组服务器,squid服务于较小的文件,通过pull方式从peer层获取,nginx服务于较大的文件,通过push方式由peer层分发同步。外部发布

- java-67-扑克牌的顺子.从扑克牌中随机抽5张牌,判断是不是一个顺子,即这5张牌是不是连续的.2-10为数字本身,A为1,J为11,Q为12,K为13,而大

bylijinnan

java

package com.ljn.base;

import java.util.Arrays;

import java.util.Random;

public class ContinuousPoker {

/**

* Q67 扑克牌的顺子 从扑克牌中随机抽5张牌,判断是不是一个顺子,即这5张牌是不是连续的。

* 2-10为数字本身,A为1,J为1

- 翟鸿燊老师语录

ccii

翟鸿燊

一、国学应用智慧TAT之亮剑精神A

1. 角色就是人格

就像你一回家的时候,你一进屋里面,你已经是儿子,是姑娘啦,给老爸老妈倒怀水吧,你还觉得你是老总呢?还拿派呢?就像今天一样,你们往这儿一坐,你们之间是什么,同学,是朋友。

还有下属最忌讳的就是领导向他询问情况的时候,什么我不知道,我不清楚,该你知道的你凭什么不知道

- [光速与宇宙]进行光速飞行的一些问题

comsci

问题

在人类整体进入宇宙时代,即将开展深空宇宙探索之前,我有几个猜想想告诉大家

仅仅是猜想。。。未经官方证实

1:要在宇宙中进行光速飞行,必须首先获得宇宙中的航行通行证,而这个航行通行证并不是我们平常认为的那种带钢印的证书,是什么呢? 下面我来告诉

- oracle undo解析

cwqcwqmax9

oracle

oracle undo解析2012-09-24 09:02:01 我来说两句 作者:虫师收藏 我要投稿

Undo是干嘛用的? &nb

- java中各种集合的详细介绍

dashuaifu

java集合

一,java中各种集合的关系图 Collection 接口的接口 对象的集合 ├ List 子接口 &n

- 卸载windows服务的方法

dcj3sjt126com

windowsservice

卸载Windows服务的方法

在Windows中,有一类程序称为服务,在操作系统内核加载完成后就开始加载。这里程序往往运行在操作系统的底层,因此资源占用比较大、执行效率比较高,比较有代表性的就是杀毒软件。但是一旦因为特殊原因不能正确卸载这些程序了,其加载在Windows内的服务就不容易删除了。即便是删除注册表中的相 应项目,虽然不启动了,但是系统中仍然存在此项服务,只是没有加载而已。如果安装其他

- Warning: The Copy Bundle Resources build phase contains this target's Info.plist

dcj3sjt126com

iosxcode

http://developer.apple.com/iphone/library/qa/qa2009/qa1649.html

Excerpt:

You are getting this warning because you probably added your Info.plist file to your Copy Bundle

- 2014之C++学习笔记(一)

Etwo

C++EtwoEtwoiterator迭代器

已经有很长一段时间没有写博客了,可能大家已经淡忘了Etwo这个人的存在,这一年多以来,本人从事了AS的相关开发工作,但最近一段时间,AS在天朝的没落,相信有很多码农也都清楚,现在的页游基本上达到饱和,手机上的游戏基本被unity3D与cocos占据,AS基本没有容身之处。so。。。最近我并不打算直接转型

- js跨越获取数据问题记录

haifengwuch

jsonpjsonAjax

js的跨越问题,普通的ajax无法获取服务器返回的值。

第一种解决方案,通过getson,后台配合方式,实现。

Java后台代码:

protected void doPost(HttpServletRequest req, HttpServletResponse resp)

throws ServletException, IOException {

String ca

- 蓝色jQuery导航条

ini

JavaScripthtmljqueryWebhtml5

效果体验:http://keleyi.com/keleyi/phtml/jqtexiao/39.htmHTML文件代码:

<!DOCTYPE html>

<html xmlns="http://www.w3.org/1999/xhtml">

<head>

<title>jQuery鼠标悬停上下滑动导航条 - 柯乐义<

- linux部署jdk,tomcat,mysql

kerryg

jdktomcatlinuxmysql

1、安装java环境jdk:

一般系统都会默认自带的JDK,但是不太好用,都会卸载了,然后重新安装。

1.1)、卸载:

(rpm -qa :查询已经安装哪些软件包;

rmp -q 软件包:查询指定包是否已

- DOMContentLoaded VS onload VS onreadystatechange

mutongwu

jqueryjs

1. DOMContentLoaded 在页面html、script、style加载完毕即可触发,无需等待所有资源(image/iframe)加载完毕。(IE9+)

2. onload是最早支持的事件,要求所有资源加载完毕触发。

3. onreadystatechange 开始在IE引入,后来其它浏览器也有一定的实现。涉及以下 document , applet, embed, fra

- sql批量插入数据

qifeifei

批量插入

hi,

自己在做工程的时候,遇到批量插入数据的数据修复场景。我的思路是在插入前准备一个临时表,临时表的整理就看当时的选择条件了,临时表就是要插入的数据集,最后再批量插入到数据库中。

WITH tempT AS (

SELECT

item_id AS combo_id,

item_id,

now() AS create_date

FROM

a

- log4j打印日志文件 如何实现相对路径到 项目工程下

thinkfreer

Weblog4j应用服务器日志

最近为了实现统计一个网站的访问量,记录用户的登录信息,以方便站长实时了解自己网站的访问情况,选择了Apache 的log4j,但是在选择相对路径那块 卡主了,X度了好多方法(其实大多都是一样的内用,还一个字都不差的),都没有能解决问题,无奈搞了2天终于解决了,与大家分享一下

需求:

用户登录该网站时,把用户的登录名,ip,时间。统计到一个txt文档里,以方便其他系统调用此txt。项目名

- linux下mysql-5.6.23.tar.gz安装与配置

笑我痴狂

mysqllinuxunix

1.卸载系统默认的mysql

[root@localhost ~]# rpm -qa | grep mysql

mysql-libs-5.1.66-2.el6_3.x86_64

mysql-devel-5.1.66-2.el6_3.x86_64

mysql-5.1.66-2.el6_3.x86_64

[root@localhost ~]# rpm -e mysql-libs-5.1

![]()

![]()

![]()

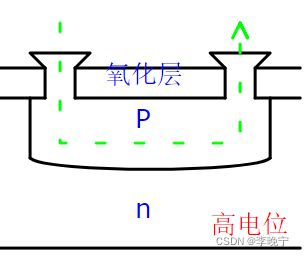

![]() 对阻值的影响,而厚度在工艺后也已经确定,所以,根据目标阻值,调整L和w。

对阻值的影响,而厚度在工艺后也已经确定,所以,根据目标阻值,调整L和w。 以npn双极集成电路为例,如果要将电阻做在p基区,在电流流过电阻时,要防止底部pn结击穿,就要在n外延区上加一个高电位

以npn双极集成电路为例,如果要将电阻做在p基区,在电流流过电阻时,要防止底部pn结击穿,就要在n外延区上加一个高电位![]() 。

。![]()