低功耗设计——基于UPF进行设计

UPF, 统一电源格式UPF(Unified Power Format)是新思(Synopsys)公司通用的电源格式,是一组标准的类Tcl 语言的集合,用来描述芯片设计中的低功耗意图(Low-Power Design Intent)。

使用UPF 的语言,可以描述供电电源网络,电源开关,隔离单元,保持寄存器单元等等和功耗设计相关的元素。这些语言可以在设计,分析,验证,实现这些流程中应用。在低功耗设计流程中加入UPF可以保证功耗意图在IC 设计流程中的一致性体现,这样的一致性可以让低功耗信息在仿真、逻辑一致性检查、设计验证环节更容易实现。

2007 年2 月,Synopsys 工具经过Accellera 的批准被设计成可以支持UPF 1.0标准。Accellera 是一个电子行业组织,致力于发展电子设计自动化标准并推广到整个电子行业中。这个组织的成员包括一大部分EDA 公司,其中有Magma Design Automation, Mentor Graphics 和Synopsys。这些公司相互合作来升级各家的工具支持UPF 标准。现在,Accellera 已经将UPF 的版权交给了IEEE P1801 工作组,这个工作组负责今后的UPF 标准扩展和完善以及将UPF 列入IEEE 标准的工作。

一、概述

UPF文件可以在设计早期引入对功耗的考虑。在RTL级设计中, 可以把电源方案相关信息关联到代码中。下图展示了UPF对整个设计流程的支持。UPF提供了低功耗设计流程前后一致的功耗信息格式。

UPF 的运用贯穿低功耗电路始终,比如仿真验证、逻辑综合、物理实现、等价性验证和最终签核(SignOff)的过程都能使用。该流程相比于其他设计思路有如下优点:更加方便集中管理和实施各种低功耗方法;统一电源格式使设计整个过程更加高效,减少设计周期;提升电路的设计质量;减少低功耗设计风险,此流程已被行业内多家企业成功使用。

RTL 描述的是电路中的逻辑功能,而UPF 可以方便的描述RTL 不方便在电路中直接体现的电源信息,所以UPF 也是低功耗设计不可或缺的源文件,与RTL 文件一起被多种EDA 工具读入来实现设计者需要的电路功能。

综合阶段:读入RTL 文件和初始UPF 文件,产生门级网表及新的UPF 文件,新的UPF 文件与产生的门级网表对应,不仅包括初始UPF 信息,并且描述了在综合过程中插入的低功耗元器件(如电源开关单元等)之间的电源连接关系。

物理实现阶段:读入综合产生的网表和UPF,执行布局布线后,生成包含完整电源信息的网表和新的UPF。布局布线产生的UPF 包含初始UPF 所有信息,并且包含有布局布线时对低功耗设计调整的信息。

UPF 在流程上的等价性如RTL 一样可以通过等价性验证工具保证,比如用等价性验证工具读入RTL、UPF 和基于UPF 综合出的网表进行比较,然后读入基于UPF 综合出的网表和布局布线产生出的网表进行比对,由此来保证逻辑与功耗意图在整个流程中都是等价的。

二、UPF的概念

功耗意图(Power Intent)是指实现芯片低功耗设计所需要的思想和方法。UPF 语言提供了一种描述芯片功耗要求的方法,但是却没有精确的描述这些要求是如何实现的。UPF 语言描述了如何连接每一个设计单元的供电电源,供电网络的模型,以及电路的逻辑功能如何来支持动态电压切换等等,但却没有任何关于布局布线的描述。UPF 语言独立于RTL 语言,并且像RTL 语言一样都是设计的输入文件。

UPF 能表述出IC 电路低功耗设计的供电意图,比如描述电压域、电压域的供电端口、电压域的电压变换、电压域的供电电压、电压域之间怎样加入低功耗元件,以及定义电路的电源网络、电源线间的行为等等。下面举例说明如何用UPF 命令描述功耗意图。

1、对供电网络的描述

1)电压域

电路设计时为了更好的整体调配控制每个部分的电压,设计人员会给芯片划分不同的电源区域,每一个电源区域内的所有单元供电电压一致,每一个区域即为一个电压域。

默认情况下,同一个电压区域里所有的逻辑单元连接到相同的主要供电电源和地线上,其他次要的供电电源也可以定义在这个电压区域里。一般情况下,一个电压区域在芯片物理版图上被划做一个连续的区域(Voltage Area)。(但这并不是UPF 强制要求的)。

每一个电压区域都有一个边界(Scope)和范围(Extent)。边界表示在指定的电压区域在逻辑层次的深度。范围表示同属于一个电压域的逻辑单元的集合,他们共用相同的供电电源。所以定义边界可以明确电压域的逻辑所属关系,定义范围可以明确电压域的大小。

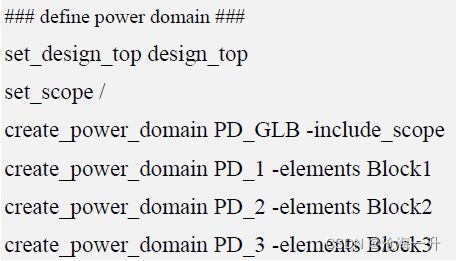

定义命令示例如下:

set_design_top用来指定该UPF文件所描述的顶层模块名为design_top。然后使用set_scope 这个命令来指定当前UPF 文件的命令对应在RTL 代码中的层次结构,如果没有写这条命令,则当前的UPF 文件的是对应于设计的最顶层。-create_power_domain 命令用来创建电压区域,-elements 用来表示设计层次结构中哪些部分是属于这个电压区域的。在一个UPF 文件中,一定要有一个电压区域作为顶层区域,使用-include_scope 来指定当前所有的在接下来未被指定的层次结构属于该顶层区域的电压区域。

2)供电端口与网络

每一个电压区域的边界上都每一个电压区域的边界上都必须定义供电端口(Supply Port)和供电网络(Supply Net)。供电网络是指贯穿于电压域中提供电源的“导线”,并且可以穿过多个电压域达到重用的效果。供电端口是指两个电压区域的供电电源连接点。供电网络从一级逻辑穿过供电端口到达另外一级逻辑。

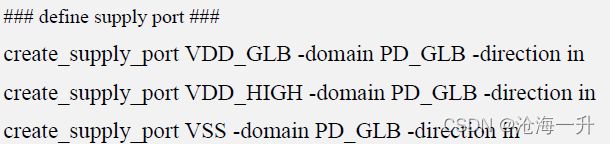

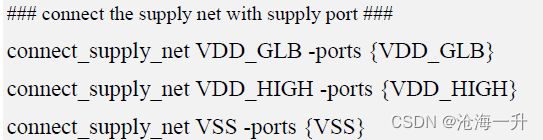

定义命令示例如下:

示例中create_supply_port 创建了一个电源端口,作用是和上一级电压区域进行连接,create_supply_net 在电压区域里创建了一组电源网络,-reuse 可以在指定的电压区域里创建一组与之前创建的名字相同的电源网络相连接的电源网络。connect_supply_net 把电源网络连接到电源端口上。

3)电源开关

电源开关(Power Switch)是用来连通或切断供电网络的器件。一个电源开关包括一个输入供电网络,一个可以被连通或切断的输出供电网络,和至少一个输入控制信号,还可以选择性的增加为多个输入控制信号以及输出一个或多个应答信号。

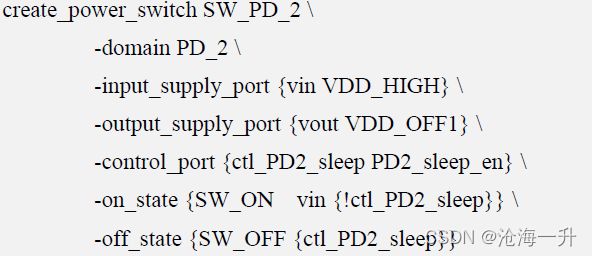

定义命令示例如下:

在做完之前的电源网络创建和连接工作后,接下来使用create_power_switch命令来建立和连接电源开关。示例中在电压域PD_2中插入电源开关SW_PD_2,此命令中详细的描述了该开关的电源输入网络为VDD_HIGH,电源输出网络为VDD_OFF1,即VDD_HIGH在经过了电源关断单元后变成了VDD_OFF1。控制信号为PD2_sleep_en,当控制信号为高电平的时候,电源开关关断。反之,控制信号为低电平时,VDD_OFF1与VDD_HIGH接通,电压域PD_2处于上电状态。

后面再用map_power_switch 命令把抽象的电源开关和单元库中的电源开关模型对应起来,这样后端工具在布局布线的时候就能正确的插入所需要的电源开关。

供电端口(Supply Ports)、供电连接线(Supply Net)、开关(Switches)组成了供电网络(Supply Network),供电连接线连接到供电端口给电压域供电,电源关断与否由开关操控。

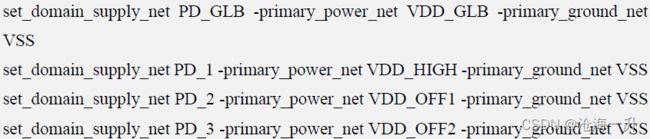

使用set_domain_supply_net 命令就把指定电压区域里的所有单元默认连接到主要的供电电源和地上,这样一来,电压区域内基本的电源网络结构已经构建好了 。

2、对电源状态表的描述

在之前的功耗意图设计完毕之后,还需要再描述一个电压状态表(Power State Table),其内容是定义了所有芯片在工作的时候各个电压区域合理的电压状态。电压状态包括了电压区域的开关和电源端口上的电压值。其主要目的是确定功耗意图正确无误的实现在芯片设计中。根据电源状态表,EDA 工具能够判断出在各电压域之间是否需要插入特殊单元,如电平转换器等。

比如电压区域A 的输出经过了电压区域B 到达了电压区域C,如果电压区域B 是常开的,那么没有问题;但如果电压区域B 是可以关断的,而且在电压状态表里存在A,C 打开而B 关闭的状态,那么A 的输出在电压区域B 里如果需要插入缓冲器的话,则插入的必须是常开电源供电的缓冲器。定义好电压状态表之后,后端工具会根据这个状态表来对之前设计的功耗意图进行检查和综合。

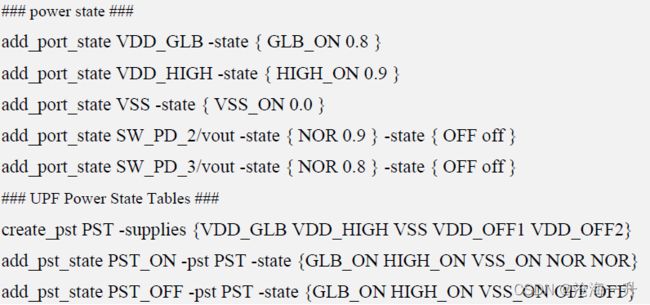

定义示例如下:

首先用命令add_port_state定义电源端口有哪些状态,然后再用creat_pst命令以一系列特定顺序的电源线来创建一个电源状态表。最后用add_pst_state命令来定义一组电源线状态组合。

3、其他

其他会用到的单元见

数字后端——低功耗单元库_沧海一升的博客-CSDN博客_数字后端工具为了实现例如门控时钟,多电源电压,多阈值电压,门控电源等低功耗技术,芯片设计的单元库必须有一些特殊的器件来支持完成这些低功耗技术的实现。https://blog.csdn.net/qq_21842097/article/details/122638582

1)隔离单元

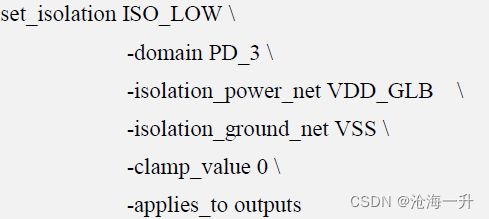

隔离单元定义示例如下:

上面的UPF 命令set_isolation 和set_isolation_control 都是用来定义隔离单元的策略,包括加在指定电压区域的输入还是输出,隔离单元的电源网络连接,隔离单元控制信号的电平是高有效还是低有效,隔离单元插入的位置是在电压区域的里面还是外面等。

一般来说,可以定义两组策略,一组是默认隔离到逻辑值“0”的一组,一组是隔离到逻辑值“1”的一组,这样定义的好处是可以避免漏掉未定义隔离单元的输入输出,而且读起来也很直观。

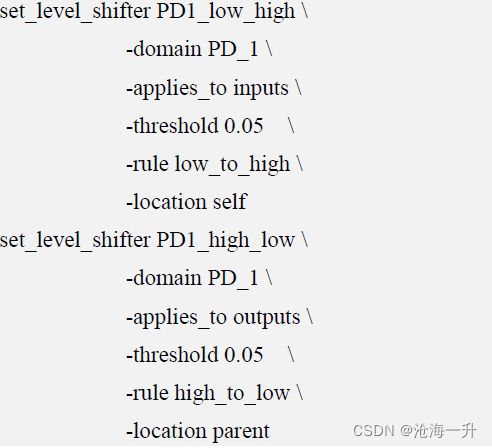

2)电压转换单元

对于level shifter,如果是只是插入普通的电压转换单元,就可以简单的使用UPF 的命令set_level_shifter 来描述插入电压转换单元的策略。这里需要的是带有隔离功能的电压转换单元也就是带有使能端的电压转换单元,在UPF 中应该既使用set_isolation 和set_isolation_control 来定义隔离单元策略,又需要使用set_level_shifter 来定义电压转换单元策略,后端工具会自动识别并在综合中插入带有使能端的电压转换单元。

通常电平转换单元应放置在目的电压域,定义示例如下:

“-threshold”选项用来定义当电压差超过了由其指定的大小时,才能插入电平转换单元。

3)保持寄存器

定义示例如下:

示例中把电压域PD_2内断电后需要保存数据的寄存器替换为保持寄存器,包括保持寄存器在save控制信号为高电平时保存数据,在restore控制信号为低电平时恢复数据,在电源关断时保持寄存器使用的电源是VDD_HIGH。

三、设计流程

基于UPF 的低功耗设计流程是从寄存器传输级(RTL)开始并加上一个独立的含有低功耗设计意图的UPF 文件。RTL 设计和UPF 设计分别存放在不同的文件中,这样可以让RTL 和UPF 的修改互相不受影响。下图所示为基于UPF 的低功耗设计流程。

在设计的每一个阶段,EDA 工具都需要UPF 的设计输入。其中用来做逻辑仿真,低功耗下的逻辑仿真和静态电源网络验证的工具分别为VCS,MVSIM和MVRC。逻辑综合工具Design Compiler 和物理版图实现工具IC Compiler 负责后端实现工作。使用Formality 进行RTL 与UPF 的等价性验证。PrimeTime,PrimeTimePX,PrimeRail 这些工具可以用来分析整体设计的时序约束要求和功耗大小。

综合工具Design Compiler 读入RTL 代码和初始的UPF 文件,在综合后产生网表和与其对应的UPF’。新产生的UPF’既包含了原始UPF 的信息,同时也包含了综合时Design Compiler 插入的特殊单元(如隔离单元,电压转换单元等)的电源连接关系。

物理实现工具IC Compiler 读入综合后的网表和UPF’文件,来进行布局布线操作,从而得到具有完整电源网络的门级网表和UPF’’。UPF’’包含了UPF’中的所有信息,并且加入了布局布线时UPF 的低功耗设计的意图(比如插入电源开关等)。

RTL 或综合后网表与对应的UPF 可以通过仿真工具,等价性验证工具和时序分析工具来进行验证和分析。例如等价性验证工具Formality 可以通过读入RTL与UPF,综合后网表与UPF’来比较RTL 代码和综合后网表的逻辑功能与低功耗设计意图的等价性。

VCS 仿真器和MVSIM 多电压域仿真工具可以用来在不同的设计阶段(综合前RTL,综合后加入电源网络相关单元门级网表,布局布线后加入电源开关的门级网表)进行带有电源信息的功能逻辑仿真。在每一个设计阶段,都可以用这种带有电源信息的仿真来检查电源电压的变化对设计的影响,精确的定位出低功耗设计的问题所在。MVRC 可以根据UPF 的描述来对电源网络的连接性,结构及功耗意图的一致性进行检查。

PrimeTime 读入Design Compiler 或IC Compiler 生成的门级网表和对应生成的UPF 文件,用来进行的时序分析。PrimeTime 使用UPF 的电源信息来构造一个虚拟的电源网络模型,并且将电压值标注在每一个实例化门单元的电源地引脚上。PrimeTime 只是进行时序分析,不会对电源网络结构进行任何结构或者功能的修改,所以PrimeTime 不会生成任何修改的UPF 文件。

1、基于UPF的逻辑综合

相比于一般的逻辑综合,基于UPF的逻辑综合需要增加以下步骤:读入UPF文件、对不同的电压域设定不同的电压、检查UPF对多电压设计的描述是否正确等。

首先需要在target_library里添加在低功耗设计时需要用到的库,库中包含隔离器、电平转换器、电源开关等特殊单元,且这个库应添加在标准单元库的后面。

在DC综合脚本里的主要步骤如下:

1) 设置相关变量;

2) 读入设计及相关约束;

3) 用load_upf命令读入UPF文件

4) 用命令set_voltage设定各电源线的工作电压。工具会根据各电源线给定的工作电压,自动选择相应的工作环境对RTL进行综合。如下,设置VDD_HIGH、VDD_OFF1的工作电压为0.9V,VDD_GLB、VDD_OFF的工作电压为0.8V,VSS的工作电压为0V。

5) 用check_mv_design命令检查UPF对多电压设计的描述是否正确;

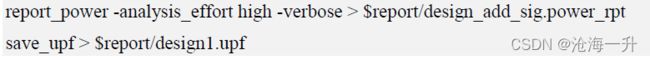

6) 生成功耗报告,保存Design Compiler综合后生成的UPF文件以供布局布线工具使用。

然后最后用工具PrimeTime读入综合之后生成的门级网表和UPF文件UPF’进行了带电源信息的时序检查,保证时序满足要求。

2、低功耗设计下的功能仿真

Synopsys公司有一款基于UPF的低功耗动态验证工具MVSIM。它可以与目前主流的功能仿真器比如Modelsim,VCS协同仿真。设计者可以在RTL设计阶段结合UPF文件来验证低功耗设计的正确性,检查UPF文件所描述的低功耗设计意图是否正确,这样能够在设计初期发现问题,大幅度地降低设计的成本和风险。随着低功耗设计复杂度的提高,设计者们对低功耗设计的仿真验证技术提出了越来越高的要求,Synopsys公司为了提高低功耗仿真验证的速度,把MVSIM工具的低功耗引擎整合到了VCS仿真器里面,所以叫MVSIM-Native Mode。

如图所示为MVSIM-Native Mode仿真流程,与一般的VCS仿真相比,工具是通过在编译时增加一个选项“-upf upf_file_name”来读入UPF文件的,这样工具就可以做带有电源信息的逻辑功能仿真了。

在设计中做Power Aware Simulation的简单步骤如下所示:

1) 在VCS编译时增加-upf选项读入UPF文件,增加-power_top选项

2) 在测试平台里添加语句给电源上电

3) 主要针对于门控电源技术,在测试平台里添加一些功耗控制语句,检查控制信号(如电源开关单元、隔离单元、保持寄存器的save和restore信号)变化后,电路是否按照设计要求正确的工作。

4) 运行过程与一般的VCS仿真相同。