FPGA面试题目笔记(二)——同步异步D触发器、静动态时序分析、分频设计、Retiming

文章目录

- 1、行为级与RTL级的区别

-

- 1.1 RTL级(可综合成门级电路)

- 1.2 行为级

- 2、关于LUT

-

- 2.1 LUT是什么

- 2.2 N维查找表

- 2.3 FPGA中的LUT

- 3、`include和条件编译

- 4、写异步D触发器(扬智电子笔试)

-

- 4.1 八位同步D触发器

- 4.2 具有异步清零,同步复位信号功能的D触发器

- 5、静态、动态时序分析的优缺点(威盛VIA 2003.11.06 上海笔试试题)

- 6、采用二选一多路器 mux2和inv非门实现异或操作(飞利浦-大唐笔试)

- 7、寄存器和锁存器的区别,为什么多用寄存器,行为级描述中锁存器如何产生

- 8、 D触发器实现2分频的Verilog描述 (汉王笔试)

- 9、D触发器实现带同步高置数和异步高复位端的二分频的电路

- 10、设计一个可预置初值的7进制循环计数器

- 11、高阻态

- 12、对Retiming技术的理解

FPGA基础知识的总结

1、行为级与RTL级的区别

数字系统设计的过程:

算法——行为级描述——RTL级描述——门级网表——物理版图

1.1 RTL级(可综合成门级电路)

- RTL级又称为寄存器级,是指用寄存器来描述电路数据流的方式,用硬件描述语言(verilog)描述,语句必须是可综合的(能生成各种门电路)。

- 寄存器和组合逻辑来组成RTL级。在RTL级下,需要描述各级寄存器(寄存器),还要描述各级寄存器之间的信号的转换关系(组合逻辑)

- 需要掌握如何采用RTL级对流水线原理图进行描述,同时还要知道哪里需要使用组合逻辑,哪里需要用寄存器,并且该如何实现。

1.2 行为级

- 行为级一般基于算法,仅用来描述电路的功能,最终目的是得到输入和输出之间的关系,采用任何verilog语法描述都可以,因为不用考虑可综合的问题。

- 行为级描述下,一般采用直接赋值的方式,需要运用大量的算术运算、延迟、initial块等不可综合语句,因此常用于验证仿真中。

题目:Verilog语言的层次高低对应(D)

A.系统级,行为级,功能级,寄存器传输级,门级

B.系统级,行为级,寄存器传输级,功能级,门级

C.系统级,功能级,寄存器传输级,行为级,门级

D.系统级,功能级,行为级,寄存器传输级,门级

二者区别的详细讲解

2、关于LUT

2.1 LUT是什么

LUT为查找表,顾名思义,其根本的作用也是查找(好比我们在字典中查找我们想要的字)。本质:给定一个输入的值,返回给一个对应的输出值。

2.2 N维查找表

查找表包括一维(1D LUT)、二维查找表等。

- (1D LUT)一维查找表是在一维空间中,给定一个输入变量,得到一个对应的输出变量。如下所示,给输入0,得到输出0,给输入1,得到输出0.5……

- (2D LUT)二维查找表是在二维空间中,输入输入两个不相关的变量,会得到相应的输出。比方说,我们的输入一组坐标(x, y),可得到该坐标对应的值。

- 同理,3D LUT 就是三维查找表,输入三个不相关的变量,得到一个输出值。可在色彩空间中应用,比如给予一组RGB的数值,通过查找表查找后,得到一组新的RGB数值,从而实现了颜色的变化。

2.3 FPGA中的LUT

FPGA查找表的本质就是一个RAM,每一个LUT可看作一个有4位地址线的16*1RAM。一般情况下我们采用LUT4或者LUT6,因为如果查找表的输入位数过大的话,需要进行级联操作,会造成更大的数据传输延迟;

在FPGA中,可使用LUT来实现组合逻辑电路的功能,形成门电路。LUT里存储的数据是真值表,根据逻辑计算后的结果,即可在LUT中查找对应内容。

- 如下我们实现了二输入查找表,通过两个不相关的输入,根据逻辑功能得到对应的输出,这里的逻辑功能就是查找表,因此查找表也相当于逻辑门的真值表。

module test(

input a,

input b,

output out1,

output out2

);

assign out1 = a & b;

assign out2 = a | b;

endmodule

可看出我们采用LUT实现了门电路,LUT内就是逻辑门电路的真值表。

根据LUT是ROM且内部存储数据是真值表的本质,对于LUT1,我们即可通过输入变量00,输出LUT1中地址为00存储单元中的数值0……

- 如何看一个设计中含有几个查找表?

3.2.2 详解

LUT前生今世

FPGA中LUT详解

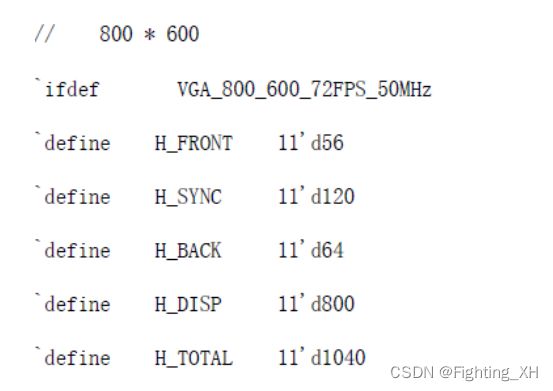

3、`include和条件编译

我们用`include来进行文件的包含,和C语言类似,该文件中定义一些公共的宏参数。一个include只能对一个头文件进行包含。

- 条件编译:当满足条件时对一组语句进行编译,当条件不满足时则对另外一组语句进行编译。

- `define作为条件编译的标志,定义了哪一段哪一段即可编译,否则不编译。

- `ifdef 可出现在设计的任何地方;

`ifdef 宏名(标识符)

程序段1

`else

程序段2

`endif

-

在FPGA图像处理中,VGA驱动设计处会用到这种条件编译的方式,用来选择不同VGA分辨率中对应的显示前沿、行有效等宏参数,如下是定义的800*600分辨率的VGA时序参数。我们通过包含头文件(建议包含头文件和该文件在同一文件夹下)以及用`define的方式来选择对应的分辨率即可。

-

`define VGA_800_600……表示这800*600分辨率的一部分代码被编译。

详解

4、写异步D触发器(扬智电子笔试)

关于D触发器:

D触发器通常在时钟上升沿时,此时会捕获D端输入的值,然后保持该值不变,直到下一个上升沿到来时,重新捕获D端的输入值。因此它具有存储记忆功能。

注意:D触发器的正常工作必须要满足其保持和建立时间要求。如果数据稳定的时候不满足要求,也是不能正常存储的。

//一位 异步D触发器

module test(clk,rst,d,q);

input clk;

input rst;

input d;

output reg q;

always@(posedge clk or negedge rst)

if(!rst)

q <= 0;

else

q <= d;

endmodule

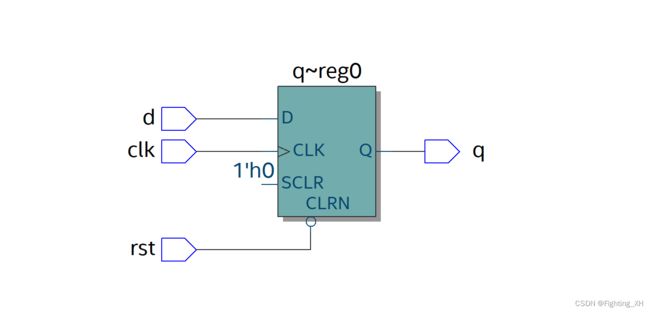

4.1 八位同步D触发器

module test(clk,rst,d,q);

input clk;

input rst;

input [7:0]d;

output reg [7:0]q;

always@(posedge clk )

if(!rst)

q <= 0;

else

q <= d;

endmodule

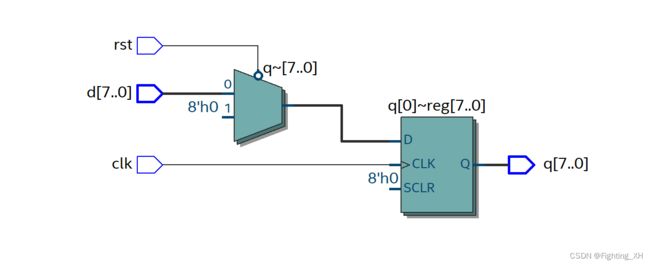

RTL图:

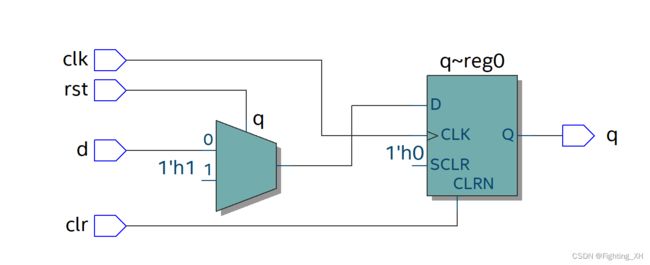

4.2 具有异步清零,同步复位信号功能的D触发器

module test(clk,rst,clr,q,d);

input clk ;

input rst ;

input clr;

input d ;

output reg q ;

always @ (posedge clk or posedge clr )

if(clr)

q <= 0;

else if(rst)

q <= 1;

else

q <= d;

endmodule

这里相当于有了优先级,清零信号clr优先于复位rst信号。

优先的理解:当clr清零的时候,不管rst信号为高电平还是低电平都不会影响q为0的结果。

5、静态、动态时序分析的优缺点(威盛VIA 2003.11.06 上海笔试试题)

1、动态时序分析:是通常我们所说的仿真,该仿真可以验证功能和时序。方法:首先确定测试向量,输入硬件模型,进行仿真。

优点:比较精确,同静态时序相比,它适用于更多的设计类型 。

缺点:若遇到门级等,分析速度慢;其次它需要使用输入矢量,这使得它在分析的过程中有可能会遗漏一些关键路径,难以保证足够的覆盖率;随着规模增大,所需要的向量数量以指数增长。

2、静态时序分析:只能分析时序,不能功能验证。

优点:不需要输入测试向量,比动态时序分析快得多,提高仿真时间。采用穷尽分析的方法,可验证每一条路径(100%覆盖),分析路径上的传播延时,比如组合逻辑延时、走线延时等,检查信号建立时间和保持时间是否满足时序要求。通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。运行速度很快、占用内存较少。可利用时序分析结果进行时序优化。

缺点:静态时序分析只能对同步电路分析,不能对异步电路时序分析。在深亚微米的工艺条件下,静态时序分析不能完整的把所有影响延时的因素给包含进去。

6、采用二选一多路器 mux2和inv非门实现异或操作(飞利浦-大唐笔试)

module test(sel,b,c);

input sel ;

input b ;

output c ;

assign c= sel ?(~b):(b);

endmodule

7、寄存器和锁存器的区别,为什么多用寄存器,行为级描述中锁存器如何产生

1、锁存器Latch :锁存器是电平触发方式,属于异步电路设计。————用于组合逻辑

缺点:不利于时序分析;对毛刺敏感;FPGA是没有锁存器单元的,它由查找表和触发器组成,因此会造成更多的资源浪费。

产生锁存器的几个情况:

1,case——缺少default的时候产生锁存器

2,if-------else if ——缺少else的时候产生锁存器

3,always@(敏感信号表)——赋值表达式右边参与赋值的信号没有在敏感列表出现会出现透明锁存器

2、寄存器Register:寄存器是时钟边沿触发方式,属于同步电路设计。

寄存器更利于时序分析,还能防止亚稳态等现象出现,FPGA里有寄存器单元,因此使用可节约芯片资源。

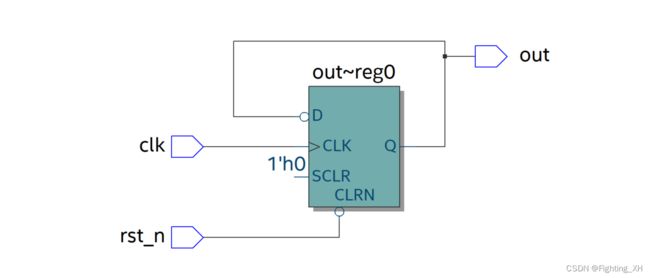

8、 D触发器实现2分频的Verilog描述 (汉王笔试)

关于分频设计及仿真的参考

verilog代码:

module test(clk,rst_n,out);

input clk ;

input rst_n ;

output reg out;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

out <= 0;

else

out <= ~out;

endmodule

`timescale 1ns/1ns

`define clock_period 20

module test_tb;

reg clk;

reg rst_n;

wire out;

test u1(

.clk(clk),

.rst_n(rst_n),

.out(out)

);

//产生时钟复位激励

initial clk = 1;

always #(`clock_period/2) clk =~clk;

initial begin

rst_n = 0;

#5;

rst_n = 1;

#100;

$stop;

end

endmodule

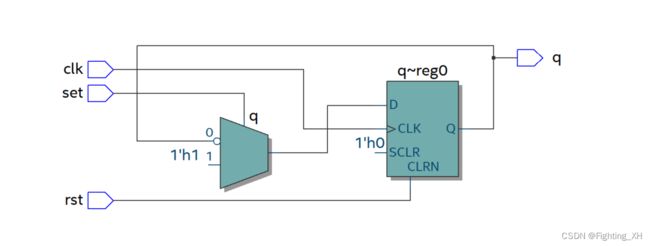

9、D触发器实现带同步高置数和异步高复位端的二分频的电路

需要关注两个点:同步高置数和异步高复位。

因此这里有置位和复位两个信号——set和rst

verilog代码如下:

module test(clk,rst,set,q);

input clk ;

input rst ;

input set ;

output reg q ;

always @ (posedge clk or posedge rst )

if(rst)

q <= 0;

else if(set)

q <= 1;

else

q <= ~q;

endmodule

10、设计一个可预置初值的7进制循环计数器

module test(clk,rst_n,load,data,cout);

input clk ;

input rst_n ;

input load ;

input [2:0] data ;

output reg [2:0] cout ;

always @ (posedge clk )

if(!rst_n)

cout <= 3'd0;

else if(load)

cout <= data;

else if(cout == 3'd6)

cout <= 3'd0;

else

cout <= cout + 3'd1;

endmodule

如果想要设计一个可预置初值的15进制循环计数器,修改位宽以及计数最大值即可。

参考

11、高阻态

高阻态是指电路的一种输出状态,和高低电平一样,但是它既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

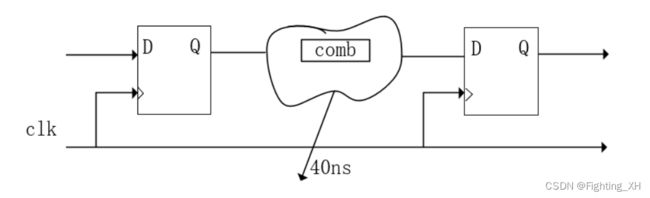

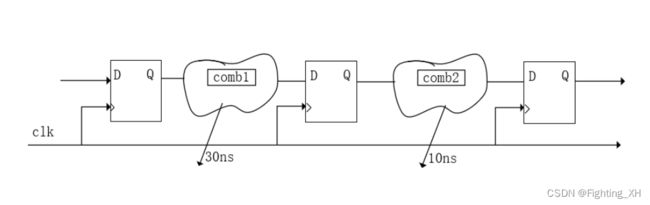

12、对Retiming技术的理解

重定时(Retiming)是一种时序优化技术,用在不影响电路输入/输出行为的情况下跨组合逻辑寄存器从而提高设计性能。

例如:当组合逻辑过大的时候,我们可采用流水线的方式用面积换取速度——插入寄存器