Xilinx IP核 之DDS

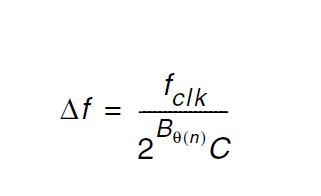

文章目录

- 0、背景

- 1、原理

-

- 1.1特性:

- 1.2结构

- 1.3 接口与时序说明

- 1.4 计算公式

- 1.4 IP配置选项

- 2、实际案例

-

- 2.1 overview

- 2.2、工程实战

- 2.3 工程福利

- 知识补充

-

- 1、什么叫SFDR

0、背景

关于这个本来是有专门的集成芯片DDS,但是那种通常用于产生雷达chirp信号,并且能够产生高频的模拟信号,这个FPGA里面的DDS通常用于混频处理,实现数字混频,其实和Intel的 NCO也类似,具体的我们一边来看看官方文档,一边来学习如何使用。采用平台,ISE14.7,另外IP核产生的DDS输出数字频率往往不够高,比不上专用的DDS芯片。

特此声明,请不要转载我的blog,否则不再推出新blog,并关闭所有文章!

1、原理

1.1特性:

DDS包括一个相位生成器和一个SIN/COS查找表,可以单独使用或组合使用。

通过相位抖动选项扩展了传统相位截断波形综合体系的谱线能量结构。

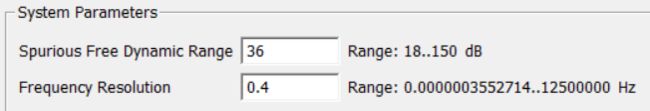

通过相位抖动或泰勒级数修正选项提高高动态范围的信号,同时最小化使用的FPGA资源,支持的无杂散动态范围(SFDR)为18~150dB。

支持1到16个独立的时分复用通道,支持数据位宽为3 ~26位的输出采样精度,采用二进制补码形式。

频率和相位偏移可以单独配置,值可以是常数、可编程的或动态的(用于调制)。

可选正弦或余弦的反输出。

SDFR和频率分辨率等系统参数及相位和输出数据位宽等硬件参数可以在定制IP核的图形用户界面上选择配置。

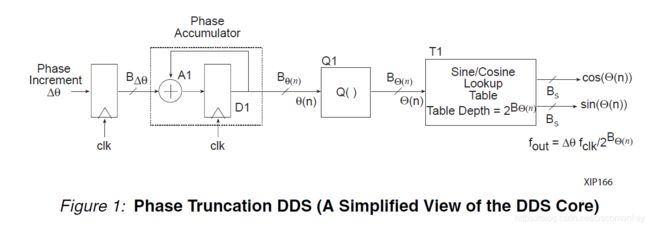

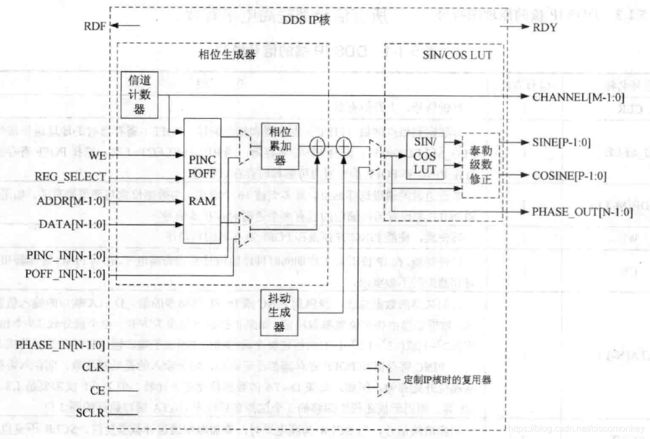

1.2结构

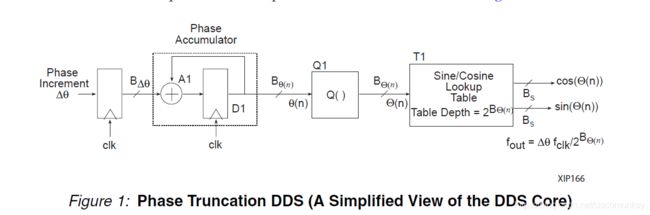

通过上图,我们可以知道D1与A1组成了积分器,生成相位,然后映射到sin的LUT表中,并且我们还可以看到这张表的深度。数字积分器用于产生合适的相位参量,然后通过查找表映射,得到输出波形

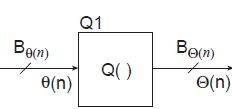

如上图所示,Q1是一个切片器,可以把高精度的相位切片至低精度的相位。量化器Q1的输入是高精度的相位,然后输出量化后精度较低的相位。然后该信号出现在查找表的地址端口,实现相位空间到时间的映射。

量化的目的是减小查找表的存储空间,其代价是降低了频谱纯度。相位抖动DDS。在相位截断DDS中,由于量化器Q1操作丢弃了高精度相位累加器结果的低位比特,从而引入相位误差。相位误差是周期性序列,误差造成的影响反应在频谱上就是出现非期望的谱线。可以通过加性随机信号来打破查找表地址误差的规律性。随机信号序列称为抖动,是一个方差近似等于相位累加器最低整数位的噪声序列,在高精度累加器输出送入Q1量化器之前加上抖动序列,实现相位抖动DDS。与截断DDS相比,相位抖动DDS相当于有12dB左右的附加无杂散动态范围。此外如果在FPGA中可以使用嵌入式乘法器或XtremeDSP实现DDS,则在实际应用中可以用高精度相位的小数部分来计算修正值,并加到查找表的值上,得到高SFDR输出。高阶泰勒级数要求计算正弦函数和余弦函数,对于每个正弦函数和余弦函数的计算都需要额外的乘法器和块RAM。

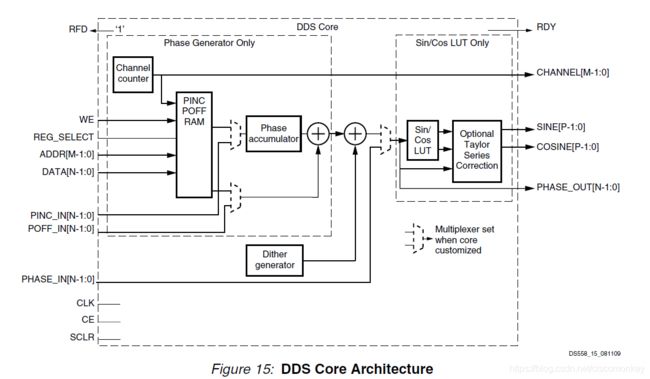

DDS IP核由两个主要部分组成:相位生成器和SIN/COS LUT。这两个部分可以独立地使用,也可以结合在一起使用。DDS IP核还支持十分复用多通道,各通道的相位增量和偏移参数可以独立配置。

相位生成器包括一个累加器和一个可选的加法器,提供与相位偏移的假发,定制核时相位增量和偏移可以分别配置为固定值、可编程或分别由输入端口输入。如果配置为可编程,需要制定地址信号用于在多通道应用时指定数据信号写入哪一个通道,寄存器选择信号指定写入的是相位增量还是相位偏移。如果设置为固定值,则在定制IP核时指定输出频率,而且在嵌入到设计工程后不能再进行调整。

如果IP核配置为相位生成器和SIN/COS LUT 组合使用可以实现相位截断DDS或泰勒级数修正DDS。如果在相位生成器和SIN/COS LUT之间增加一个抖动生成器,则可以实现相位抖动DDS。

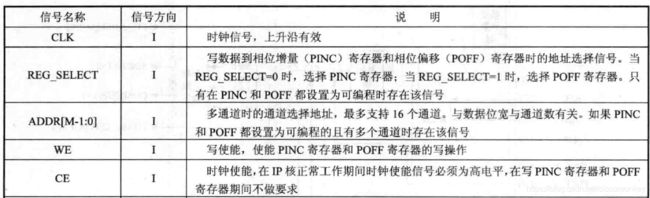

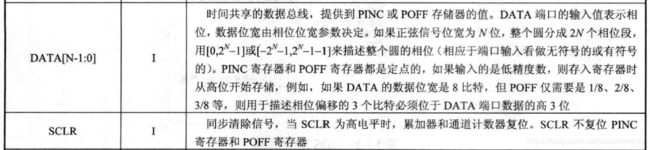

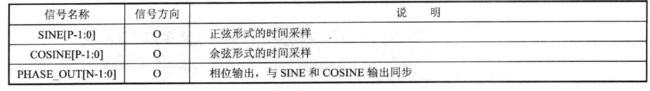

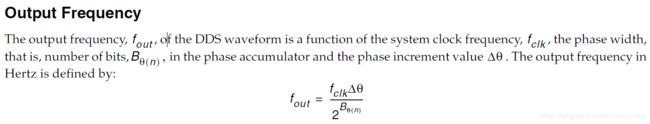

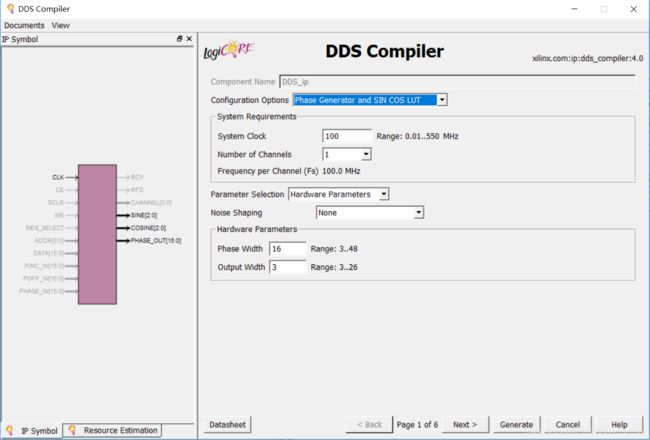

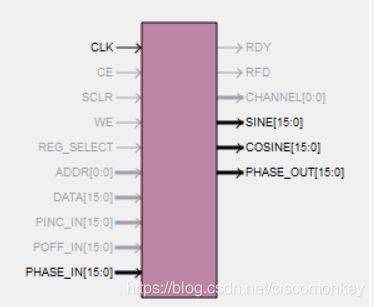

1.3 接口与时序说明

下面对DDS IP核的时序进行说明,我们通过时序说明再返回去看接口说明,这样效果更好。

核内PINC核POFF都用寄存器实现并提供可编程接口。

首先在DATA端口输入相位增量数据,通过将REG_SELECT设置为0来寻址PINC寄存器。当CE信号为高电平时在系统时钟上升沿写数据到PINC寄存器。在加载PINC寄存器后,将值写入POFF寄存器,条件是REG_SELECT=1,CE=1。

写PINC寄存器和POFF寄存器不要求CE有效。DDS在CE为有效高电平后喀什工作。如果在DDS配置时没有生成CE端口,则DDS在FPGA配置完成并系统时钟有效时就开始工作。

在核配置延时(由流水设置和CE信号决定)后,采样值出现在输出端口,并通过RDY信号指示(RDY=1)。核的延时决定了从SCLR置为低电平到RDY指示有输出之间的延时。RDY信号变为高电平(RDY=1)意味着在输出端口出现第一个有效采样,从SCLR置为低电平到第一个输出之间的延时为2个时钟周期。

在第n个时钟周期输出的相位值为PHASE_OUT(n)=PINC×n+POFF。

PINC=0x029 、POFF=0x100,相位输出PHASE_OUT依次为0x100 、ox020+0x100、0x020×2+0x100

可以使用SCLR信号来在PINC和/或POFF编程(写寄存器)期间或之后使输出同步,由于PINC和POFF编程最多有2个时钟周期的延时,SCLR信号在寄存器写操作完成后最少再过一个时钟周期再置为低电平。

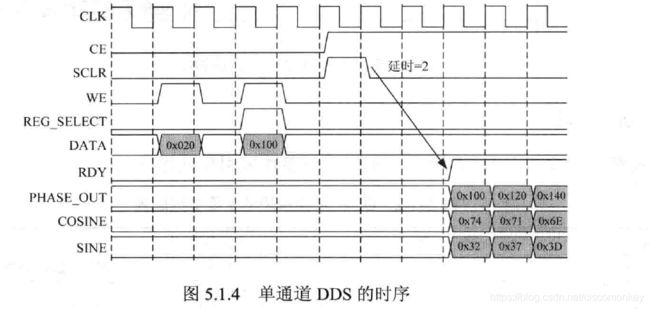

如果相位增量和/或相位偏移是连续输入的流(例如,用于调制频率和/或相位偏移),则相位增量和相位偏移分别通过PINC_IN端口和POFF_IN端口输入,第n个时钟周期的输出相位为:

则时序关系如图所示:

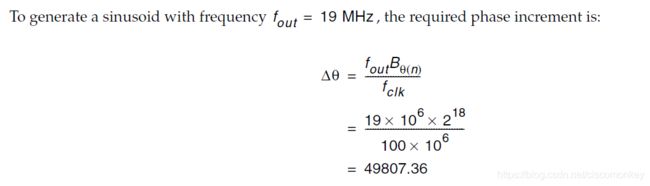

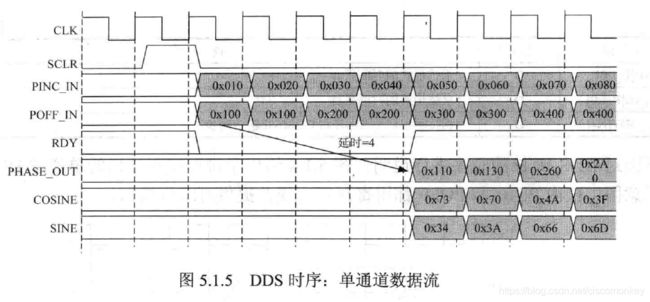

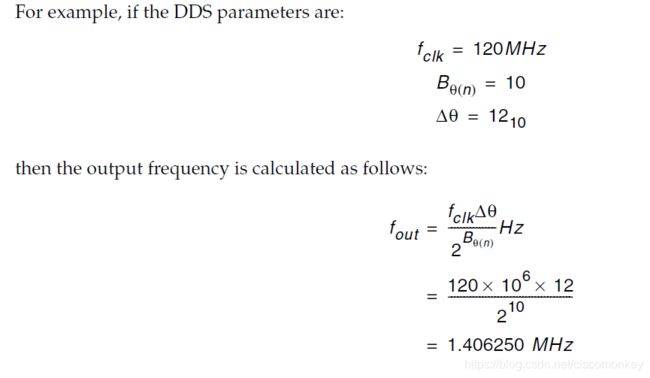

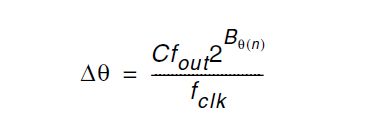

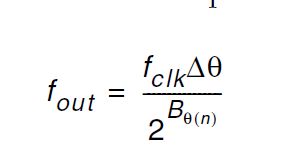

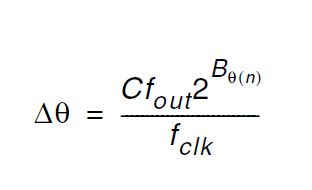

1.4 计算公式

![]()

![]()

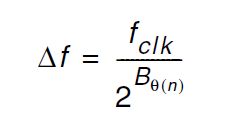

也就是说采用时分复用的话,我们需要将输出频率变小

从文档中介绍的来看,也就是说通道越多,频率分辨率越高

其实呀,我们自己仔细看看相位增量的公式和第一幅图中的频率输出公式吧,就知道其实两个公式都是一样的。也就是说,sin的大小由相位决定。所以相位增量,也就是决定了频率。

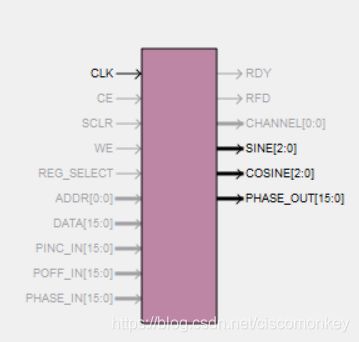

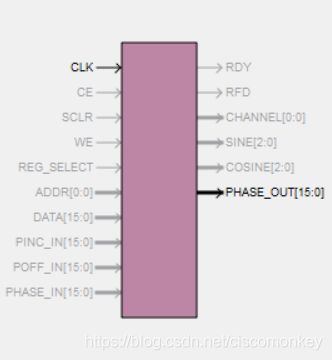

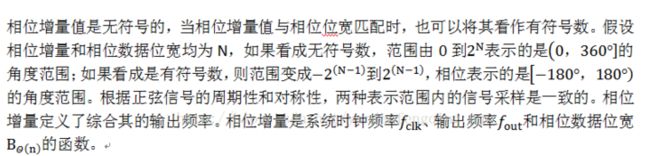

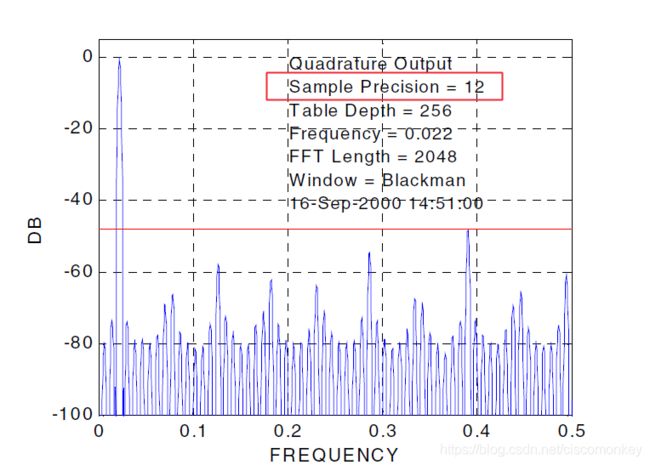

频谱纯度,下面这段话我们来看看,没有图也没有关系。我们从中可以知道增加采样的位数并不会减少毛刺,减少毛刺的唯一办法是增加LUT的表深度

对于更多的噪声的细节,我这里不再展开赘述,我们直接来看实际点的工程,具体要获知理论的话,你可以去看datasheet。

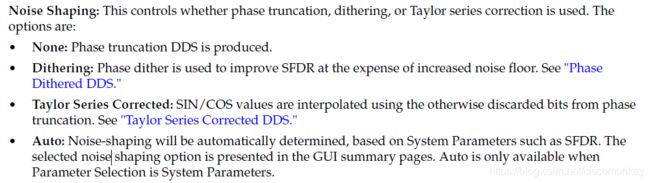

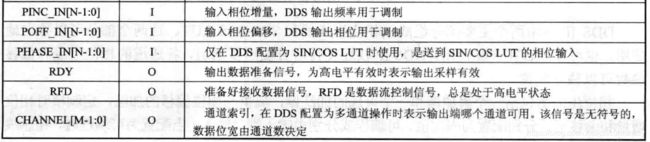

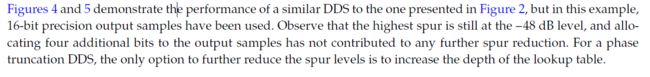

1.4 IP配置选项

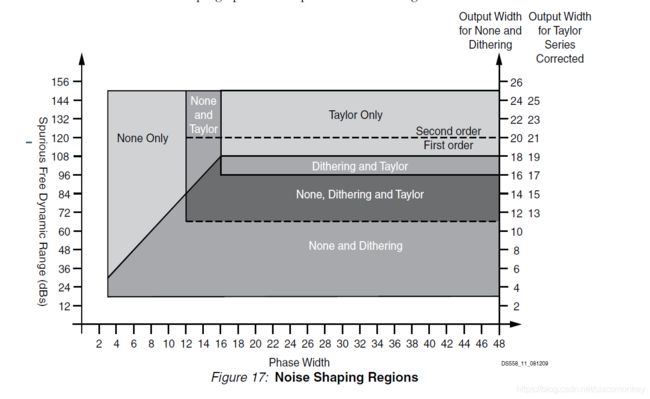

上面,我们介绍完了所有连线的含义,接下来,我们看看IP核的每一个参数都是代表什么意思。

首选component Name我就不说了,代表了这个DDS模块的名称。

配置选项:

Phase_Generator_and_SIN_COS_LUT

Phase_Generator_and_SIN_COS_LUT : DDS由Phase Generator和SIN/COS组合提供

并且带有可选的相位抖动(DDS is provided by combining Phase Generator and SIN/COS

LUT with an optional Dither circuit.)

- Phase_Generator_only

Phase_Generator_only: 仅仅提供相位输出(Only the phase generator is provided.)

- SIN_COS_LUT_only:

只提供了带有可选泰勒级数校正电路的SIN/COS LUT。(Only the SIN/COS LUT with optional Taylor Series Correction circuit is provided.)关于泰勒级数校正这一点我没去仔细研究,感兴趣的可以看看datasheet

SFDR和频率分辨率等系统参数及相位和输出数据位宽等硬件参数可以在定制IP核的图形用户界面上选择配置

如上图所示,我们再来看一下system requiremens里面的配置参数

SFDR可以设置,无杂散动态范围的大小,关于SFDR的概念,这里不再赘述。支持的无杂散动态范围SFDR为18~150dB

2、实际案例

2.1 overview

前面,我们已经阅读过理论部分了,大概读读理解了,就差不多了,下面我们来复习抓重点一下,然后就进入实际的工程。

- 重点1-特性

支持1到16个通道,使用高达48bit的相位累加器,可以以GUI的模式输入系统参数(SFDR和频率分辨率)或者硬件参数(相位和输出宽度)。这两种输入系统和硬件参数是可以互相推算出来的,所以对于熟悉频率分析的人可以采用系统参数,对于硬件工程师可以采用硬件参数。

此外能够最快跑到多少,也就是系统时钟最快到多少,这一点也是我们非常关心的。下面是v6,最快400M。spartan-6最快250M。

支持数据位宽为3~26位的输出采样精度,也就是说数据采样的精度是3 ~ 26位。再用XtremeDSP或FPGA逻辑资源实现时,支持使用位宽最大48位的相位累加器来实现高频率分辨率综合器。

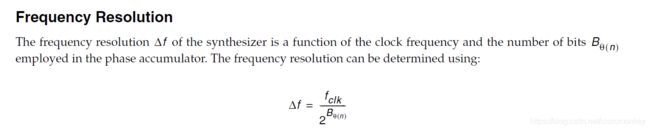

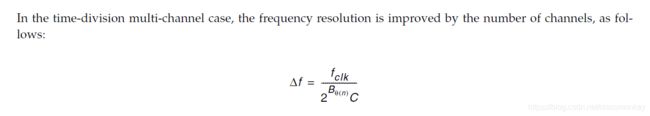

对于时分复用的多通道,频率分辨率

SDFR和频率分辨率等系统参数及相位和输出数据位宽等硬件参数可以在定制IP核的图形用户界面上选择配置。

数字积分器用于产生合适的相位参量并通过查找表映射,得到输出波形。通过查找表映射构造的正弦波的质量与处理过程相位和幅度量化有关,而查找表的深度和宽度分别决定了信号的相位分辨率和幅度分辨率。

对于时分复用的多通道,频率分辨率随通道数的增加而提高。

相位抖动DDS,在相位截断DDS中,由于量化器Q1操作丢弃了高精度相位累加器结果的低位比特,从而引入相位误差。相位误差是周期性序列,误差造成的影响反应在频谱上就是出现非期望的谱线。可以通过加性随机洗脑来打破查找表地址误差的规律性,随机信号序列称为抖动,是一个方差近似等于相位累加器最低整数位的噪声序列

- 重点2-理论

输出频率fout是系统时钟频率fclk,相位累加器中相位数据位宽B和相位增量的函数。通常我们知道输出频率,我们知道系统时钟频率,我们也可以定义相位的位宽,从而我们就可以倒推相位增量。

对于多个通道的情况如下;

Frequency Resolution

对于频率分辨率来说,相位的位宽,完全决定了频率分辨率。

In the time-division multi-channel case, the frequency resolution is improved by the number of channels, as follows:

Phase Increment

Spectral Purity Considerations频谱纯度

如果你想达到SFDR为SdB,那么相位精度,要设置到S/6 位,正是4096深度的地址表。

此外官方举了个例子,注意到SFDR有48dB 增加4位的输出采样位,并没有增加SFDR。也就是说增加数据的宽度是不能增加SFDR的。

如果要进一步增加SFDR的唯一方法是是增加查找表的深度,其实也就是减少相位增量,从而就能增加深度。

相位抖动Phase Dithered DDS

通过相位抖动选项扩展传统相位截断波形综合体系的谱线结构。

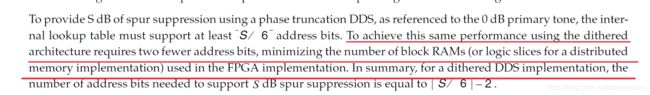

上面这两处,我也不知道为啥不一致。上面官方说了,为了达到相同的性能,并且可以减小RAM,可以使用相位抖动,从而就可以减小2bit的数据深度。

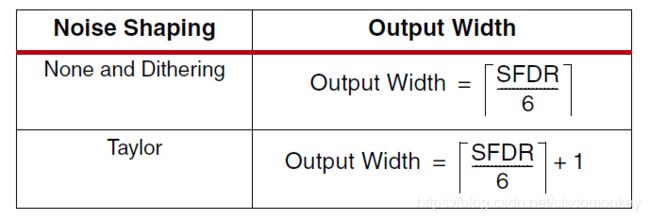

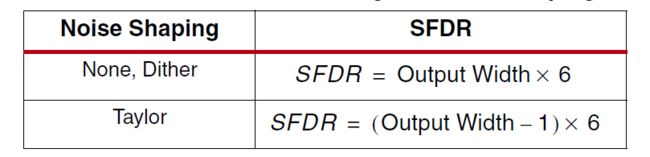

但是,我不知道下面表格这个公式里面有dither,然而却没有减去2.实际上启动了相位抖动后,至少可以将SFDR增加为12dB.从而至少可以减少宽度2bit。

当然,我认为以表格为准吧,毕竟表格里面是针对GUI界面来说明的。

这张表也很重要,也就是说你要到达很高的SFDR的话,相位抖动就不能用了。

其它泰勒修正,我就不介绍了(没耐心看)以后用到了再说吧

2.2、工程实战

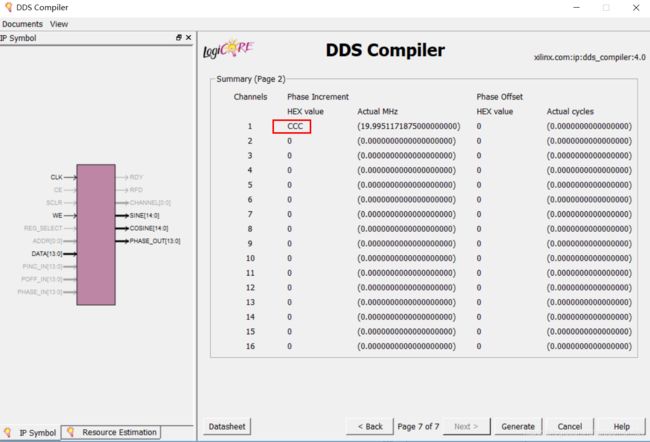

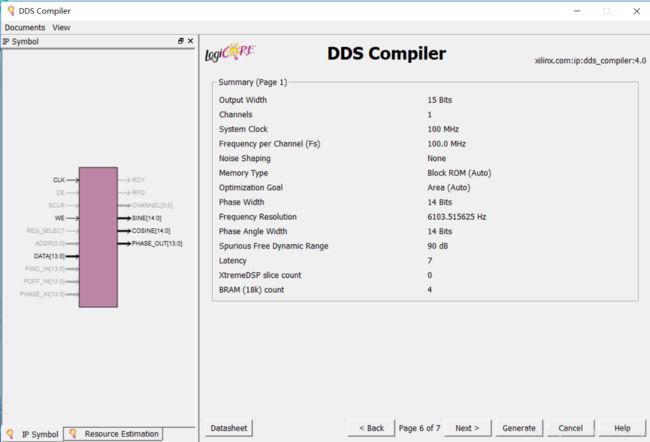

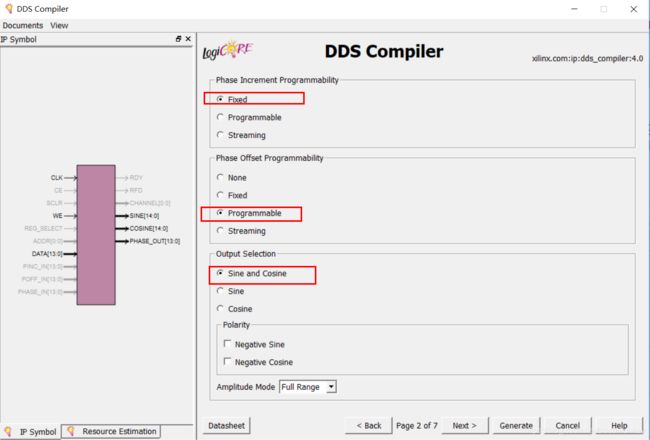

首先我们的SFDR设置为90dB,也就是说在使用noise none的情况下,输出的output width为90/6=15.频率分辨率设置将影响相位增量,也就是说DDS clock 100MHZ 100M/2^14=6103.515625

另外噪声整形我们设置为none。这样,我们就可以得到输出的位宽为15,相位位宽是14.

1、代表相位增量可编程

![]()

选择为fix固定选项后,相位增量被固定了,不可输入,如果选择为可编程,那么可以对相位增量进行流输入,从而这个输入允许DDS输出频率可以调制。

如果改成可编程后,PINC值可以在运行的时候使用ADDR,We,REG_SELECT and DATA ports来改变,推荐如果在需要改变频率的情况下可以选用这种模式。

2、相位偏移量可编程性质,这里选择为programmable。如果选择为fixed固定模式,POFF将会被固定,并且不能再运行的时候改变。如果选择为Programmable,那么POFF值可以在运行的时候通过ADDR、WE、REG_SELECT和DATA端口改变。而Streaming流控模式,POFF值可以直接通过POFF_IN端口改变,推荐当POFF值需要经常改变的时候推荐使用这种方式。

3、输出选择,选择Sine and Cosin

4、输出幅度的选择方式,一般选择full range即可

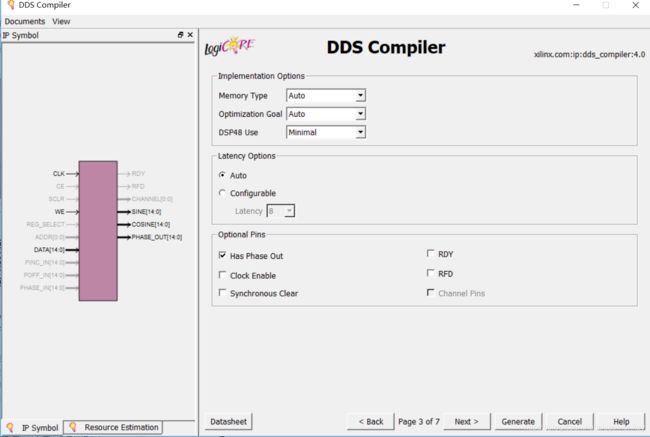

Memory type,系统可以自动选择,一般来说,自动设置会根据小数据的就选择分布式ROM,大数据的就自动选择BLOCK ROM。

优化选项:有时候,电路时钟的速度可以增加,这个选项控制着是针对高速度还是最少资源进行优化。

module DDS_top(

input clk,

input we, //写使能,使能PINC寄存器和POFF寄存器的写操作

input [13 : 0] data,//时间共享的数据总线,提供到PINC或POFF存储器的值。DATA端口的输入值表示相位

//数据位宽由相位位宽参数决定。PINC寄存器和POFF寄存器都是定点的,例如,如果

//data的数据位宽式8bit,但POFF仅需要1/8、2/8、3/8等等,则用于描述相位偏移

//的3个比特必须位于DATA端口数据的高三位

output [14 : 0] cosine,

output [14 : 0] sine,

output [13 : 0] phase_out

);

dds_ip dds_ip_inst

(

.clk(clk),

.we(we),

.data(data),

.cosine(cosine),

.sine(sine),

.phase_out(phase_out)

);

endmodule

测试代码:

`timescale 1ns / 1ns

// Company:

// Engineer:

//

// Create Date: 16:09:48 06/22/2019

// Design Name: DDS_top

// Module Name: D:/ISE_FPGA_Project/liruifeng_tem/ISE_learning/DDS_top/DDS_top/DDS_top_tb.v

// Project Name: DDS_top

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: DDS_top

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module DDS_top_tb;

// Inputs

reg clk;

reg we;

reg [14:0] data;

// Outputs

wire [14:0] cosine;

wire [14:0] sine;

wire [14:0] phase_out;

// Instantiate the Unit Under Test (UUT)

DDS_top uut (

.clk(clk),

.we(we),

.data(data),

.cosine(cosine),

.sine(sine),

.phase_out(phase_out)

);

initial

begin

// Initialize Inputs

#0 clk = 0;

#0 we = 1;

#0 data = 15'd200;

// Wait 100 ns for global reset to finish

#100 ;

forever

#5 clk =~clk;

end

endmodule

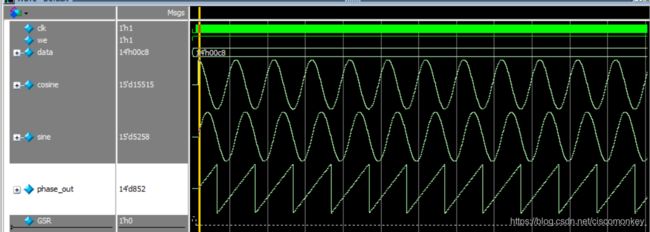

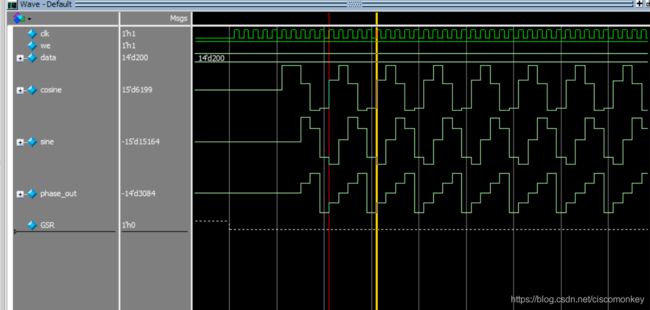

另外我们可以看到100M的时钟,输出频率20M,一个周期也就5个点

分析;

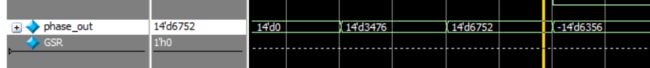

CCC的十进制是3276,另外相位偏移实200,所以第一个相位应该是3476,第二个相位应该是3476+3276=6752

下面,我们更改输出频率看看,输出频率为1M

2.3 工程福利

https://download.csdn.net/download/ciscomonkey/11258538

知识补充

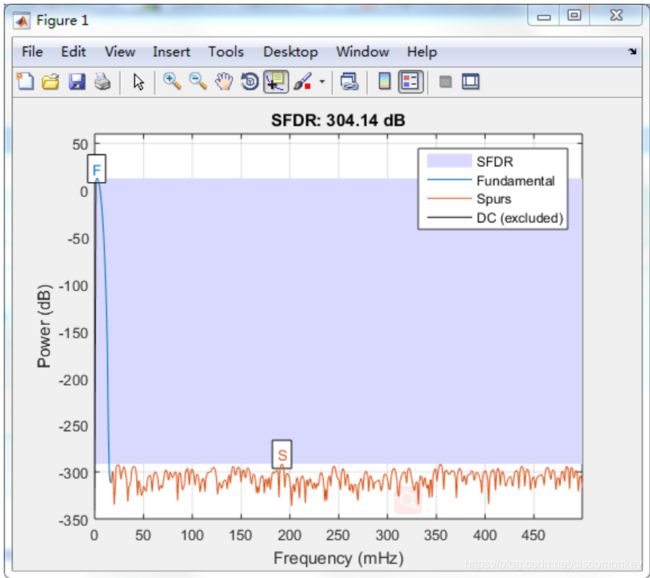

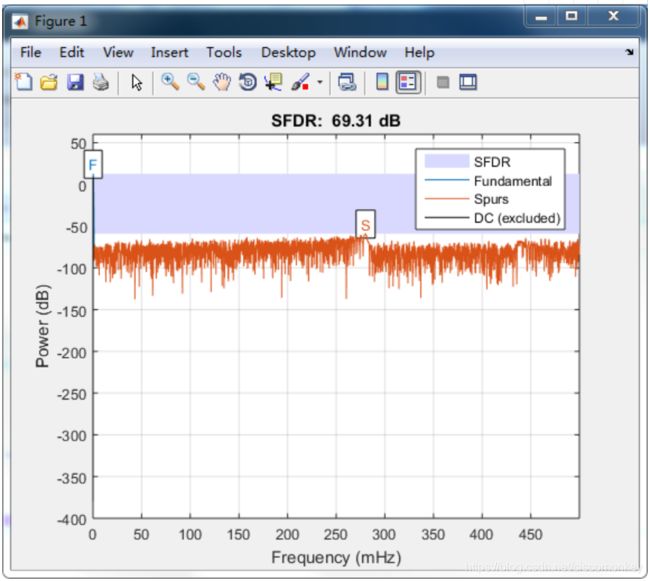

1、什么叫SFDR

分贝(dB) - 按照对数定义的一个幅度单位。对于电压值,dB以20log(VA/VB)给出;对于功率值,以10log(PA/PB)给出。dBc是相对于一个载波信号的dB值;dBm是相对于1mW的dB值。对于dBm而言,规格中的负载电阻必须是已知的(如:1mW提供给50Ω),以确定等效的电压或电流值。

SFDR参数分析:

SFDR是信号系统处理中常用的一项参数,对于评估系统的噪声水平和ADC/DAC的性能有一定参考意义。

SFDR,英文全称是 Spurious-Free Dynamic range,意为无杂散动态范围。SFDR是指基波强度与最大杂波或谐波的强度之比,所以SFDR值越大则说明系统的噪声水平越低,灵敏度越高。

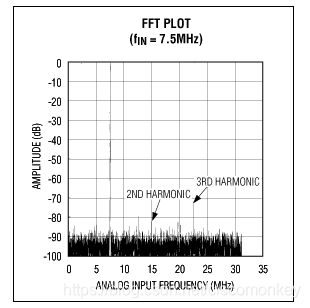

无杂散动态范围(SFDR) - 正弦波fIN (对于ADC指的是输入正弦波,对于DAC指的是重建的输出正弦波)的RMS值与在频域观察到的杂散信号的RMS值之比,典型值以分贝表示。SFDR在一些需要最大转换器动态范围的通信系统中非常重要。正如下图所示,我们看到FFT的plot图,输入信号是7.5MHZ,即为基波,基准频率的2倍也就是在15MHZ的位置,称之为2次谐波。随后在7.5MHZ*3=22.5MHZ的地方正是基准倍频的3倍,所以称之为3次谐波。

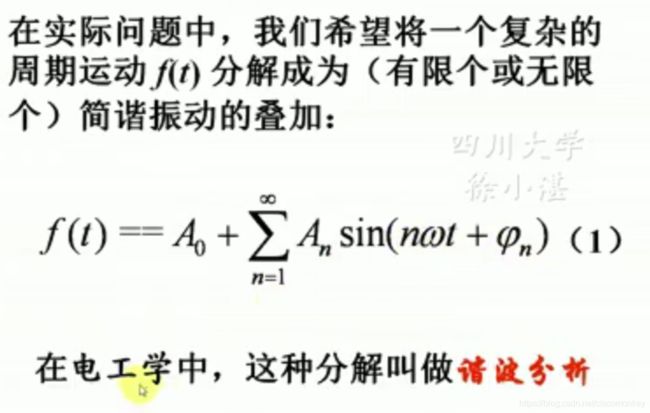

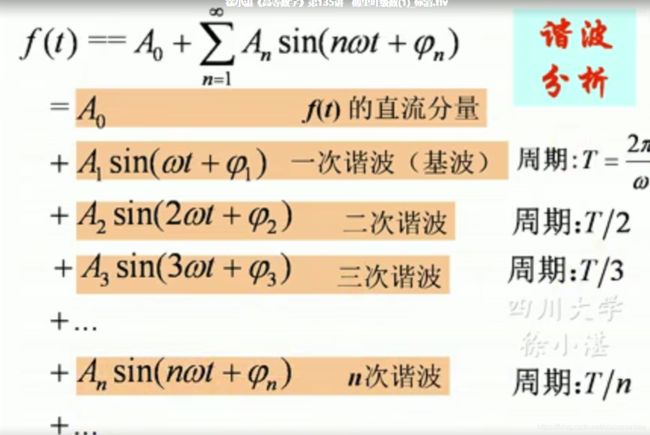

那么什么是基波?

在复杂的周期性震荡中,包含了基波和谐波。和该震荡最长周期相等的正弦波分量称为基波,相应于这个周期的频率称为基频,频率等于基本频率的整倍数的正弦波分量称为谐波。频率为其基准频率的一倍的称之为一次谐波(正是基波),频率为其基准频率的2倍的称之为2次谐波。

图中黑色部分为DC信号,蓝色部分是基波信号,红色部分是杂波信号。灰色区域是SFDR计算范围。