ARM处理器的异常模式

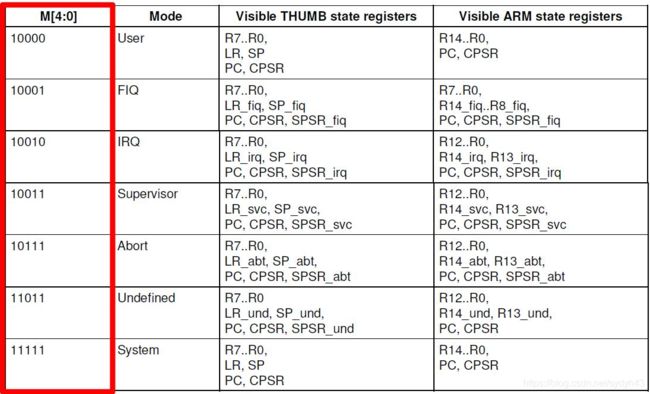

1、ARM处理器有各种异常模式,用于应对ARM出现的不同状态。出现异常时,会随即进入相关的异常向量,同时CPSR的寄存器也会设置成具体的模式。

例:当出现中断时,不管是哪种中断,都会跳转到0x18这个总入口地址(也有可能是0xFFFFFF18,看系统初始化的虚拟地址,无所谓),然后通过中断号执行具体的中断注册函数。

同时会把CPSR寄存器设置成相应的模式。

当从一个模式切换到另一个模式的时候,需要把之前模式下的HW context保存起来,比方说从用户态进入内核态,因为新模式下,内存区域划分是不一样的。如下图,各个模式下的通用寄存器是同一份,在两种模式下,可以用来传递信息,但是像sp,lr跟空间相关的寄存器会独立一份。

2、出现异常时,如何进入异常模式

2.1、在内核启动阶段,会对异常向量表完成初始化。

start_kernel

setup_arch

early_trap_initvoid __init early_trap_init(void *vectors_base)

{

unsigned long vectors = (unsigned long)vectors_base;

extern char __stubs_start[], __stubs_end[];

extern char __vectors_start[], __vectors_end[];

unsigned i;

vectors_page = vectors_base;

......

/*

* Copy the vectors, stubs and kuser helpers (in entry-armv.S)

* into the vector page, mapped at 0xffff0000, and ensure these

* are visible to the instruction stream.

*/

memcpy((void *)vectors, __vectors_start, __vectors_end - __vectors_start);

memcpy((void *)vectors + 0x1000, __stubs_start, __stubs_end - __stubs_start);

......

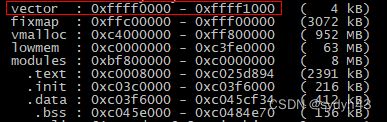

}异常向量地址保存在vectors_base变量(CONFIG_VECTORS_BASE=0xffff0000)中。

异常向量地址__vectors_start在entry-armv.S - arch/arm/kernel/entry-armv.S - Linux source code (v5.16.9) - Bootlin实现初始化。

在编译的时候,地址已经确定

grep "__vectors" System.map -nR启动的时候,可以看到异常向量的地址分布情况。

2.2、出现异常时,跳转到异常向量入口__vectors_start,不同的异常对应着不同的偏移量,从图1可以看出software interrrupt对应着异常向量第三项,即W(ldr) pc, .L__vectors_start + 0x1000对应着software interrupt的入口。

.L__vectors_start:

W(b) vector_rst

W(b) vector_und

W(ldr) pc, .L__vectors_start + 0x1000

W(b) vector_pabt

W(b) vector_dabt

W(b) vector_addrexcptn

W(b) vector_irq

W(b) vector_fiq

.data

.align 2

.globl cr_alignment后续会根据宏定义跳转到具体的异常向量处理流程。

.macro vector_stub, name, mode, correction=0

.align 5

vector_\name:

.if \correction

sub lr, lr, #\correction

.endif

@

@ Save r0, lr_ (parent PC) and spsr_

@ (parent CPSR)

@

stmia sp, {r0, lr} @ save r0, lr

mrs lr, spsr

str lr, [sp, #8] @ save spsr

@

@ Prepare for SVC32 mode. IRQs remain disabled.

@

mrs r0, cpsr

eor r0, r0, #(\mode ^ SVC_MODE | PSR_ISETSTATE)

msr spsr_cxsf, r0

@

@ the branch table must immediately follow this code

@

and lr, lr, #0x0f

THUMB( adr r0, 1f )

THUMB( ldr lr, [r0, lr, lsl #2] )

mov r0, sp

ARM( ldr lr, [pc, lr, lsl #2] )

movs pc, lr @ branch to handler in SVC mode

ENDPROC(vector_\name)