- Long类型前后端数据不一致

igotyback

前端

响应给前端的数据浏览器控制台中response中看到的Long类型的数据是正常的到前端数据不一致前后端数据类型不匹配是一个常见问题,尤其是当后端使用Java的Long类型(64位)与前端JavaScript的Number类型(最大安全整数为2^53-1,即16位)进行数据交互时,很容易出现精度丢失的问题。这是因为JavaScript中的Number类型无法安全地表示超过16位的整数。为了解决这个问

- LocalDateTime 转 String

igotyback

java开发语言

importjava.time.LocalDateTime;importjava.time.format.DateTimeFormatter;publicclassMain{publicstaticvoidmain(String[]args){//获取当前时间LocalDateTimenow=LocalDateTime.now();//定义日期格式化器DateTimeFormatterformat

- Linux下QT开发的动态库界面弹出操作(SDL2)

13jjyao

QT类qt开发语言sdl2linux

需求:操作系统为linux,开发框架为qt,做成需带界面的qt动态库,调用方为java等非qt程序难点:调用方为java等非qt程序,也就是说调用方肯定不带QApplication::exec(),缺少了这个,QTimer等事件和QT创建的窗口将不能弹出(包括opencv也是不能弹出);这与qt调用本身qt库是有本质的区别的思路:1.调用方缺QApplication::exec(),那么我们在接口

- 基于社交网络算法优化的二维最大熵图像分割

智能算法研学社(Jack旭)

智能优化算法应用图像分割算法php开发语言

智能优化算法应用:基于社交网络优化的二维最大熵图像阈值分割-附代码文章目录智能优化算法应用:基于社交网络优化的二维最大熵图像阈值分割-附代码1.前言2.二维最大熵阈值分割原理3.基于社交网络优化的多阈值分割4.算法结果:5.参考文献:6.Matlab代码摘要:本文介绍基于最大熵的图像分割,并且应用社交网络算法进行阈值寻优。1.前言阅读此文章前,请阅读《图像分割:直方图区域划分及信息统计介绍》htt

- DIV+CSS+JavaScript技术制作网页(旅游主题网页设计与制作)云南大理

STU学生网页设计

网页设计期末网页作业html静态网页html5期末大作业网页设计web大作业

️精彩专栏推荐作者主页:【进入主页—获取更多源码】web前端期末大作业:【HTML5网页期末作业(1000套)】程序员有趣的告白方式:【HTML七夕情人节表白网页制作(110套)】文章目录二、网站介绍三、网站效果▶️1.视频演示2.图片演示四、网站代码HTML结构代码CSS样式代码五、更多源码二、网站介绍网站布局方面:计划采用目前主流的、能兼容各大主流浏览器、显示效果稳定的浮动网页布局结构。网站程

- 【华为OD机试真题2023B卷 JAVA&JS】We Are A Team

若博豆

java算法华为javascript

华为OD2023(B卷)机试题库全覆盖,刷题指南点这里WeAreATeam时间限制:1秒|内存限制:32768K|语言限制:不限题目描述:总共有n个人在机房,每个人有一个标号(1<=标号<=n),他们分成了多个团队,需要你根据收到的m条消息判定指定的两个人是否在一个团队中,具体的:1、消息构成为:abc,整数a、b分别代

- 2023-04-17|篮球女孩

长一木

1小学抑或初中阶段,在课外书了解到她的故事。“篮球女孩”。当时佩服她的顽强,也对生命多了一丝敬畏。今天刚好在公众号看到,长大后的“篮球女孩”。佩服之余又满是心疼。网络侵删祝那素未蒙面的女孩,未来一切顺遂。

- 在一台Ubuntu计算机上构建Hyperledger Fabric网络

落叶无声9

区块链超级账本Hyperledgerfabric区块链ubuntu构建hyperledgerfabric

在一台Ubuntu计算机上构建HyperledgerFabric网络Hyperledgerfabric是一个开源的区块链应用程序平台,为开发基于区块链的应用程序提供了一个起点。当我们提到HyperledgerFabric网络时,我们指的是使用HyperledgerFabric的正在运行的系统。即使只使用最少数量的组件,部署Fabric网络也不是一件容易的事。Fabric社区创建了一个名为Cello

- GitHub上克隆项目

bigbig猩猩

github

从GitHub上克隆项目是一个简单且直接的过程,它允许你将远程仓库中的项目复制到你的本地计算机上,以便进行进一步的开发、测试或学习。以下是一个详细的步骤指南,帮助你从GitHub上克隆项目。一、准备工作1.安装Git在克隆GitHub项目之前,你需要在你的计算机上安装Git工具。Git是一个开源的分布式版本控制系统,用于跟踪和管理代码变更。你可以从Git的官方网站(https://git-scm.

- 关于城市旅游的HTML网页设计——(旅游风景云南 5页)HTML+CSS+JavaScript

二挡起步

web前端期末大作业javascripthtmlcss旅游风景

⛵源码获取文末联系✈Web前端开发技术描述网页设计题材,DIV+CSS布局制作,HTML+CSS网页设计期末课程大作业|游景点介绍|旅游风景区|家乡介绍|等网站的设计与制作|HTML期末大学生网页设计作业,Web大学生网页HTML:结构CSS:样式在操作方面上运用了html5和css3,采用了div+css结构、表单、超链接、浮动、绝对定位、相对定位、字体样式、引用视频等基础知识JavaScrip

- HTML网页设计制作大作业(div+css) 云南我的家乡旅游景点 带文字滚动

二挡起步

web前端期末大作业web设计网页规划与设计htmlcssjavascriptdreamweaver前端

Web前端开发技术描述网页设计题材,DIV+CSS布局制作,HTML+CSS网页设计期末课程大作业游景点介绍|旅游风景区|家乡介绍|等网站的设计与制作HTML期末大学生网页设计作业HTML:结构CSS:样式在操作方面上运用了html5和css3,采用了div+css结构、表单、超链接、浮动、绝对定位、相对定位、字体样式、引用视频等基础知识JavaScript:做与用户的交互行为文章目录前端学习路线

- node.js学习

小猿L

node.jsnode.js学习vim

node.js学习实操及笔记温故node.js,node.js学习实操过程及笔记~node.js学习视频node.js官网node.js中文网实操笔记githubcsdn笔记为什么学node.js可以让别人访问我们编写的网页为后续的框架学习打下基础,三大框架vuereactangular离不开node.jsnode.js是什么官网:node.js是一个开源的、跨平台的运行JavaScript的运行

- 【华为OD技术面试真题 - 技术面】-测试八股文真题题库(1)

算法大师

华为od面试python算法前端

华为OD面试真题精选专栏:华为OD面试真题精选目录:2024华为OD面试手撕代码真题目录以及八股文真题目录文章目录华为OD面试真题精选1.黑盒测试和白盒测试的区别2.假设我们公司现在开发一个类似于微信的软件1.0版本,现在要你测试这个功能:打开聊天窗口,输入文本,限制字数在200字以内。问你怎么提取测试点。功能测试性能测试安全性测试可用性测试跨平台兼容性测试网络环境测试3.接口测试的工具你了解哪些

- 01-Git初识

Meereen

Gitgit

01-Git初识概念:一个免费开源,分布式的代码版本控制系统,帮助开发团队维护代码作用:记录代码内容。切换代码版本,多人开发时高效合并代码内容如何学:个人本机使用:Git基础命令和概念多人共享使用:团队开发同一个项目的代码版本管理Git配置用户信息配置:用户名和邮箱,应用在每次提交代码版本时表明自己的身份命令:查看git版本号git-v配置用户名gitconfig--globaluser.name

- 《在战“疫”中成长致敬生活》观后感

梅子刘的刀

(作者:周晨)今天上午,我看了“我是接班人”网络大课堂《在战役中成长致敬生活》。有很多人拿出自己攒下的钱,默默地捐给了武汉,有几千块钱的、有几万块钱的,也有十几万块钱的。连小朋友也把自己的压岁钱捐给了武汉。有名环卫工人把自己五年的积蓄全部捐给了武汉。有名外卖小哥为医护人员买鞋子送吃的。还有已经治愈出院的新型肺炎病人捐了400毫升的血浆。还有位叫大树的叔叔,虽然他没有钱,但是他地里有蔬菜,捐了几大卡

- Java 重写(Override)与重载(Overload)

叨唧唧的

Java重写(Override)与重载(Overload)重写(Override)重写是子类对父类的允许访问的方法的实现过程进行重新编写,返回值和形参都不能改变。即外壳不变,核心重写!重写的好处在于子类可以根据需要,定义特定于自己的行为。也就是说子类能够根据需要实现父类的方法。重写方法不能抛出新的检查异常或者比被重写方法申明更加宽泛的异常。例如:父类的一个方法申明了一个检查异常IOExceptio

- 中原焦点团队网络初中级30期阴丽丽坚持分享第三百八十八次2022.10.18分享 约练次数(74) 咨询师(6) 来访者(53) 观察者(15)

阴丽丽

今天是忙碌的一天,一早起来,总想着找点把事情弄完,可总也弄不完。就这样弄着吧!孩子的事,自己的事都在那里搁置着,不想做,有点欧!今天总体还不错,只是在下午起床时走神了俩小时,也算是给自己的放松吧!今日难得1.儿子乖巧、听话,努力配合,一天下来也是忙忙碌碌,这真的很难得!2.儿子今天录的视频被班主任认可,这真的很难得3.我今天早上做核酸时,自己把教案整了一下,这真的很难得

- 网络编程基础

记得开心一点啊

网络

目录♫什么是网络编程♫Socket套接字♪什么是Socket套接字♪数据报套接字♪流套接字♫数据报套接字通信模型♪数据报套接字通讯模型♪DatagramSocket♪DatagramPacket♪实现UDP的服务端代码♪实现UDP的客户端代码♫流套接字通信模型♪流套接字通讯模型♪ServerSocket♪Socket♪实现TCP的服务端代码♪实现TCP的客户端代码♫什么是网络编程网络编程,指网络上

- 简单了解 JVM

记得开心一点啊

jvm

目录♫什么是JVM♫JVM的运行流程♫JVM运行时数据区♪虚拟机栈♪本地方法栈♪堆♪程序计数器♪方法区/元数据区♫类加载的过程♫双亲委派模型♫垃圾回收机制♫什么是JVMJVM是JavaVirtualMachine的简称,意为Java虚拟机。虚拟机是指通过软件模拟的具有完整硬件功能的、运行在一个完全隔离的环境中的完整计算机系统(如:JVM、VMwave、VirtualBox)。JVM和其他两个虚拟机

- 1分钟解决 -bash: mvn: command not found,在Centos 7中安装Maven

Energet!c

开发语言

1分钟解决-bash:mvn:commandnotfound,在Centos7中安装Maven检查Java环境1下载Maven2解压Maven3配置环境变量4验证安装5常见问题与注意事项6总结检查Java环境Maven依赖Java环境,请确保系统已经安装了Java并配置了环境变量。可以通过以下命令检查:java-version如果未安装,请先安装Java。1下载Maven从官网下载:前往Apach

- Java企业面试题3

马龙强_

java

1.break和continue的作用(智*图)break:用于完全退出一个循环(如for,while)或一个switch语句。当在循环体内遇到break语句时,程序会立即跳出当前循环体,继续执行循环之后的代码。continue:用于跳过当前循环体中剩余的部分,并开始下一次循环。如果是在for循环中使用continue,则会直接进行条件判断以决定是否执行下一轮循环。2.if分支语句和switch分

- 多子女家庭问题

3e5c5362403c

杨宁宁焦点解决网络初17中19坚持分享589天(2021.3.20)本周约练我1次,总计166次,读书打卡第256天案例督导收获:【家有老大篇】被爱与高期待下的独舞家里的第一个孩子往往集万千宠爱于一身。爸爸妈妈、爷爷奶奶、姥姥姥爷的目光都聚焦在他的身上。在这种光环下长大的孩子,就如小皇帝一般,衣来伸手、饭来张口。拥有爱的同时,也意味着拥有了更高的被期待,父母会花血本给你报各种各样的早教班,给你买各

- JVM、JRE和 JDK:理解Java开发的三大核心组件

Y雨何时停T

Javajava

Java是一门跨平台的编程语言,它的成功离不开背后强大的运行环境与开发工具的支持。在Java的生态中,JVM(Java虚拟机)、JRE(Java运行时环境)和JDK(Java开发工具包)是三个至关重要的核心组件。本文将探讨JVM、JDK和JRE的区别,帮助你更好地理解Java的运行机制。1.JVM:Java虚拟机(JavaVirtualMachine)什么是JVM?JVM,即Java虚拟机,是Ja

- 父母教育孩子的方式,将影响孩子一生

树英教育

为什么有些孩子总是充满自信与快乐?独立、有主见又坚强?而有些孩子却自卑、胆怯,软弱又过度依赖父母?为什么有些孩子总是健康、阳光又富于创造力?而有些孩子却悲观、孤僻又思想空乏?一个孩子的行为取决于孩子的思想,思想取决于环境和自己的认知,认知取决于教育。父母是孩子人生中的第一位教育者,父母养育孩子的方式,将决定他们人生的高度,影响他们的一生。网络图,侵权即删优秀的父母就像园丁,既要浇水施肥,又要修剪杂

- Java面试题精选:消息队列(二)

芒果不是芒

Java面试题精选javakafka

一、Kafka的特性1.消息持久化:消息存储在磁盘,所以消息不会丢失2.高吞吐量:可以轻松实现单机百万级别的并发3.扩展性:扩展性强,还是动态扩展4.多客户端支持:支持多种语言(Java、C、C++、GO、)5.KafkaStreams(一个天生的流处理):在双十一或者销售大屏就会用到这种流处理。使用KafkaStreams可以快速的把销售额统计出来6.安全机制:Kafka进行生产或者消费的时候会

- 2024.9.6 Python,华为笔试题总结,字符串格式化,字符串操作,广度优先搜索解决公司组织绩效互评问题,无向图

RaidenQ

python华为leetcode算法力扣广度优先无向图

1.字符串格式化name="Alice"age=30formatted_string="Name:{},Age:{}".format(name,age)print(formatted_string)或者name="Alice"age=30formatted_string=f"Name:{name},Age:{age}"print(formatted_string)2.网络健康检查第一行有两个整数m

- 戴容容 中原焦点团队.网络初级第33期,坚持分享第19天 2022年3月9日

TessDai

《每个人眼中的世界都是不同的》“一千个人眼里有一千个哈姆雷特”世界是多元的,每个人都有自己的道理,人人按照自己的理解去看待这个世界的人和物.我们如此,其他人也是如此.因此,任何事情,我们要放下自己以为的真理,去理解他人认为的真理,只有同频方能共振.孩子在慢慢长大的过程中慢慢学会独立,甚至对抗.尤其当孩子处于青春期的时候,他们开始有很多自己独立的想法,和一些特立独行的做法,家长常常会觉得不可思议,觉

- 白骑士的Java教学基础篇 2.5 控制流语句

白骑士所长

Java教学java开发语言

欢迎继续学习Java编程的基础篇!在前面的章节中,我们了解了Java的变量、数据类型和运算符。接下来,我们将探讨Java中的控制流语句。控制流语句用于控制程序的执行顺序,使我们能够根据特定条件执行不同的代码块,或重复执行某段代码。这是编写复杂程序的基础。通过学习这一节内容,你将掌握如何使用条件语句和循环语句来编写更加灵活和高效的代码。条件语句条件语句用于根据条件的真假来执行不同的代码块。if语句‘

- python语法——三目运算符

HappyRocking

pythonpython三目运算符

在java中,有三目运算符,如:intc=(a>b)?a:b表示c取两者中的较大值。但是在python,不能直接这样使用,估计是因为冒号在python有分行的关键作用。那么在python中,如何实现类似功能呢?可以使用ifelse语句,也是一行可以完成,格式为:aifbelsec表示如果b为True,则表达式等于a,否则等于c。如:c=(aif(a>b)elseb)同样是完成了取最大值的功能。

- 第1步win10宿主机与虚拟机通过NAT共享上网互通

学习3人组

大数据大数据

VM的CentOS采用NAT共用宿主机网卡宿主机器无法连接到虚拟CentOS要实现宿主机与虚拟机通信,原理就是给宿主机的网卡配置一个与虚拟机网关相同网段的IP地址,实现可以互通。1、查看虚拟机的IP地址2、编辑虚拟机的虚拟网络的NAT和DHCP的配置,设置虚拟机的网卡选择NAT共享模式3、宿主机的IP配置,确保vnet8的IPV4属性与虚拟机在同一网段4、ping测试连通性[root@localh

- Spring的注解积累

yijiesuifeng

spring注解

用注解来向Spring容器注册Bean。

需要在applicationContext.xml中注册:

<context:component-scan base-package=”pagkage1[,pagkage2,…,pagkageN]”/>。

如:在base-package指明一个包

<context:component-sc

- 传感器

百合不是茶

android传感器

android传感器的作用主要就是来获取数据,根据得到的数据来触发某种事件

下面就以重力传感器为例;

1,在onCreate中获得传感器服务

private SensorManager sm;// 获得系统的服务

private Sensor sensor;// 创建传感器实例

@Override

protected void

- [光磁与探测]金吕玉衣的意义

comsci

这是一个古代人的秘密:现在告诉大家

信不信由你们:

穿上金律玉衣的人,如果处于灵魂出窍的状态,可以飞到宇宙中去看星星

这就是为什么古代

- 精简的反序打印某个数

沐刃青蛟

打印

以前看到一些让求反序打印某个数的程序。

比如:输入123,输出321。

记得以前是告诉你是几位数的,当时就抓耳挠腮,完全没有思路。

似乎最后是用到%和/方法解决的。

而今突然想到一个简短的方法,就可以实现任意位数的反序打印(但是如果是首位数或者尾位数为0时就没有打印出来了)

代码如下:

long num, num1=0;

- PHP:6种方法获取文件的扩展名

IT独行者

PHP扩展名

PHP:6种方法获取文件的扩展名

1、字符串查找和截取的方法

1

$extension

=

substr

(

strrchr

(

$file

,

'.'

), 1);

2、字符串查找和截取的方法二

1

$extension

=

substr

- 面试111

文强chu

面试

1事务隔离级别有那些 ,事务特性是什么(问到一次)

2 spring aop 如何管理事务的,如何实现的。动态代理如何实现,jdk怎么实现动态代理的,ioc是怎么实现的,spring是单例还是多例,有那些初始化bean的方式,各有什么区别(经常问)

3 struts默认提供了那些拦截器 (一次)

4 过滤器和拦截器的区别 (频率也挺高)

5 final,finally final

- XML的四种解析方式

小桔子

domjdomdom4jsax

在平时工作中,难免会遇到把 XML 作为数据存储格式。面对目前种类繁多的解决方案,哪个最适合我们呢?在这篇文章中,我对这四种主流方案做一个不完全评测,仅仅针对遍历 XML 这块来测试,因为遍历 XML 是工作中使用最多的(至少我认为)。 预 备 测试环境: AMD 毒龙1.4G OC 1.5G、256M DDR333、Windows2000 Server

- wordpress中常见的操作

aichenglong

中文注册wordpress移除菜单

1 wordpress中使用中文名注册解决办法

1)使用插件

2)修改wp源代码

进入到wp-include/formatting.php文件中找到

function sanitize_user( $username, $strict = false

- 小飞飞学管理-1

alafqq

管理

项目管理的下午题,其实就在提出问题(挑刺),分析问题,解决问题。

今天我随意看下10年上半年的第一题。主要就是项目经理的提拨和培养。

结合我自己经历写下心得

对于公司选拔和培养项目经理的制度有什么毛病呢?

1,公司考察,选拔项目经理,只关注技术能力,而很少或没有关注管理方面的经验,能力。

2,公司对项目经理缺乏必要的项目管理知识和技能方面的培训。

3,公司对项目经理的工作缺乏进行指

- IO输入输出部分探讨

百合不是茶

IO

//文件处理 在处理文件输入输出时要引入java.IO这个包;

/*

1,运用File类对文件目录和属性进行操作

2,理解流,理解输入输出流的概念

3,使用字节/符流对文件进行读/写操作

4,了解标准的I/O

5,了解对象序列化

*/

//1,运用File类对文件目录和属性进行操作

//在工程中线创建一个text.txt

- getElementById的用法

bijian1013

element

getElementById是通过Id来设置/返回HTML标签的属性及调用其事件与方法。用这个方法基本上可以控制页面所有标签,条件很简单,就是给每个标签分配一个ID号。

返回具有指定ID属性值的第一个对象的一个引用。

语法:

&n

- 励志经典语录

bijian1013

励志人生

经典语录1:

哈佛有一个著名的理论:人的差别在于业余时间,而一个人的命运决定于晚上8点到10点之间。每晚抽出2个小时的时间用来阅读、进修、思考或参加有意的演讲、讨论,你会发现,你的人生正在发生改变,坚持数年之后,成功会向你招手。不要每天抱着QQ/MSN/游戏/电影/肥皂剧……奋斗到12点都舍不得休息,看就看一些励志的影视或者文章,不要当作消遣;学会思考人生,学会感悟人生

- [MongoDB学习笔记三]MongoDB分片

bit1129

mongodb

MongoDB的副本集(Replica Set)一方面解决了数据的备份和数据的可靠性问题,另一方面也提升了数据的读写性能。MongoDB分片(Sharding)则解决了数据的扩容问题,MongoDB作为云计算时代的分布式数据库,大容量数据存储,高效并发的数据存取,自动容错等是MongoDB的关键指标。

本篇介绍MongoDB的切片(Sharding)

1.何时需要分片

&nbs

- 【Spark八十三】BlockManager在Spark中的使用场景

bit1129

manager

1. Broadcast变量的存储,在HttpBroadcast类中可以知道

2. RDD通过CacheManager存储RDD中的数据,CacheManager也是通过BlockManager进行存储的

3. ShuffleMapTask得到的结果数据,是通过FileShuffleBlockManager进行管理的,而FileShuffleBlockManager最终也是使用BlockMan

- yum方式部署zabbix

ronin47

yum方式部署zabbix

安装网络yum库#rpm -ivh http://repo.zabbix.com/zabbix/2.4/rhel/6/x86_64/zabbix-release-2.4-1.el6.noarch.rpm 通过yum装mysql和zabbix调用的插件还有agent代理#yum install zabbix-server-mysql zabbix-web-mysql mysql-

- Hibernate4和MySQL5.5自动创建表失败问题解决方法

byalias

J2EEHibernate4

今天初学Hibernate4,了解了使用Hibernate的过程。大体分为4个步骤:

①创建hibernate.cfg.xml文件

②创建持久化对象

③创建*.hbm.xml映射文件

④编写hibernate相应代码

在第四步中,进行了单元测试,测试预期结果是hibernate自动帮助在数据库中创建数据表,结果JUnit单元测试没有问题,在控制台打印了创建数据表的SQL语句,但在数据库中

- Netty源码学习-FrameDecoder

bylijinnan

javanetty

Netty 3.x的user guide里FrameDecoder的例子,有几个疑问:

1.文档说:FrameDecoder calls decode method with an internally maintained cumulative buffer whenever new data is received.

为什么每次有新数据到达时,都会调用decode方法?

2.Dec

- SQL行列转换方法

chicony

行列转换

create table tb(终端名称 varchar(10) , CEI分值 varchar(10) , 终端数量 int)

insert into tb values('三星' , '0-5' , 74)

insert into tb values('三星' , '10-15' , 83)

insert into tb values('苹果' , '0-5' , 93)

- 中文编码测试

ctrain

编码

循环打印转换编码

String[] codes = {

"iso-8859-1",

"utf-8",

"gbk",

"unicode"

};

for (int i = 0; i < codes.length; i++) {

for (int j

- hive 客户端查询报堆内存溢出解决方法

daizj

hive堆内存溢出

hive> select * from t_test where ds=20150323 limit 2;

OK

Exception in thread "main" java.lang.OutOfMemoryError: Java heap space

问题原因: hive堆内存默认为256M

这个问题的解决方法为:

修改/us

- 人有多大懒,才有多大闲 (评论『卓有成效的程序员』)

dcj3sjt126com

程序员

卓有成效的程序员给我的震撼很大,程序员作为特殊的群体,有的人可以这么懒, 懒到事情都交给机器去做 ,而有的人又可以那么勤奋,每天都孜孜不倦得做着重复单调的工作。

在看这本书之前,我属于勤奋的人,而看完这本书以后,我要努力变成懒惰的人。

不要在去庞大的开始菜单里面一项一项搜索自己的应用程序,也不要在自己的桌面上放置眼花缭乱的快捷图标

- Eclipse简单有用的配置

dcj3sjt126com

eclipse

1、显示行号 Window -- Prefences -- General -- Editors -- Text Editors -- show line numbers

2、代码提示字符 Window ->Perferences,并依次展开 Java -> Editor -> Content Assist,最下面一栏 auto-Activation

- 在tomcat上面安装solr4.8.0全过程

eksliang

Solrsolr4.0后的版本安装solr4.8.0安装

转载请出自出处:

http://eksliang.iteye.com/blog/2096478

首先solr是一个基于java的web的应用,所以安装solr之前必须先安装JDK和tomcat,我这里就先省略安装tomcat和jdk了

第一步:当然是下载去官网上下载最新的solr版本,下载地址

- Android APP通用型拒绝服务、漏洞分析报告

gg163

漏洞androidAPP分析

点评:记得曾经有段时间很多SRC平台被刷了大量APP本地拒绝服务漏洞,移动安全团队爱内测(ineice.com)发现了一个安卓客户端的通用型拒绝服务漏洞,来看看他们的详细分析吧。

0xr0ot和Xbalien交流所有可能导致应用拒绝服务的异常类型时,发现了一处通用的本地拒绝服务漏洞。该通用型本地拒绝服务可以造成大面积的app拒绝服务。

针对序列化对象而出现的拒绝服务主要

- HoverTree项目已经实现分层

hvt

编程.netWebC#ASP.ENT

HoverTree项目已经初步实现分层,源代码已经上传到 http://hovertree.codeplex.com请到SOURCE CODE查看。在本地用SQL Server 2008 数据库测试成功。数据库和表请参考:http://keleyi.com/a/bjae/ue6stb42.htmHoverTree是一个ASP.NET 开源项目,希望对你学习ASP.NET或者C#语言有帮助,如果你对

- Google Maps API v3: Remove Markers 移除标记

天梯梦

google maps api

Simply do the following:

I. Declare a global variable:

var markersArray = [];

II. Define a function:

function clearOverlays() {

for (var i = 0; i < markersArray.length; i++ )

- jQuery选择器总结

lq38366

jquery选择器

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

- 基础数据结构和算法六:Quick sort

sunwinner

AlgorithmQuicksort

Quick sort is probably used more widely than any other. It is popular because it is not difficult to implement, works well for a variety of different kinds of input data, and is substantially faster t

- 如何让Flash不遮挡HTML div元素的技巧_HTML/Xhtml_网页制作

刘星宇

htmlWeb

今天在写一个flash广告代码的时候,因为flash自带的链接,容易被当成弹出广告,所以做了一个div层放到flash上面,这样链接都是a触发的不会被拦截,但发现flash一直处于div层上面,原来flash需要加个参数才可以。

让flash置于DIV层之下的方法,让flash不挡住飘浮层或下拉菜单,让Flash不档住浮动对象或层的关键参数:wmode=opaque。

方法如下:

- Mybatis实用Mapper SQL汇总示例

wdmcygah

sqlmysqlmybatis实用

Mybatis作为一个非常好用的持久层框架,相关资料真的是少得可怜,所幸的是官方文档还算详细。本博文主要列举一些个人感觉比较常用的场景及相应的Mapper SQL写法,希望能够对大家有所帮助。

不少持久层框架对动态SQL的支持不足,在SQL需要动态拼接时非常苦恼,而Mybatis很好地解决了这个问题,算是框架的一大亮点。对于常见的场景,例如:批量插入/更新/删除,模糊查询,多条件查询,联表查询,

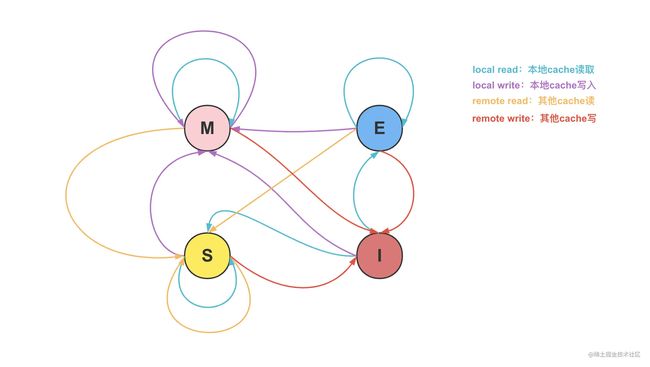

我们这里用CPU的两个核CA(coreA)和CB(coreB)以及缓存行数据 X 来解释下上面图片的转变,当CA中存在X:

我们这里用CPU的两个核CA(coreA)和CB(coreB)以及缓存行数据 X 来解释下上面图片的转变,当CA中存在X: