一文读懂SerDes技术

SerDes Technology

1. Serial Interface Technique Development

1.1 Parallel/Serial Interface

数据的传输最开始是低速的串行接口(Serial Interface,简称串口),为了提高数据的总带宽,首先想到的是增加数据的传输位宽,再进一步提升速率,也就是并行接口(Parallel Interface,简称并口)的方式,并逐渐取代传统低速串口成为主流。但随着并口的发展,其限制也也越来越明显。而高速串行(High Speed Serial, HSS)接口技术具有的优势使其有取代目前并口的趋势。

并口发展遇到的限制为: 芯片IO口数量的紧张,并口数据率提升过程中的串扰(Cross-talk)和同步切换噪声(SSN,=LNdi/dt L指芯片封装电感,N指数据位宽,di/dt是电流变化斜率),使得数据的同步变得困难。

串口与并口的演进是交替发展的。串口的典型代表是在消费电子领域普遍使用的通用串行总线(Universal Serial Bus, USB),并口也有很多,例如DDR SDRAM内存接口,也即常说的DDRx。

对于串口与并口的速率,从线速率(line rate)来看,例如DDR3-1600的最大线速率为1600Mbps(也就是1.6Gbps),从总数据带宽角度看,64bit DDR3-1600的最大数据带宽超过了100Gbps(64*1.6Gbps),SerDes也可以多通道并行使用,比如PCIe协议的x4、x8、x16模式,尽管存在多通道的对齐问题。

高速串口技术的发展未来仍是提升单通道速度和多通道并行使用相结合。因此在未来,串并口的概念会进一步模糊,整体结果是提供不断改进升级的数据总带宽。

1.2 Chip-Chip Synchronization Technique

现在大部分数字电路都采用同步电路,即系统中有一个统一的时钟对信号进行采样。芯片与芯片之间的同步接口通信有三种时序模型,分别是系统同步、源同步和自同步。

最初接口速率较低时,使用系统同步即可满足要求。随着接口速率的提升,严格的时序要求使用数据和时钟同步传输的源同步方式,例如DDR的数据线dq要与时钟线dqs同步。

而在目前SerDes中,采用自同步方式,接口传输的数据中包括时钟信息,通过接收端(Rx)的时钟数据恢复(Clock Data Recovery, CDR)电路完成对接收数据的时钟抽取和数据的再采样,最终恢复正确的数据。

因为相比于源同步接口,SerDes接口主要优点包括:

(1)数据中内嵌时钟,不需要单独的时钟信号走线

(2)通过预均衡/均衡技术实现高速长距离传输,如背板

(3)使用较少芯片引脚。

2. SerDes Introduction

对于在高速串行链路(High Speed Serial Link)使用的SerDes技术,其中Ser与Des分别是串化器(Serializer)与解串器(Deserializer)的简写,也即说明了SerDes的主要功能是将低速的并行信号转化为高速低压差分信号(LVDS)并通过串行里链路发送,同时能够接收串行输入LVDS信号并正确的转化为低速并行信号,简单来讲就是完成并串与串并的转化。

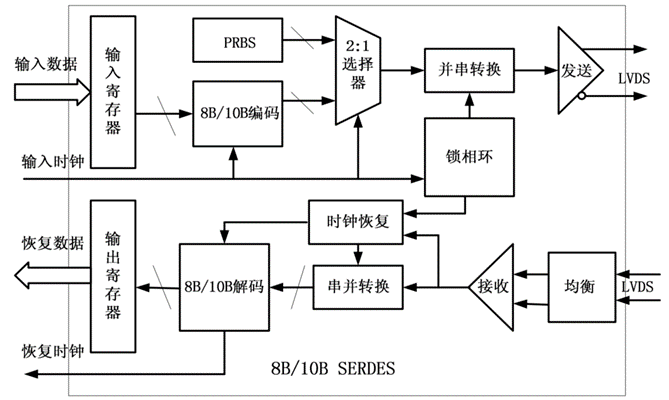

一个完整的8B/10B SERDES模块,Serializer由8B/10B编码器、PRBS码生成器、并串转换电路、差分信号发送器、PLL等模块构成;Deserializer则包括差分信号接收器、CDR(时钟数据恢复电路)、串并转换电路及8B/10B解码器,SerDes结构如下图所示。

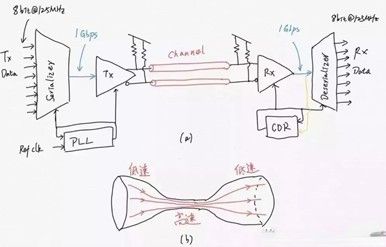

SerDes接口的简化电路如图下所示。图(a)中时钟速率为125MHz的8bit并行数据(一个时钟周期8ns,共8bit数据),经过Mux(复用器)芯片时分复用到1bit数据线上,转化为1Gbps的1bit串行数据(一个UI为1ns,包含1bit数据),经过发送器和通道到接收器,经过接收器处理后仍为1Gbps,解串后恢复为125MHz时钟速率的8bit并行数据。

SerDes是典型的数模混合系统,需要数字电路和模拟电路、信号与系统、通信原理、微波和射频电路、电磁场、信号和电源完整性等背景知识,综合要求比较高,是目前点到点(point-to-point)有线(wireline)通信的技术热点。

SerDes技术主要体现在以下几方面:

2.1 Clock generation (high frequency and low jitter)

比如对于10Gpbs数据率,内部需要产生至少10GHz的时钟(Single Date Rate, SDR)或5GHz的时钟(Double Date Rate, DDR)。随着SerDes的发展,内部PLL的时钟频率的不断提高,Ring PLL和LC tank PLL都是不可缺少的,时钟的抖动和各种各样的Jitter等对误码率(BER)的影响都需要充分分析。高性能时钟是整个SerDes系统设计的一个技术重点。

2.2 Equalizer

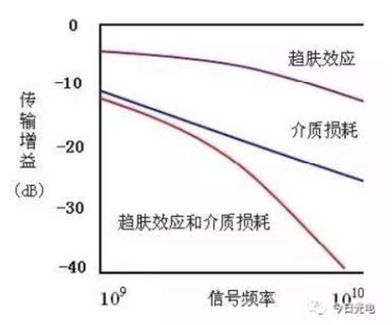

随着信号速率提高和由于架构需要而导致的传输链路长度增加,高速信号的趋肤效应和传输线的介质损耗使得信号在传输过程中损耗较大,Tx端发送的数据由于码间干扰(ISI)使得Rx端的信号已经没了模样。

为了把数据正确恢复出来,需要通过Equalizer均衡信道的衰减和数据的码间干扰。比如Tx端的Pre-Equalizer,常采用前馈均衡FFE结构,注意Pre-Equalizer的参数需要和该信号传输通道的损耗特性相匹配才能得到较好的信号改善效果。Rx采用连续时间线性均衡CTLE和判决前馈均衡DFE等手段,一般在RX端采用CTLE与DFE串接方式。

2.3 Self-Adaptive Algorithm

Rx的均衡通常需要满足不同材质和长度信道的特性,并对信号不同频率成分的衰减进行补偿。CTLE和DFE通常都会使用自适应算法Self-Adaptive Algorithm实时动态调整来应对信道的特性变化。如果不了解算法实现,就不能准确的理解DFE的本质。

2.4 CDR

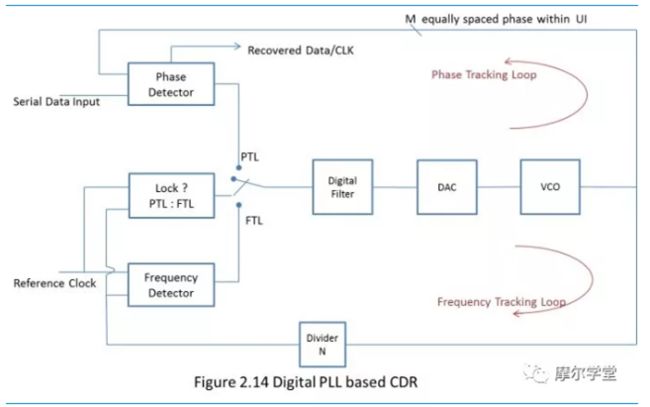

除了EQ之外,RX端的另一个难点是CDR(Clock and Data Recovery)环路,CDR的实现有不同的实现方式。CDR的环路通常会包含大量数字实现,例如PLL。一个简化的CDR结构如图所示。

2.5 Timing constraint

当数据率升高时,对于DFE的判决反馈回路的时序设计提出了更高的要求。比如说对于50Gbps的SerDes,一个UI的时间为20ps,几乎和逻辑门的延迟相当,这就要求DFE的反馈回路的逻辑设计必须尽可能的简单。单独时钟速率会遇到困难,而采用PAM-4或PAM-8等信号方式就会显得很有前景。

SerDes是一个复杂数模混合系统,内部还包含了大量数字实现内容。8B/10B等编解码实现,PRBS生成和检查,环回测试、自适应算法实现,系统状态控制数字实现等等。

3. SerDes Application

目前SerDes的应用,主要有Chip-to-Chip,Board-to-Board, Box-to-Box等形式,如图(a/b/c)示意图。并在大型数据中心,通信骨干网络,消费电子等场景下都有应用。

4. SerDes Core Technical Details

4.1 SerDes Equalization

SerDes信号从发送端到达接收端所经过的路径称为信道 channel或传输线,包括芯片封装,pcb走线,过孔,电缆,连接器等元件。某类传输线的路径损耗如图所示。

在高速信号传输中,信号的高频分量衰减要比低频分量的衰减大很多,从频域看,信道对高速信号表现出来的特性类似于LFP模型,如果SerDes的速率大于信道的截止频率,就会一定程度上损伤(distort)信号。均衡器Equalization的作用就是补偿信道对信号的损伤,表现出高通滤波器的特性。

均衡技术按照激励源来分主要由两大类:无源均衡和有源均衡。

无源均衡:类似于无源滤波器,通过频率响应去衰减SerDes调制的Nyquist频段内的低频传输损耗,从而达到带宽内均衡。

有源均衡:通过有源放大器去补偿SerDes调制的Nyquist高频传输损耗,或者衰减低频传输损耗从而达到带内均衡。

有源均衡技术按照电路类型分为:模拟电路均衡CTLE和数字电路均衡FFE、DFE

有源均衡技术按照传递函数相关性分为:线性CTLE、FFE和非线性DFE

带均衡的SerDes数据链路:

TX端内部先做并行转串行信号,同步通过PLL 生成Nyquist频率,将数据调制成SerDes信号,根据传输通道损耗使用不同的FFE,经过一系列无源通道链路传输后达到RX端,RX端内部获取SerDes信号要经过一系列线性CTLE和非线性DFE均衡达到SerDes协议一致性要求,再经过CDR内部的PLL完成时钟和数据的恢复,并将串行数据转化成并行数据。

4.1.1 Linear EQ & Non-Linear EQ

对于高速(>5Gbps)SerDes,由于信号的抖动(如ISI相关的确定性抖动)可能会超过或接近一个符号间隔(UI, Unit Interval), 单单使用线性均衡器不再适用。线性均衡器对噪声和信号一起放大,并没有改善SNR或者说BER。对于高速SerDes,采用一种称作DFE (Decision Feedback Equalizer)的非线性均衡器。DFE通过跟踪过去多个UI的数据(history bits)来预测当前bit的采样门限。DFE只对信号放大,不对噪声放大,可以有效改善SNR。

4.1.2 TX Equalizer

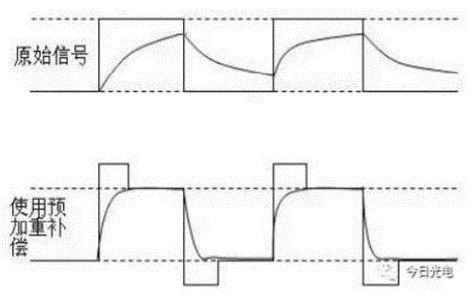

TX-EQ又称作预均衡或加重器(emphasis)。Emphasis分为预加重(pre-emphasis)和去加重(de-emphasis)。

Pre-emphasis的思想就是在传输线的始端增强信号的高频成分,以补偿高频分量在传输过程的过大衰减,技术上实现是增加差分信号的在上升沿和下降沿处的摆幅。

De-emphasis与Pre-emphasis类似,其思想是保持信号上升沿和下降沿处的幅度不变,降低信号在中频的摆幅(swing)。FPGA大部分使用de-emphasis的方式,加重越强,信号平均幅度会越小。

实际使用中更多的采用去加重技术,因为去加重补偿后的信号摆幅小,眼图高度低,功耗小,EMC辐射小。

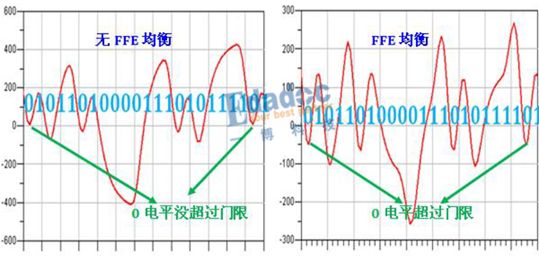

TX EQ采用FFE(Feed forward equalizers)结构,FFE的实现方式有很多,FFE的位置在发送端,它是利用波形本身来校正接收到的信号,而不是用波形的阈值(判决逻辑1或0 )进行校正。

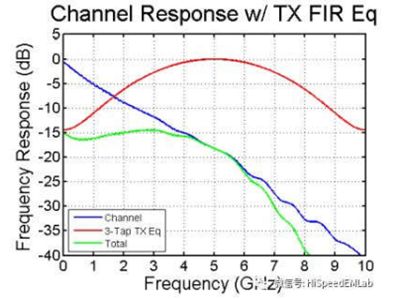

均衡器FFE的作用基本上类似于 离散型的多抽头数字FIR滤波器(Finite Impulse Response),它在校正当前比特电压时,使用的是前一个比特和当前比特的电压电平,加上校正因子(抽头系数,pre cursor\post cursor\main cursor),来校正当前比特的电压电平。一句话,就是当使用FFE时,是对实际采集到的波形执行均衡算法,目前常见的TX端预均衡的增益在10dB左右。下图给出TX发送端框图,包含并串转换(piso)、预驱动(Pre-Drv)、均衡、阻抗匹配与时域与Z域的表达式。

从时域表达式中够可以看出,当C0或C2为负值时,可抑制main cursor上的ISI分量。因此要想起到补偿作用,C0与C2可以同时为负,或者一正一负,但不能同时为正,且三者绝对值和为1。例如C0=-0.1,C1=0.7,C2=-0.2时为去加重,C0=-0.1,C1=1.3,C2=0.2时为预加重。

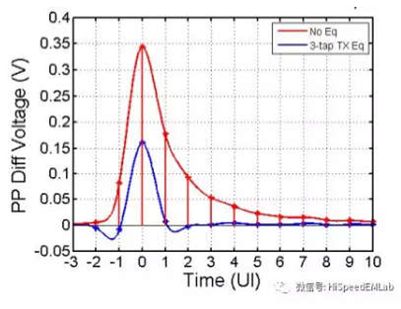

TX端FIR的时域与频域的冲击响应如图所示。左图中蓝色EQ TX曲线中,明显可以看出在-1UI和+1UI处有校正(加权)因子作用,相较于红色曲线更陡峭,也即突出了高频成分。但在0UI处幅值是比原来小,即才用的是去加重。

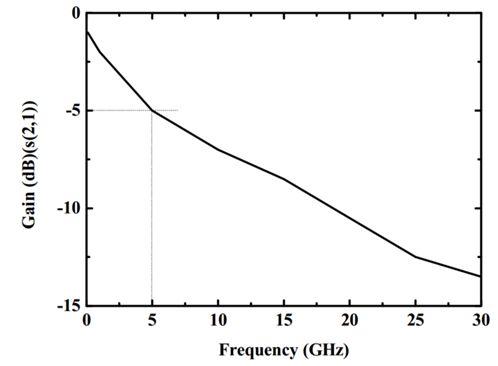

FFE对接收端眼图质量的改善效果,用仿真来说明下。信号速率在25Gbps, 根据图中传输通道S参数可以读出,其通道损耗为-15dB,

FFE相当于在发送端起到高通滤波器的效果,有FFE时,发送波形与接收眼图如下

在长0或者长1之后,下一位变化bit在FFE条件下可以更容易的被识别出来。

4.1.2 RX Equalizer

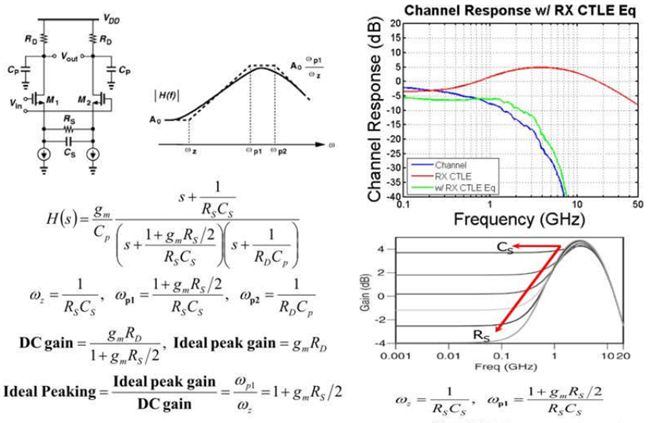

(1)CTLE

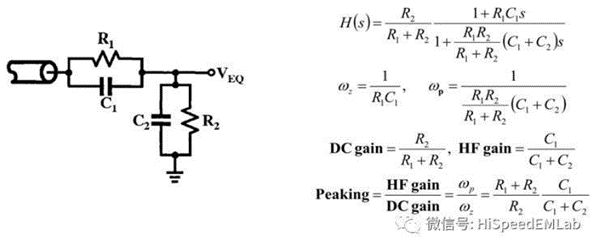

CTLE 是连续时间线性均衡Continuous Time Linear Equalization的简称,是在高速串行链路中常用的一种均衡技术。CTLE本质是一个HFP,实现方式有有源和无源两种。无源的就是一个无源高通滤波器,直流增益由电阻参数决定,交流增益由容性参数决定。有源CTLE则由线性差分放大器构成,RC决定零极点频率,增益由电阻和放大器放大倍数共同决定,极点频率受放大器自身的带宽限制。CTLE的增益补偿一般在10dB左右。

无源CTLE:

Pre-factor =Ideal Peacking是前置系数,Pre-factor= Adcwp1wp2/wz0

wz0是零点,wp1、wp2是极点,Adc由于分压,取值范围为[0,1], 表示频率为0时的直流增益

这四个参数的设置直接影响 CTLE 频响曲线的形状

CTLE 通过提高通道的带宽来提升眼图的质量。如图所示,紫色为无CTLE时的通道频率响应,红色为CTLE本身的频率响应,蓝色为打开CTLE作用后的通道频率响应。

从图中可以看到,蓝色曲线在低频处(2GHz以内)与紫色曲线基本重合,但在2GHz以后直到30GHz范围内,蓝色曲线都在紫色曲线的上方,这表明在高频处,蓝色曲线的衰减比紫色要小。

在CTLE的作用下(红色),频率响应曲线被由紫色移动到了蓝色位置,其增益平坦度比原来好。

若从带宽的角度来看,以3dB带宽为基准,在没有CTLE的时候,带宽只有2.1GHz,打开CTLE之后带宽可以达到6.6GHz,提高了3倍。换句话说,CTLE相当于提高了通道的带宽,这就是为什么CTLE能够使眼图睁开的本质原因。

(2)DFE

DFE为判决反馈均衡Decision Feedback Equalizer,这种均衡技术是非线性的,不会将噪声与串扰随损耗一起放大(与之对应的是线性均衡器会将噪声与信号一起放大),可以有效改善SNR,因此特别适合大噪声的应用场景,其构成是前向FIR+判决器+反馈FIR,对反馈时序和CDR的鉴相要求较高,因此一般与CTLE配合使用,目前常见的CTLE+DFE均衡的最大增益在20dB左右。

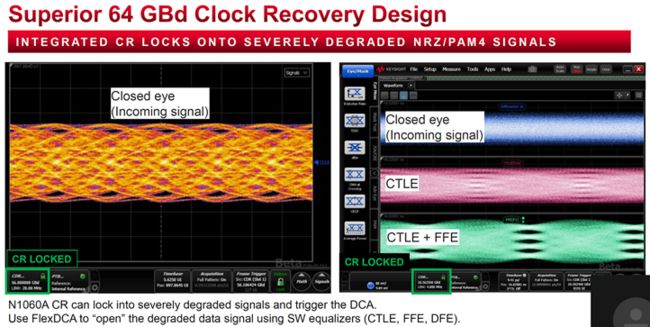

(采样示波器使用CTLE+FFE测试PAM-4信号,改善效果明显)

(3)自适应均衡技术

该技术主要用在RX端,主要通过分析输入到RX端的信号检测出需要补偿的频谱范围,从而自行调节抽头系数和增益,可运用的均衡器主要是FFE,DFE,CTLE等均衡器。

(4)EQ技术选择依据

选择建议供参考,具体要根据实际产品运用场景及Protocol compliance要求来调整,要考虑到连接器,过孔,耦合电容,串扰以及回流焊等带来的损耗。

以Nyquist频点处的插损(Insertion Loss,通常定义为输出端口接收到功率PI与输入源功率之比)为基准:

当channel Insertion Loss在6dB以内,可以不考虑使用预均衡与均衡;

当channel Insertion Loss在6-12dB,建议使用预均衡;

当channel Insertion Loss在12-20dB,建议使用预均衡+CTLE or FFE;

当 channel Insertion Loss在20-30dB,建议使用预均衡+CTLE+DFE;

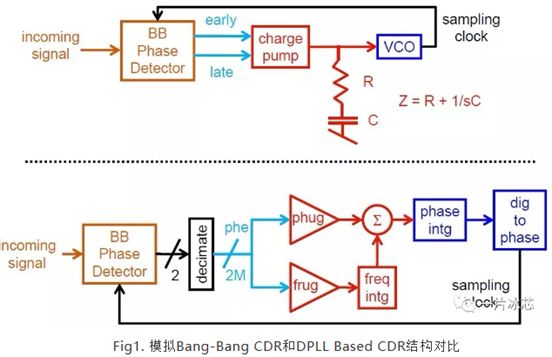

4.2 CDR

为了恢复带有频偏与抖动的TX数据,PX中通常会包含一个CDR(Clock and Data Recovery) 。CDR的功能:通过调整本地时钟的phase完成对带有channel loss和各级模块noise的TX 串行数据的重定时,找到最佳的采样时刻,使RX本地时钟边沿与TX数据中心位置对齐,实现最佳采样,同时减小Jitter。

4.2.1 CDR Classes

CDR分为模拟和数字两大类

模拟CDR大多采用APLL-Based,按照鉴相器类型分为线性和Bang-Bang两种,传函略有区别

数字CDR有过采样(Oversampling)和DPLL-Based结构,过采样对每个UI进行多次采样,可以提高环路带宽和锁定速度,但由于过采样,不适用于高速Serdes,DPLL-Based结构由传统的APLL演变而来,将环路中的部分模拟电路(如模拟滤波器、bang-bang鉴相器 )用数字电路实现,减小功耗、节省面积和PVT影响。

4.2.2 CDR digital

根据运用场景的不同需求,CDR的实现也有多种架构。FPGA的SerDes常常采用基于DPLL的CDR和基于相位插值的CDR。这两种CDR在环路中采用Digital Filter。

CDR环路的特点:

Loop Bandwidth,频率低于环路带宽的抖动会被CDR捕捉然后转移到恢复时钟上,不会引起误码,而高频的抖动分量根据抖动幅度的大小,可能会引起误码。

环路带宽越大,则在上电捕捉阶段能cover的噪声范围更广,锁定时间变短,当然恢复时钟的抖动也越大,反之则锁定时间变长,恢复时钟的抖动也越小。

环路参数的计算可参考:

[1] DPLL-BasedClock and Data Recovery-PPT.

[2] DPLL-Based Clockand Data Recovery-ISSCC.

[3] Sonntag J L,Stonick J. A Digital Clock and Data Recovery Architecture for Multi-Gigabit/sBinary Links[J]. IEEE Journal of Solid-State Circuits, 2006, 41(8):1867-1875

4.3 PLL

SerDes内部需要的时钟是工作在数据波特率上的内部时钟,或者以DDR双边沿采样工作的1/2数据波特率的时钟。但是片外提供给SerDes的时钟频率往往远远低于SerDes需要的时钟频频率,因此PLL被用来倍频产生高频时钟给SerDes使用。例如FPGA的SerDes PLL一般有8x、20x、40x等模式,而PCIe协议工作在5Gbps,则在20x模式下FPGA只需要给SerDes提供250MHz的片外参考时钟,40x模式下只需要提供125MHz的片外参考时钟。

一个三阶PLL电路如图所示,输入信号RCLK phase与参考信号FCLK phase输入到鉴相器中进行比较,相位误差由CP charge pump转化为电压或电流信号,经过Loop Filter后产生控制电压,调节VCO的输出,即调节FCKL的相位,最终使相位误差趋近于0。

PLL的工作过程分为入锁和跟踪。在入锁环节,环路的模型可以用一个非线性微分方程表示,可以评估捕获时间,捕获带宽等指标。在跟踪环节,小信号范围内,PLL的模型是一个常系数线性方程,可以在Laplace域研究PLL的带宽Bandwidth,增益Gain和系统稳定性Stability等性质,小信号模型如图:

PLL 以环路极点的个数来命名环路的阶数。VCO对相位有积分作用(Kvco/s),因此不带Loop Filter的环路称为一阶环,带Loop Filter的环路称为二阶环。一阶环和二阶环都是无条件的稳定系统。但是高阶环路有更多的零点和极点可以独立的调整带宽,增益,系统稳定性,捕获带,捕捉时间等性能。

当环路锁定之后,只有固定的相位差,输入信号RCLK的Frequency与参考信号FCLK的Frequency相等。

对于输入端的噪声,环路是一个低通滤波器,可以抑制高于环路截止频率(-3dB频点)的噪声或干扰。作为SerDes的PLL,希望带宽小一些,以抑制参考时钟的干扰和噪声。

4.4 Channel SI

SerDes Channel关注的频率范围是0Hz到Nyquist频率,也即2倍的信号基频(例如信号速率是5Gbps NRZ, 按照最大基频传输01010101,这样1s内传输2.5Gbit的1,2.5Gbit的0,因此基频为2.5GHz,则Nquist采样频率为5Ghz)。

Channel对信号的损伤包括插入损伤Insertion Loss, 反射reflection,串扰crosstalk,这些参数都可以用S-parameter信道来表示。S-parameter可以用矢网分析仪Vector Network Analyzer测量得到。Channel不是一个纯阻性网络,还包括感性和容性,对不同的频率成分产生的时延也不一样,从而产生和相关的抖动。

未完待续。。。。