★DCDC相关

1.电感选型

饱和电流:电感下降30%对应电流

温升电流:电感产生40℃对应电流

饱和电流>温升电流>输出额定电流*1.3;满载时峰值电流;限流保护点(过流或短路不饱和)

DCR直流等效电阻

自谐振频率:频率之下,电感效应阻抗与频率正相关,频率之上负相关,电容效应,是开关频率10倍以上

留20%以上余量(如实际电流4A,选5A以上)

感值计算:

BUCK

Lmin=2*【Vout*(1-Vout/Vinmax)】/Fsw*Irate

E=dNΦ/dt=Ldi/dt

E:感应电动势

N:匝数

Φ:磁通量

电感电压计算公式:V(t)=L * di/dt--->

V=L*ΔI/Δt(电流变化曲线的时间轴抽象划分为n多个Δt,对应的电流变化量为ΔI)--->

V*Δt=L*ΔI

L:电感系数

t:时间

V:产生的感应电压

di:电感电流峰峰值△iL(电流的微分)

dt:上管开通时间(时间的微分)=D*T

di/dt:电流对时间的导数(理解为电流变化的快慢),单位时间内电流变化情况,不是电流

![]()

电感上电流不能突变

储存的能量不能突变

电流变化率可突变

伏秒定律:

导通阶段电感电压*导通时间(伏秒积)=关断阶段电感电压*关断时间(伏秒积)

导通阶段电感电压*导通时间=L*ΔI(ΔI:导通时间电感电流的变化量)

关断阶段电感电压*关断时间=L*ΔI(ΔI:关断时间电感电流的变化量)

导通时间=占空比*开关周期=占空比*1/开关频率

关断时间=(1-占空比)*开关周期=(1-占空比)*1/开关频率

导通阶段电感电压*导通时间=导通阶段电感电压*占空比/开关频率=L*ΔI

Voff*toff=Voff*(1-D)/fsw=L*Ioff

![]()

加在电感两端电压:Von=Vin-Vout,此时电感由电压Von励磁(提供磁场),电感增加的磁通为Von*Ton

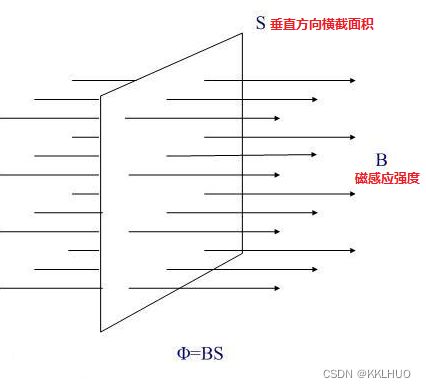

磁通:

磁感应强度B和与它垂直方向某一横截面积S的乘积,叫做穿过这个平面的磁通量,简称磁通,符号“Φ”。

Von*ton=Von*D/fsw=L*Ion

=L*ΔI=L*r*Idc=L*r*Io

L=Von*D/fsw*r*Io

L=(Vin-Vout)*D/fsw*r*Io

Lmin=(Vin-Vout)*Vout/(△I*f*Vin)--->

Lmin=(Vin-Vout)*Vout/(r*Io*f*Vin)--->

Lmin={【(Vin-Vout)*Vout】/Vin}/r*Io*f

L=(Vin-Vout)*D/fsw*r*Io

断开,由于输出电流的连续,二极管导通,电感削磁,电感减少的磁通为Vout*Toff

闭合与断开状态达到平衡,Von*Ton=Vout*Toff,由于占空比D<1,所以Vin>Vout,实现降压功能

Voff*toff=Voff*(1-D)/fsw=L*Ioff

=L*ΔI=L*r*Idc=L*r*Io

L=Voff*(1-D)/fsw*r*Io

L=Vout*(1-D)/fsw*r*Io

Lmin=(Vin-Vout)*Vout/(△I*f*Vin)

Lmin=(Vin-Vout)*Vout/(Irpp*Fsw*Vin)

Lmin=(Vin*Vout-Vout^2)/(Irpp*Fsw*Vin)

Lmin=【(Vin*Vout-Vout^2)/Vin】/Irpp*Fsw

Lmin=【(Vout-Vout^2)/Vin】/Irpp*Fsw--->

Lmin=【Vout*(1-Vout/Vin)】/Fsw*Irpp 【L≥Vout*(1-D)/(△I*Fs)】

最小电感值由输出电压,开关频率所决定

△IL(输出电感上纹波电流)=Irpp

Irpp(电感峰值电流)=0.5*Irate(输出额定电流)

Irpp决定选用电感及输出电容大小

Irpp电流大--->使用大容值低ESR输出电容--->小的输出电压纹波,Irpp电流小--->选择大感值电感,为平衡这矛盾,将Irpp选为额定输出电流的50%

△I(电感峰值电流)=20%~30%*Iout(最大输出电流)

△I(输出电感上纹波电流)=10%~60%*Iout(最大输出电流)

△I=30%~50%*Iout(所需的负载电流)

Lmin=【Vout*(1-Vout/Vinmax)】/Fsw*Irpp--->

Lmin=2*【Vout*(1-Vout/Vinmax)】/Fsw*Irate

电流参数:

流过的最大电流:Imax=Iout+0.5* △I=Iout+0.25* Iout=1.25Iout

MP1470:5V,463mA--->Imax=1.25Iout=578.75mA,△I=0.5Iout=231.5mA--->饱和电流=(Imax+△I)/ 0.8=1012.8125mA

MP1471:3.3V,2635mA--->Imax=3293.75mA,△I=1317.5mA--->饱和电流=5764.0625mA

饱和电流>Imax,温升电流>输出电流Iout

Iout=电源芯片最大输出能力电流(实际留70%~80%余量)

温升和饱和电流>最大电流*1.2(饱和电流>最大输出电流+0.5电感纹波电流)

如输入12V,输出1.2V,2A,开关频率500K,r=0.4

占空比:D=Vout / Vin=1.2/12=0.1

T=1/f

toff=(1-D)* T

L=[(Vout*toff)/ r]/ Iout

L=Vout*(1-D)/ rf I

Ipk(电感电流值)=(1+r/2)*Iout

Ipeak:电感的峰值电流

Ipk=Idc+Ipp/2

=Idc+0.5*{[(Vin-Vout)*ton] / L}

=Idc+0.5* {[(Vin-Vout)*T*DC] / L}

![]()

Lmin=(Vin-Vout)*Vout/(△I*f*Vin)

=(12-1.2)*1.2/ (2*0.3*500K*12)

=12.96/ 3600K

=0.0036K

=3.6uH

L=3.6uH*1.25=4.5uH

选4.7uH

△I=0.45A(23%)

Imax=2+0.45/2=2.225A

经验:最大电流+△I < 饱和电流*0.8

(2.225+0.45)/ 0.8=3.3A

选顺络饱和电流4.97,温升电流3.3A

Boost:Lmin=2【Vin*(1-Vin/Vout)】/Fsw*Irate;20%精度,5%设计裕量,L=(1+20%+5%)*Lmin=1.25*Lmin,选稍大的标称电感

如输入4.2V,开关频率1.2MHZ,输出电流500mA,输出电压5V

L=2.24uH*1.25=2.8uH

比2.8uH稍大标称电感为3.3uH

Imax=Iout+0.5* △I=Iout+0.25* Iout=1.25Iout=1.25*0.5A=0.625A

选电感量3.3uH,饱和电流>0.625A功率电感,顺络的叠层功率电感

饱和电流和温升电流中较小值进行设定

回路中的额定电流,且是额定电流的1.5倍以上,如图

![]()

叠层比绕线散热性好,损耗小,ESR值更小,成本较低,绕线耐电流>叠层耐电流

带屏蔽(屏蔽罩或磁性胶水涂覆)罩好,改善EMI

电容下列公式来选择:

I=C * dv/dt

C=I/(dv/dt)

C=I*(dt/dv)

整理后可得:

C≥2*△I/(8*Fs*△V)

△V:纹波电压

△I:峰对峰电感电流

假设电容串联阻抗可忽略,如陶瓷电容,乘数2代表直流偏压造成的电容值下降

2.减小噪声纹波

加大输出电感和电容

二级滤波,再加一级LC滤波器

降低输入前端低频纹波:增加滤波,电容电感滤波电路LC,π型,前端及后端增加稳压器

电源输出之后接LDO滤波(输出电压恒定,不改变原有反馈系统)

二极管后接电感(EMI滤波,抑制高频噪声,针对产生噪声的频率,选择合适的电感)

输出二极管后再接一个π型线路进行滤波,比LC滤波效果好一点,称CLC滤波器

在二极管上并电容C或RC

![]()

3.输入电压范围及输出电流

输入12V,输出3.3V和2635mA--->MP1471_4.7-16,500K,2.5A同步,4.7UH

输入12V,输出5V和463mA--->MP1470_4.7-16,500K,2A同步,2.2UH

电流降额80%

4.选型

输入输出电压

输出电流(负载电流大小)

开关频率

效率:轻载影响待机功率,重载影响温升

瞬态响应:要求输出电压波动越小越好,一般按峰峰值10%以下要求,实际要注意按推荐值选用反馈电容,常见取值在22p到120pF

5.LAYOUT

加粗地线宽度或接地铜皮面积,不同层多打地孔

反馈电阻靠近FB,到FB引脚要短

输入端地和GND引脚短而粗

输入端电容和IN引脚短而粗

干线SW,磁性元件,开关管,功率二极管噪声源远离敏感模拟区域(如FB)

电感靠近芯片的SW,输出电容靠近电感放置

6.开关频率影响

优:体积小,瞬时响应快,电压过冲下冲小

频率↑--->输出电容电感小--->节省电路板面积

频率↑--->电感圈数↓--->直流阻抗↓

频率升高后,电感在一个开关周期所需要存储释放的能量也就减小,因此不需要太大的电感值

频率*2,其他不变--->ton和toff减少一半--->伏秒数减少一半--->△I(单位电感量的伏秒数)减少一半--->r=△I/Idc减少一半(Idc没变)

仍要纹波系数保持,因频率加倍而减少一半的△I也增加一倍,实现的方法是使电感量减少一半

电感能量处理能力(与电感的体积相关)为1/2*L*Ipk^2,L减少一半,Ipk不变,所需电感体积也减少一半

峰值电流不变,所需电感额定电流与频率无关

频率↑--->纹波↓(纹波要求不变,频率增大,电感值相应可以减小)

不同频率电容值和电感值:

![]()

劣:效率低,热量多

频率↑--->负载周期↓--->电压↑(需求低电压点无法达到,如处理器核心电压降到1V以下)

最小导通时间:

负载周期(占空比)=mos导通时间/整个开关周期=Vout/Vin

最小占空比=最小导通时间*开关频率

最小输出电压=输入电压*最小占空比(不低于参考电压)

最小导通时间150ns时最小输出电压:

直流电源转换器提供更低输出电压,必须省略部分脉冲,降低输入电压或减少开关频率,选择开关频率前,最小导通时间符合要求

驱动脉冲不够快,无法达到占空比,会省略部分脉冲(脉冲跳跃)以提供所需低电压,纹波电压因脉冲间隔变大而升高,输出纹波会出现次谐波成分,带来噪声,限流电路无法正常操作,组件不会对大电流突波做出响应,有时控制器不能工作,控制回路不稳定

潜在问题:省略脉冲(脉冲跳跃)和噪声,最小导通时间,误差放大器增益频宽,mos阻抗和开关功耗

效率与功耗:

频率↑--->效率↓--->耗电↑--->散热片或扩大铜箔面积(开关频率每增加1倍,效率降低2%)

影响因素:

功耗:mos驱动功耗,mos开关功耗,电感功耗,mos阻抗与组件功耗,电容功耗(可忽略,使用等效串联阻抗很小的陶瓷电容)

5V输入1.8V输出效率:

![]()

改善各频率下效率,选择低导通阻抗,低栅极电压,满负载时静态电流小的直流电源转换器,等效阻抗更小的电容和电感

组件尺寸:

电容和电感焊盘面积>个别组件,个别零件使用面积加在一起(ic,滤波器,电阻和电容焊盘面积),然后乘以2以便容纳组件距离,得到所需总面积

频率↑--->滤波器↓--->电路板面积↓

瞬时响应:

电源供应波德图,相位边限制在45-55度之间,提供 良好阻尼瞬时响应

![]()

瞬时响应时间和相关电压峰过冲值

![]()

交越频率约为开关频率的1/8,放大器频宽足以支持高交越频率,放大器增益频宽典型值为5MHz

穿越频率↑--->带宽↑(环路带宽变宽)--->负载响应↑,线电压响应↑;穿越频率≤工作频率/2

带宽越宽,越容易引入噪声,系统稳定性越差

频率↑--->过冲↓(频宽变大)--->稳压精度↑(要求包含瞬时电压值在内的稳压精确度达到3%)

多个功率级电路并联,再以不同相位,得到高开关频率,如4组500KHz开关频率输出接在一起,得到2MHz有效频率(减少纹波,缩小输入电流容量,加快瞬时响应,功率分散到整张电路板更好散热)

器件限制:接通延迟时间,上升时间,关断延迟时间,下降时间

![]()

开关损耗:开关损耗限制

![]()

开关功率损耗=每个开关产生的能量损耗*开关频率

开关频率↑--->开关损耗↑,注重效率不可接受

磁性元件损耗:

绕组的趋肤效应和临近效应,绕组的涡流损耗增加,迟滞损耗增加

高频引起问题:

电路寄生参数影响电路性能,如变压器一次侧和二次侧,寄生电容,变压器漏感,PCB布线之间的寄生电感和寄生电容引起振动和EMI问题

非隔离buck开关频率从400K~3M不等,用的最多在1M左右

频率↑--->电容高频特性要求高

频率↓--->电容容量有要求

7.测试项目

电气性能测试

负载变化快:CPU和GPU核电压

负载变化慢:普通IO电压

示波器:耦合方式为交流耦合,量程为20mV每格点,带宽设为20MHz,阻抗为1MΩ

测试项目:

输入电压不变,不同负载电源纹波(负载电流调整率:电流从0到最大电流跳变,输出电压变化率,单位是%/A)

从0到3A因为芯片控制模式为PWM和PFM/PSM,在两者切换时存在较大纹波变化

输出负载不变,不同输入电压纹波(线性负载调整率:额定负载下输出电压随输入电压变化而发生的变化率)

输入电压不变,设定大负载变化,测试动态响应

电子负载设定在动态输入,具体负载变化为0-3A,斜率为3A/uS,改变不同负载值及不同变化斜率,示波器观察并记录纹波值

TI:纹波为-60mV

国产拓尔:纹波为84mV

过压保护

过流保护

静电防护

其他测试:效率(电源功率计测试),温升,器件封装,绿色,焊接

开尔文测试法:

注意:

连线:线损越小越好,直径1mm多股铜线最佳,以免造成过大压降,负载电流较大时,缩短输出引脚与各负载间距离,增加导线截面积减小过大压降

采用单通道探头直接测量法测试输出,避免输入输出共地和外界干扰产生测量误差

确保前级供电限流合理,输出容性负载≤技术手册规定值

线性电压调整率:

如额定负载600mA,输出电压5.01V(最大输入电压,额定负载),输出电压5V(最小输入电压,额定负载),输出电压5.01V(标称输入电压,额定负载)

线性电压调整率=[(5-5.01) / 5.01]*100%=-0.2%

负载调整率:

负载调整率=[(a-b)/b]*100%

a=a1和a2中偏离b最大值

a1=输出电压(标称输入电压,10%负载)

a2=输出电压(标称输入电压,100%负载)

b=输出电压(标称输入电压,50%负载)

输出电压精度:

如输出设定电压12V(标称输入电压,满载),额定负载144Ω,测试输出电压12.039V(标称输入电压输出电压)

输出电压精度=[(12.039-12)/ 12]*100%=0.325%

交叉调整率:

双路或多路输出,主路输出端取样电压形成闭环控制回路,主路负载电流变化对其输出电压影响不大,辅路电压是通过变压器耦合得到的,主路,辅路负载电流变化都会导致辅路输出电压变化相差比较大,双路或多路输出每路输出负载一定要平衡应用(负载平衡度最好不超过5%),否则会导致输出电压和负载调节率超出精度范围

交叉调整率=[(a-b)/ b)]*100%

a=其他一路带载10%输出电压(主路带载100%);其他一路带载100%输出电压(主路带载10%)

b=其他一路带载50%输出电压(主路带载50%输出电压)

效率:

如标称输入12V,100.7mA,满载输出11.951V,83.6mA

η(艾塔或伊塔)=[(0.0836*11.951)/ (0.1007*12)]*100%=82.68%

外壳温升测试

用热成像仪或热电偶

温升=壳温-环境温度(外壳温度50℃,环境温度25℃,温升=25℃)

输入反射纹波电流:

滤波器未滤除完全的纹波电流反射到输入端的交流分量,输入反射纹波电流测量需要在前端接入电感和电容元件来匹配源阻抗

![]()

启动时间:

输入开启后输出相对于输入达到目标电压值时响应延迟时间,额定满负载下测得,外接滤波器(包括输入输出电容)均会大大延迟启动时间

纹波和噪声:

纹波和噪声采用峰-峰值计量(mVP-P)

第一,示波器带宽设置为20MHz,可以有效防止高频噪声

第二,采用平行线测试法,双绞线或靠测法

平行线测试法:

![]()

双绞线法:

![]()

在Vo与0V之间接上阻性负载(假负载),在双绞线末端接一个10uF电解电容,在测量点连接时,一端接在Vo上,另一端接到地平面端

示波器靠测法:

![]()

示波器地线夹会吸收各种高频噪声干扰测量结果,为屏蔽干扰采用靠测法,示波器探头接在每路输出端测试

实测:

![]()

安规测试:

产品认证中对产品安全的要求,如强制认证CCC

项目:

限功率电源测试

限流源测试

电容放电测试

输入测试

高压测试

温升测试

潮湿测试

高低温试验

漏电流测试

耐压测试

接地电阻,连续测试

绝缘阻抗测试

电源线拉力测试

稳定性测试

插头扭矩测试

外壳受力测试

跌落测试

应力释放测试

电池充放电测试

球压测试

元器件异常测试

过载测试

滚筒跌落试验

7大安全:防电击,能量危险,防火,热量危险,机械危险,辐射,化学危险

常规测试项目:

功率因素和效率

平均效率

输入电流

浪涌电流

电压调整率

8.电感过大过小影响

![]()

Fsw:开关频率

电感值↑--->Ripple↓(即电流越稳定,EMI辐射干扰↓)

电感值↑--->瞬时反应↓(电流变化跟不上电压变化;电感阻碍电流变化)

可能:

开关关闭--->电流还在上升阶段

开关打开--->电流还在下降阶段

自我谐振频率:

自我谐振频率>10*切换频率

如:切换频率2.5MHz,自我谐振频率大于25MHz

电感值↑--->谐振频率↓(越难达成上述目标)

内阻:

电感值↑--->绕圈数↑,内阻↑--->转换效率↓,IR Drop(电压降)↑

![]()

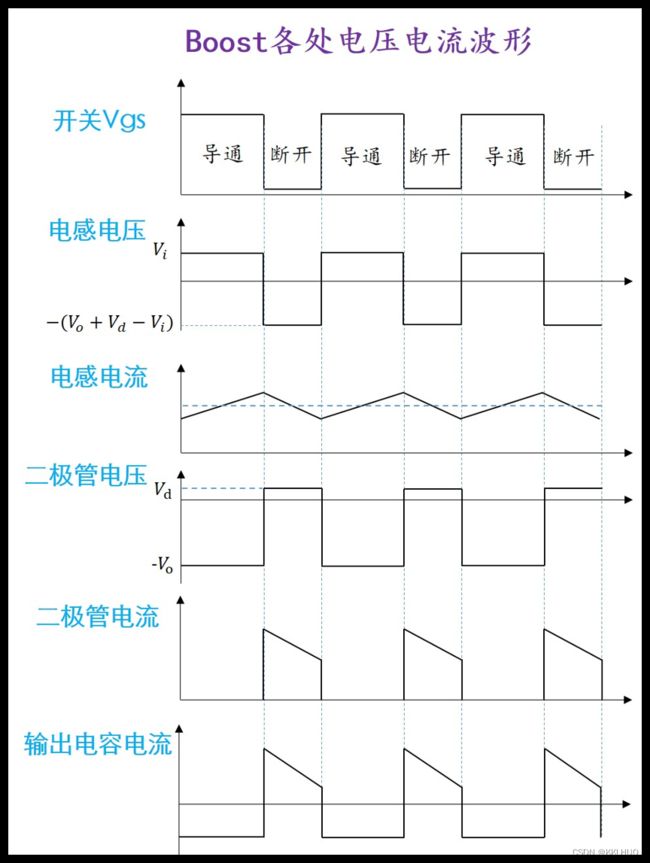

9.1个周期各元器件电压电流波形

![]()

![]()

MOSFET导通,输入电压给电感和电容充电,通过它们把能量传递给负载,在此期间,电感电流线性上升

MOSFET断开,输入电压断开与电感的连接,电感和输出电容为负载供电。电感电流线性下降,电流流过二极管

MOSFET的导通时间定义为PWM信号的占空比(D)。D把每个开关周期分成[D × tS]和[(1 - D) × tS]两部分,它们分别对应于MOSFET的导通时间(环路1)和二极管的导通时间(环路2)

10.输出纹波范围

输入5V,输出1.8V,3A--->最多20mV纹波电压_(也叫峰值,大约输出电压1%)

CPU供电电源(1.2V,0.8V)--->30mV以内(CPU内核和DDR供电电压50mV大小)

纹波表示:有效值,峰值,绝对量,相对量

如:电源稳压状态,输出100V,5A,测得纹波有效值10mV(绝对量)

相对量:纹波系数(纹波率)=纹波电压/输出电压=10mv/100V=0.01%(万分之一)

纹波与噪声:

![]()

纹波:开关过程,电能从输入端到输出端,在输出电容形成充电和放电过程,造成输出电压波动,波动频率与开关频率相同,波动时输出纹波(开关电源运行时功率开关管动作时产生的,由于功率开关管是通过PWM进行控制产生的脉冲电流,然后通过滤波电感和电容产生直流电,因此在输出电压会存在和开关频率一致的纹波,主要是开关噪声)

噪声来源:SWITCH的开关,电感中电流也是在输出电流 的有效值上下波动,所以在输出端也会出现一个与SWITCH同频率的纹波

开关电源输出纹波来源5方面:

输入低频纹波:

输出电解电容容量受限,导致输出低频纹波残留,整流滤波电路输出直流电压中含有沟通低频纹波,该沟通纹波经DC/DC改换器衰减后,在输出端表现为低频噪声,选用前级预稳压和增大改换器闭环增益来消除

高频纹波:

来源高频功率开关切换电路

功率器材开关过程中发生的超高频谐振噪声:

来源于高频整流二极管反向恢复时二极管结电容,功率器材开关时功率器材结电容与线路寄生电感的谐振,经过选用软恢复特性二极管,结电容小的开关管和削减布线长度削减超高频谐振噪声

闭环调理操控引起的纹波噪声:

闭环调理器参数不适当引起的输出纹波增大:

调理器输出添加对地补偿网络,可抑制调理器自激引起的纹波增大

选闭环调理器开环扩大倍数和闭环调理器参数,开环扩大倍数过大会引起调理器振荡或自激,增大输出纹波,过小开环扩大倍数使输出电压稳定性变差及增大纹波,调试中根据负载情况进行调理

反馈通道中不添加纯滞后滤波环节,使延时滞后降到较小,以添加闭环调理的快速性和及时性,对抑制输出电压纹波有利

闭环调理操控引起的纹波噪声:

输出电压进行闭环控制,调理器参数规划不适当引起纹波,当输出端动摇时经过反馈网络进入调理器回路,导致调理器自激振荡,引起附加纹波

纹波主要来自工频50Hz变压器,纹波电压频率是50nHz,n取自然数,大小取决于整流电路类型,半波整流是1,全波整流是2,三相全波整流是6(即300Hz),幅值小,轻易滤掉,纹波可做到几mV

![]()

噪声:自身产生高频脉冲串,发生在开关导通与截止瞬间产生尖脉冲所造成,噪声频率比开关频率高的多,噪声电压大小与电源拓扑,变压器绕制,寄生参数,测试外部电磁环境,PCB布线有关

纹波噪声大影响运放精度,干扰AD或DA工作

纹波电压对高放,本振,混频,滤波,检波,A/D变化等电路都会产生影响

噪声来源3方面:

芯片本身输出不恒定,有纹波,只能接受

无法实时响应负载对于电流需求的快速变化,通过感知其输出电压的变化,调整其输出电流,从而把输出电压调整回额定输出值(负载电流变化频率低,很好做出调整,保持输出电压稳定,负载瞬态电流变化频率高,出现跌落,产生噪声)

负载瞬态电流在电源路径阻抗和地路径阻抗上产生的压降,引脚及焊盘有寄生电感,瞬态电流流经产生压降,负载芯片电源引脚处电压会随着瞬态电流变动而波动,是阻抗产生的电压噪声,在电源路径表现为负载芯片电源引脚处的电压轨道塌陷,在地路径表现为负载芯片地引脚处的电位和参考电位不同

MOS导通和截止时候,都会有一个与SWITCH上升下降时间频率相同或奇数倍频的噪声,一般为几十MHz

二极管在反向恢复瞬间,其等效电路为电阻电容和电感串联,会引起谐振,产生噪声频率为几十MHz,这2中噪声一般交高频噪声,幅值比纹波大很多

共模噪声(寄生参数引起的共模纹波噪声):开关电源功率器件使用外壳作为散热器,产生等效电容导致

功率器材与散热器底板和变压器原,副边之间存在寄生电容,导线存在寄生电感,当矩形波电压作用于功率器材时,输出端发生共鸣纹波噪声,减小与操控功率器材,变压器与机壳地之间的寄生电容,并在输出侧加共模抑制电感极电容,可减小输出共模纹波噪声

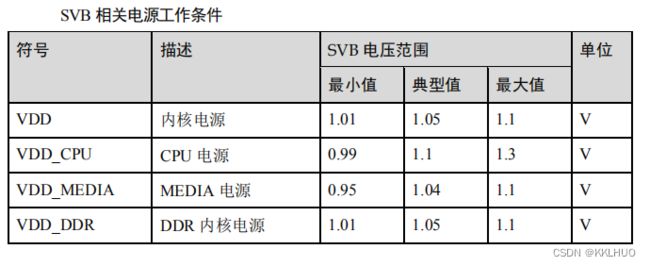

Hi3516A:

core电源有4种:

Media(Media电源):1.1V,≥2A

DDR(DDR内核电源) :1.1V,≥1A

CPU(CPU电源):1.1V,≥1A

VDD(内核电压):1.1V,≥1A

11.保护

输入保护电路有过流保护,过压保护,浪涌抑制,对电压冲击,EMC有重要作用

FUSE:选具有安规认证的慢断保险丝,推荐值5W以下1A/250V,10W-15W(2A/250V),20W-60W(3.15A/250V)

额定电流过大起不了作用,过小容易因起机时输入电容充电引起误熔断

只有过流保护作用,保险丝实际熔断电流=额定电流*1.5

MOV:压敏电阻,输入浪涌电压保护(保险丝,压敏电阻形式有过压,过流保护功能,有些具有防雷击保护)

![]()

压敏电压高于用户正常工作电压,并留有一定余量

通流量大于防雷电路设计的通流容量

根据应用端口,防护等级选压敏电阻和二极管

熔断电阻器与保险丝作用相同

![]()

过压保护:保护后续电路免受甩负载或瞬间高压破坏

过压器件作用方式不同分为钳位型和开关型

开关型(防雷器件):陶瓷气体放电管,半导体放电管,玻璃放电管

陶瓷气体放电管:单独使用,弧光压(电离的气体(空气)在带电体和地之间或带电体之间的短路)>用户正常工作电压,并留有一定余量;与MOV配合使用,直流击穿电压>用户正常工作电压,并留有一定余量,通流量大于防雷电路设计的通流容量

半导体放电管:信号接口电平 玻璃放电管:直流击穿电压高于用户正常工作电压,通流量大于防雷电路设计的通流量容量 钳位型:瞬态抑制二极管,压敏电阻,ESD放电二极管 NTC:热敏电阻(负温度系数,阻值随温度升高降低),减少启动过程中冲击电流(抑制浪涌电流能力),输入功率大,选绕线电阻 C1:滤波,高频低阻电解电容,电容耐压降额80% C2:陶瓷,去除高频噪声,推荐值1uF/50V :TVS:模块异常时保护后级电路 双路或三路输出,输入应用电路相同,输出看做2个或3个独立变压器选择滤波参数 防反: 二极管防反 二极管单向导电性 优:方法简单,安全可靠,成本低 劣:输出端有0.7V压降(安森美快速恢复二极管);电流过大,损耗高(2A电流,1.4W损耗),发热大(要加散热器);反向电压稍微偏大,并未完全截止,有比较小漏电流通过,使用时需留足余量 PMOS管防反 刚上电时,MOS管寄生二极管导通,S极电压为VCC-0.6,G极为0,PMOS导通 当电源反接时,G极为高电平,不导通 实际应用中PMOS的GS之间再加一个电阻比较好,这种方法也有PMOS和NMOS之分,都是利用MOS管寄生二极管以及导通性,NMOS导通电阻 整流桥防反 桥式整流电路,无论什么极性都能工作,导通后有2个二极管压降,发热是二极管防反2倍 保险丝+稳压二极管防反 当电源Vin接反时,稳压二极管D1正向导通,负载的负压为二极管的导通电压Vf,Vf一般比较低,不会烧坏后级负载电路,同时,Vin反接时,D1正向导通,电压主要落在F1上,因此开始时电流会迅速上升,直至超过F1的熔断电流,保险丝F1熔断,电源断开,不会因为电流过大而烧坏D1 当电源Vin输入比较高时(比如大于稳压管的5.6V),因为稳压管D1存在,所以负载端获得电源约为5.6V,那么F1上就会有比较大的电压(Vin-5.6V),电流会上升比较快,直至F1熔断,电路获得保护 保险丝: 熔断电流>后级负载正常工作电流(正常使用时不能熔断) 稳压二极管: 稳压值>正常Vin电源输入(正常电源输入时不能击穿稳压),稳压值<后级能允许最大输入电压(稳压值不能烧坏后级电路) 最大允许电流+上电时负载电流>保险丝击穿电流(如果不满足此条件,电源过压输入时,在保险丝击穿之前,稳压管会因为通过的电流过大而烧坏) 反接电路时负压Vf<1.5V,后级电路应能允许接入1.5V负压不会烧坏 此电路应用于功率比较小电路中,小于500mW EMC滤波电路: 辅路输出电压精度受负载影响大,,要求负载比例平衡,如满载主路900mA,满载辅路100mA, 实际主路负载90mA,辅路10mA 对辅路电压精度要求较高时,加LDO(主要应用于辅路负载较轻,导致输出电压升高场合) 静电保护: 雪崩二极管:信息线并联雪崩二极管到地,利用雪崩二极管快速响应并且具有稳定钳位的能力,可以在较短的时间内消耗聚集的高电压 高压电容:将耐压至少为1.5KV的陶瓷电容放置在I/O连接器或信号位置,同时连接线尽可能短,减小连接线的感抗 铁氧体磁珠:衰减ESD电流,且抑制辐射 火花间隙法:铜皮构成微带线层使用尖端相互对准的三角铜皮构成,三角铜皮一端连接在信号线,另一个三角铜皮连接地,当有静电时会产生尖端放电进而消耗电能 LC滤波器:减小高频静电进入电路,电感的感抗特性能很好的抑制高频ESD进入电路,而电容又分流了ESD高频能量到地,还可以圆滑信号边缘 多层板:完整的地平面靠近走线,使ESD更加快捷的耦合到低阻抗平面上 电路板外网留保护带:在电路板周围画出不加阻焊层的走线,条件允许走线连接至外壳,走线不能构成一个封闭的环,形成环形天线 有钳位二极管的CMOS器件或TLL器件:利用隔离原理进行保护![]()

![]()

![]()

![]()