手把手教你蜂鸟E203自测试用例

1.准备好编程环境,推荐使用VMware虚拟机,在虚拟机中安装Linux操作系统。在Linux操作系统的众多版本中推荐使用Ubuntu 18.04版本的Linux操作系统。

2.运行以下命令安装测试用到的工具包

sudo apt-get install autoconf automake autotools-dev curl device-tree-compiler libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev git3.下载e203_hbirdv2项目到Linux环境中。有两种方法:

方法①:在Linux终端中,运行以下命令,直接就可以下载到Linux的桌面上。

git clone https://github.com/riscv-mcu/e203_hbirdv2.git

方法②在github官网上直接下载e203文件夹到windows系统下,然后拖到Linux系统中。进入github的步骤如图所示

4.由于编译汇编程序需要用到GUN工具链。可以到芯来科技官方网站的文档与工具页面中下载“RISC-V GNU Toolchain”,下载最新的即可,得到压缩包然后解压,拖到Linux操作系统中。

5.运行以下命令配置工具链:

cp nuclei_riscv_newlibc_prebuilt_linux64_2020.08.tar.bz2 ~/

cd ~/

tar -xjvf nuclei_riscv_newlibc_prebuilt_linux64_2020.08.tar.bz2

cd ~/project/e203_hbirdv2

mkdir -p ./riscv-tools/prebuilt_tools/prefix/bin

cd ./riscv-tools/prebuilt_tools/prefix/bin/ # 建立riscv gcc的链接

ln -s ~/nuclei_riscv_newlibc_prebuilt_linux64_2020.08.tar.bz2/gcc/bin/* .注意标红的是下载的GNU工具链解压以后的文档名,可以自行修改换成解压以后的文档名。

运行代码后可能会出现错误:“Syntax error:Bad fd number”。这个错误可能是由于在Ubuntu 18.04中/bin/sh被链接到了/bin/dash 而不是/bin/bash。如果出现如此错误,用以下命令修改即可。

sudo mv /bin/sh /bin/sh.orig

sudo ln -s /bin/bash /bin/sh6.运行以下命令进行编译

cd ~/project/e203_hbirdv2/riscv-tools/riscv-tests/isa

source regen.sh注意:此操作过程只是为了运行蜂鸟e203自带的测试用例,不修改任何的汇编测试程序的源代码,直接运行此source.regen.sh时,Makefile认为没有更新,什么都不用做(显示“make:Nothing to be done for defaule”),显示如此就是编译成功。

7.下载iverilog仿真工具。

蜂鸟E203处理器的仿真环境支持VCS和iverilog两款工具,因此在运行仿真前,请确保运行环境中已安装VCS或者iverilog仿真工具,若安装iverilog仿真工具,请确保其版本号为V12.0。这里推荐使用iverilog仿真工具,安装步骤如下:

# 从github下载

git clone https://github.com/steveicarus/iverilog.git

#进入iverilog目录

cd iverilog

#检测依赖文件、配置环境并编译

sh autoconf.sh

./configure

make

#运行测试demo检查是否编译成功

make check

#安装iverilog

sudo make install

#查看iverilog的版本

iverilog –v

8.编译RTL代码

使用如下命令进行编译

cd /vsim //进入e203_hbirdv2项目所在文件夹下面的vsim目录

make install //运行该命令会在vsim目录下生成一个install子文件夹,在其中配置仿真需要的文件

make compile SIM=iverilog

//选择iverlog工具,编译处理器核和SoC的RTL代码

//若选择VCS工具,则将上述命令中iverilog改为VCS 9.运行默认的一个测试用例。

使用如下命令

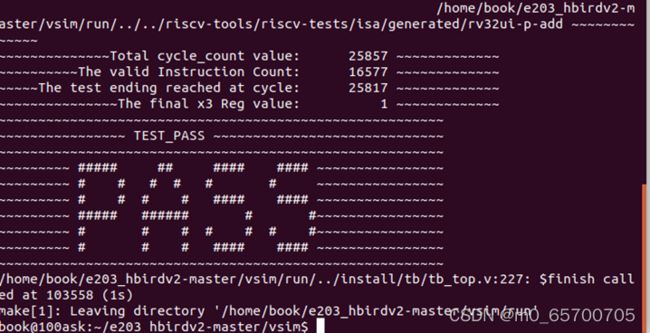

make run_test SIM=iverilog //选择VCS工具,运行仿真测试运行成功以后终端显示结果如下图所示:

此测试用例只运行其中的一个默认测试用例。

10.运行所有回归(regression)测试用例,并查看回归结果。

make regress_run SIM=iverilog //逐个运行回归测试用例

make regress_collect //查看回归测试结果至此蜂鸟e203自测试用例就运行完成。