数字IC后端流程——(一)数据准备Data Setup

原文转自:https://blog.csdn.net/weixin_46752319/article/details/107252336

ICC数据准备文件

主要基于ICC_lab2010的学习 查找资料的总结

-

非库文件:

·ICC启动环境设置文件:.synopsys_dc.setup

·Verilog门级网表

·时序约束文件.sdc

-

库文件:

·milkyway参考库(ref文件)

·标准单元库(.db)

·寄生参数库(.tlup/.itf)

·工艺库文件techfile(.tf)

·ICC启动环境设置文件:.synopsys_dc.setup

该文件与DC启动相同,放在ICC启动目录下,需自己编写。软件在启动时会自动加载search path、target_library、link_library这些库及其他设置。比如:

·设置一些常用的关联命令

·逻辑库设置(设置search_path ,target_libr,link_library,设置min库:包括标准单元库、IO库、ram库)

·定义一些变量,这些变量内容是不同路径下一些文件的名称

·Verilog门级网表

该文件是我们输入的设计文件,由DC或其他综合软件综合后输出的门级网表形式的Verilog(.v)文件。

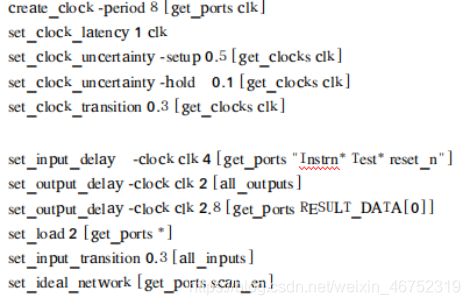

·时序约束文件.sdc

时序约束文件也是由DC进行综合输出的.sdc格式的文件,其中包含对设计的时序约束条件。

·milkyway参考库(ref文件)

ICC使用的库是milkyway形式的库,该库由milkyway软件生成。

信息是以被称为“views”的形式存储的,例如:

CEL:完整的版图信息

FRAM:用于布局布线的抽象化的版图物理信息(只有单元大小、端口名称、端口位置等简单的物理信息)

LM:带有时序和功耗信息的逻辑模型(可选*),该文件对于后端布局布线不是必须的,IC Compiler只通过link_library变量来读取指定的(.db)格式的逻辑库。

其余还有PWR、TIM等,一般ICC使用的是FRAM views

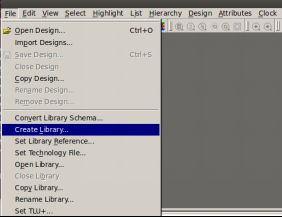

对于一个设计,启动ICC后,第一件事就创建设计库create_library

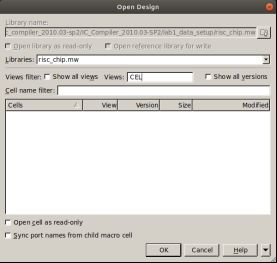

path和name自己设置,Technology file选择.tf格式的工艺文件,reference libraries中选择的即为设计中需要用到的std cell 、IO、RAM等的milkyway库,点击ok完成library的创建。这个library不仅包含设计的参考库,也包含设计本身,即设计保存后也储存在该library中。

在学习lab的过程中我与smic18的库进行了对照学习,我的smic18标准单元库是网上下载的,milkyway库有一点问题。于是我也自己学习了一下使用milkyway(这里指milkyway软件,后面以MW区分)生成参考库。

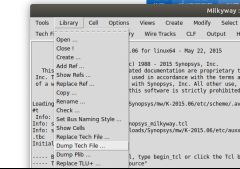

首先,工艺文件.tf文件可以由参考库dump获得:

file name自己设定,library选择smic18的milkyway库,在MW的工作目录下生成一个.tf文件。

接着创建milkyway库,GUI>Library>Create

勾选Set Case Sensitive。GUI>Library>Open打开创建的library

导入lef文件,GUI>Cell Library>LEF In

工艺库目录下的lef目录包含了工艺相关的.lef文件(library exchange format),库交换格式,描述了库单元的物理属性,包括端口位置、层定义和通孔定义。包含了工艺的技术信息,如布线的层数、最小的线宽、线与线之间的最小距离以及每个被选用cell,BLOCK,PAD的大小和pin的实际位置。由lef文件可以获得FRAM view。

可能会遇到报错:Error: No Tech or Cell LEF file name is specified. (MW-013)

在MW的点击左下角的Scheme,切换到Scheme模式,然后输入read_lef,这样就能弹出Read LEF窗口。

在tech lef file中选择.tf文件(或者tech.lef),Cell LEF file中选择标准单元库的.lef文件

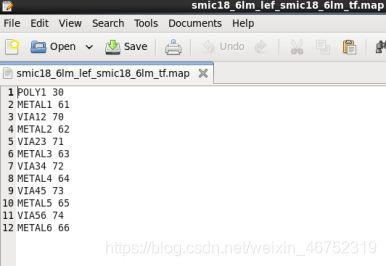

而Layer Mapping文件是.tf和.lef的映射文件,可以自己写,或使用脚本文件提取。

在网上下载了lef_layer_tf_number_mapper.pl脚本文件将.tf和.lef中的信息提取出来,能够获得一个.map文件

文件设置完毕后点击ok开始LEF的导入,在创建的library下生成FRAM view。

可能出现错误Error: DATABASE unit (2000) specified in LEF/PLIB file is greater than legth precision in library (1000). (MWLIBP-102)

解决方案:打开你所用的lef文件,找到DATABASE MICRONS 2000,修改为DATABASE MICRONS 1000,重新开始生成库。

另外,若在ICC中inport design的时候出现错误

Error: Module 'XXX' is not defined.

Error: Verilog parser cannot parse the xxx.v source file. (MWNL-047) No such file or directory

Error: Current design is not defined.

网上查阅大多原因是由于工艺库压缩包在windows环境下解压,CELL的文件名为XXX_1或xxx_2,将其改为xxx:1或xxx:2可解决。

·标准单元库(.db)

用于提供STD Cell、IO、Macro的时序、功耗、面积等信息。这里不同于之前的Astro需要根据已有的库文件生成LM View、TIM View、PWR View,ICC可以直接用Design Compiler使用的db文件,因此方便了设计,简化了设计的复杂度。

·寄生参数库(.tlup/.itf)

寄生RC查找表,ICC使用网络几何形状以及该文件来计算互联电阻电容。

若tluplus文件没有时,可由Foundry给的.itf转成tluplus。其中.itf文件全称是Interconnect Technology Format。

用Synopsys公司的Star-RCXT

> grdgenxo-itf2TLUPlus -i

ICC中设置TLU+文件 GUI>File>Set TLU+

这里的map文件与前面相同。

简单说一下ICC读入设计的步骤

①首先按前面叙述的操作create library

②open library

找到刚刚创建的library打开

![]()

③open design/ import design

如果你的library是按上述操作新创建的,library中没有CELL存在

GUI>File>Import Design

输入verilog格式的网表文件 db文件和ddc都是DC输出的,其中会带有时序约束的信息,最好以verilog格式创建。点击ok之后

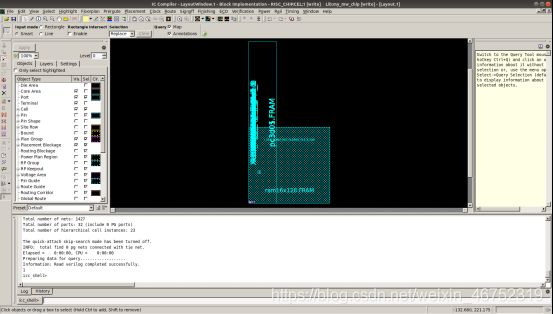

设计中的Macro的标准单元都被摆放在坐标原点 console窗口显示read successfully

④设置TLU+文件,读入SDC文件

TLU+设置前面说过。读入SDC GUI>File>Import>Read SDC

⑤设计合理性检查

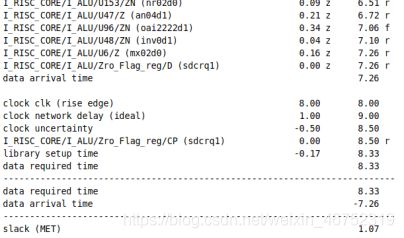

读入sdc时序约束后 Icc_shell>set_zero_interconnect_delay_mode true

设置0互联延时,最理想的情况下报告时序,此时应不存在setup的违规,如存在,则返回前端进行修改设计。

Icc_shell>set_zero_interconnect_delay_mode false

最后 保存设计

save_mw_cel -as xxxxx