HNU-电路与电子学-实验3

实验三 模型机组合部件的实现(二)(实验报告格式案例)

班级 计XXXXX 姓名 wolf 学号 2021080XXXXX

一、实验目的

1.了解简易模型机的内部结构和工作原理。

2.分析模型机的功能,设计 8 重 3-1 多路复用器。

3.分析模型机的功能,设计移位逻辑。

4.分析模型机的工作原理,设计模型机控制信号产生逻辑。

二、实验内容

1.用 VERILOG 语言设计模型机的 8 重 3-1 多路复用器;

2.用 VERILOG 语言设计模型机的移位模块;

3.用 VERILOG 语言设计模型机的控制信号产生逻辑。

[A]补=2*4-A

三、实验过程

1、8重3-1多路复用器

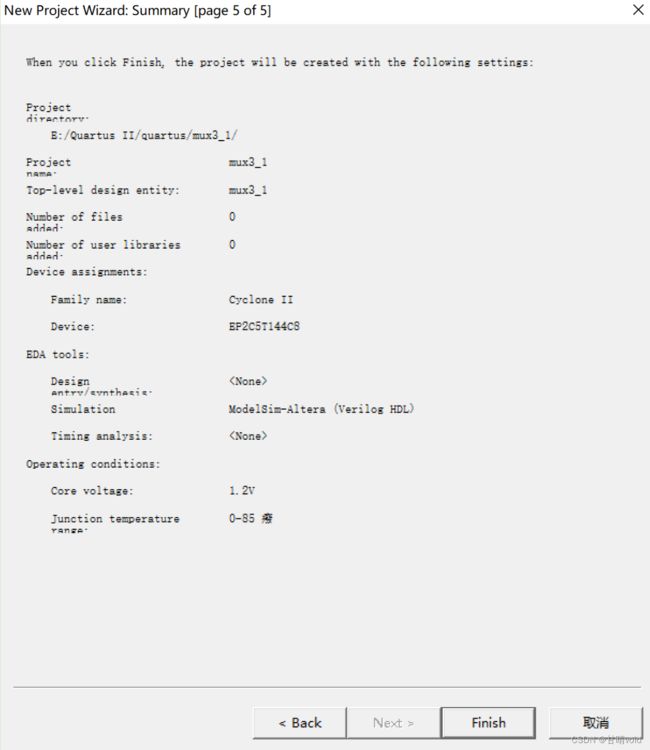

- 创建工程(选择的芯片为family=Cyclone II;name=EP2C5T144C8)

步骤:【File】->【new project wizard】->【next】->【next】->【properties】

->【next】->选择芯片类型 family=Cyclone II,name= EP2C5T144C8->【next】

->【finish】完成工程创建。

- 编写源代码

【file】->【Verilog HDL】->写好源代码,保存文件

C) 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

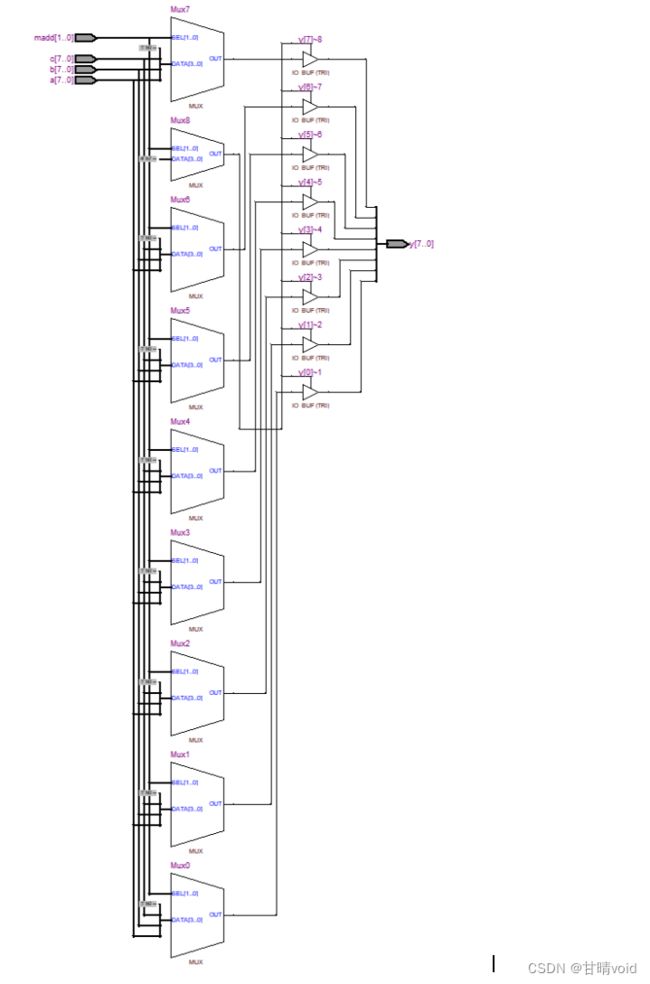

D) RTL视图

视图分析:

分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为 0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 madd和 a,b,c,输出信号为 y。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

madd=00 时,控制输出 y 等于 a,正确

madd=01 时,控制输出 y 等于 b,正确

Madd=10 时,控制输出 y 等于 c,正确

Madd=11 时,控制输出高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

F) 时序仿真波形

结果分析及结论:

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

G) 时序分析

操作方法是:编译后,在compilation report中选择【timing analysis】-【summary】和【tpd】

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 b[7]到 y[7]的最坏定时情况的 tpd 为 12.852ns。下面的tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟间,比如第二行中 a[7]到 y[7] 的tpd 为 13.820ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

2、移位逻辑

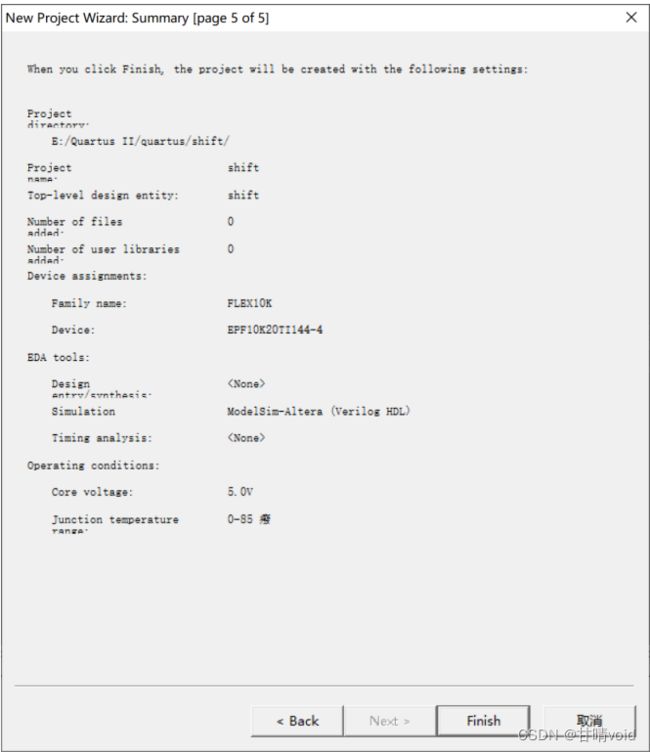

A)创建工程(选择的芯片为family=FLEX10K;name=EPF10K20TI144-4)

B) 编写源代码

- 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

警告信息:

无警告信息

资源消耗:

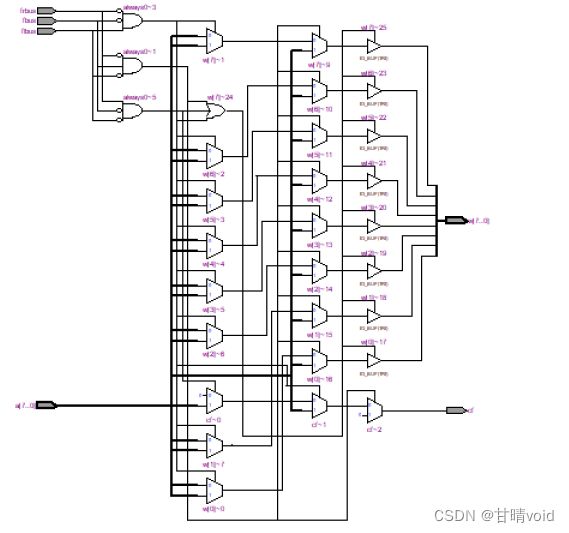

D) RTL视图

结果分析:

分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 fbus,frbus,flbus 和 a,输出信号为 w。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

当fbus=1,frbus=0,flbus=0,不执行移位操作,输出等于输入,cf 不改变

当fbus=0,frbus=1,flbus=0,执行右移,输出等于输入右移移位,有进位的话cf为1

当fbus=0,frbus=0,flbus=1,执行左移,输出等于输入左移一位,cf 不改变

当控制信号全为 0 时,输出为高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

F) 时序仿真波形

结果分析及结论:

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关, 又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时 改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

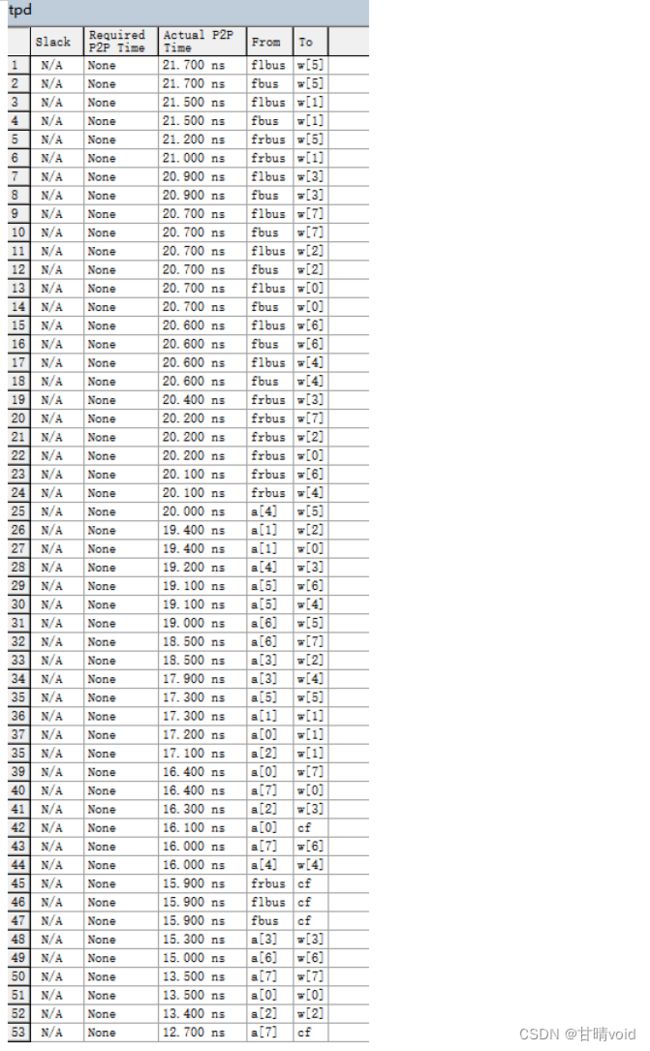

G) 时序分析

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 fbus 到 w[0] 的最坏定时情况的 tpd 为 20.700ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 fbus 到 w[7] 的tpd 为 20.700ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

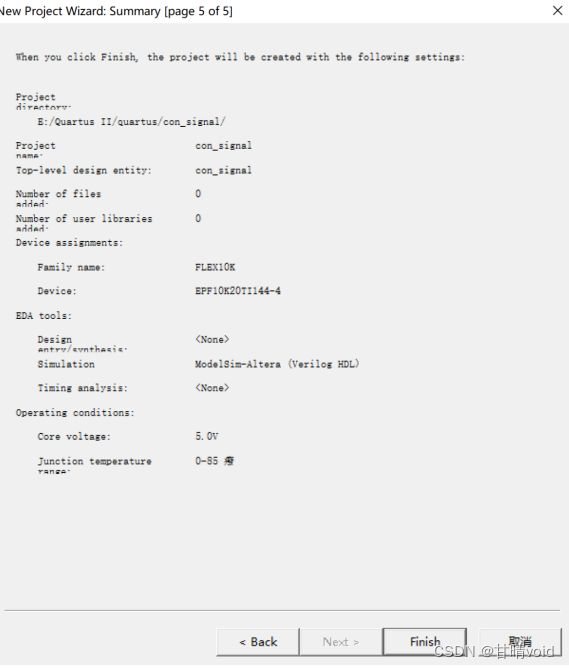

3、控制信号产生逻辑

A)创建工程(选择的芯片为family=FLEX10K;name=EPF10K20TI144-4)

B) 编写源代码

- 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

D) RTL视图

结果分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的与或门。图中输入信号为 sm 等20 个,输出信号包括 reg_ra 等 19 种情况。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

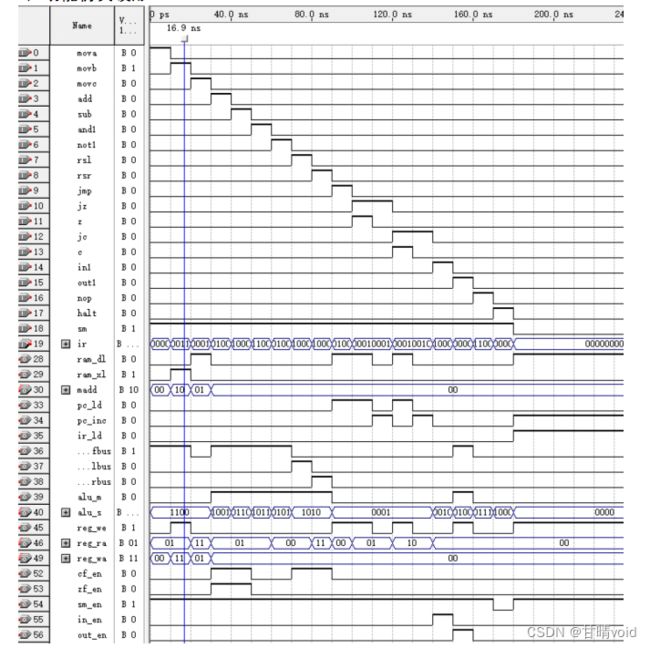

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验

证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路

设计的真值表的结果相对应。

(1)当 mova 指令执行时,shi_fbus 和 sm_en 输出 1,其他输出为 0,madd 输出 00,

alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 00,正确

(2)当 movb 指令执行时,ram_xl 和 shi_fbus 和 reg_we 和 sm_en 输出为 1,其他输出

为 0,madd 输出为 10,alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 11,正确

(3)当 movc 指令执行时,ram_dl 和 sm_en 输出为 1,其他输出为 0,madd 输出 01,

alu_s 输出 1100,reg_ra 输出 11,reg_wa 输出 01,正确

(4)当 add 指令执行时,shi_fbus,alu_en,cf_en,zf_en,sm_en 输出为 1,其他输出

为 0,alu_s 为 1001,reg_ra 输出 01,reg_wa 输出 00,正确

(5)当 sub 指令执行时,shi_fbus 和 alu_m,cf_en,zf_en 和 sm_en 输出为 1,其他输

出为 0,alu_s 输出 0110,reg_ra 输出 01,reg_wa 输出 00,正确

(6)当 and1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出

1011,reg_ra 输出 01,reg_wa 输出 00,正确

(7)not1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出 0101,

reg_ra 输出 00,reg_wa 输出 00,正确

(8)rsl 指令执行时,shi_flbus 和 alu_m 和 cf_en 和 sm_en 输出 0,其他输出 0,alu_s

输出 1010,reg_ra 和 reg_wa 输出 00,正确

(9)rsr 指令执行时,shi_frbus 和 alu_m 和 cf_en 和 sm_en 输出 1,其他输出 0,alu_s

输出 10110,reg_ra 输出 11,reg_wa 输出 00,正确

(10)jmp 指令执行时,ram_dl,pc_ld,reg_we 和 sm_en 输出 1,其他输出 0,alu_s

输出 0001,reg_ra 和 reg_wa 输出 00,正确

(11)jz 指令为 1 和 jc 指令为 1 时,若 z 和 c 为 1 时,ram_dl 和 pc_ld 和 reg_we 和 sm_en输出为 1,其他输出为 0,正确

若 z 和 c 为 0 时,pc_inc 和 reg_we 和 sm_en 输出 1,其他输出 0,正确

(12)in1 指令执行时,sm_en 和 in_en 输出 1,其他输出 0,正确

(13)out1 指令执行时,sm_en 和 out_en 输出 1,其他输出 0,正确

(14)nop 指令执行时,sm_en 输出 1,其他输出 0,正确

(15)halt 指令执行时,输出全为 0,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结

果有一定误差。0,reg_ra 输出 11,reg_wa 输出 00,正确

F) 时序仿真波形

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,

又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时

改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果

并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其

输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不

仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一

种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

G) 时序分析

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个

定时特性的最坏情况定时。比如从 sub 到 reg_we 的最坏定时情况的 tpd 为 26.600ns。下面 的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 and1 到

reg_we 的 tpd 为 26.300ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延

迟也不相同。

四、思考题

1.移位逻辑不工作时,输出应该为何值?为什么?

答:输出应成高阻,防止数据通路发生冲突,产生主线竞争。

2.移位逻辑的输出Cf应该如何处理?

答:

当fbus=1,frbus=0,flbus=0,不执行移位操作,输出等于输入,cf 不改变;当fbus=0,frbus=1,flbus=0,执行右移,输出等于输入右移移位,有进位的话cf为1;

当fbus=0,frbus=0,flbus=1,执行左移,输出等于输入左移一位,cf 不改变

当控制信号全为 0 时,输出为高阻态;

3.如何产生正确的控制信号以及具体的编程实现?

答:应当逐个分析每个控制信号在不同的指令下对应的状态,利用逻辑函数进行状态的总和。

五、实验总结、必得体会及建议

1、从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

(1)需要掌握的理论:基本了解了简易模型机的内部结构和工作原理。同时熟悉了选择器,移位逻辑,控制器的工作原理。学会 使用 Verilog 语言编写电路。

(2)遇到的困难:对于 QuartusII 的使用还不够熟练,特别是进行波形仿真的功能仿真和时许仿真分别怎么操作的方面有一定不足。

(3)解决方法:通过上网查询相关资料和询问同学后得以解决问题,并通过分析报告发现电路中的问题。有不理解的还请教了老师,不仅收获了方法还掌握的技巧。

(4)经验教训:对于电子电路的学习一定要肯动手,光是看是学不会的,一定要落到实处,多自己使用软件进行仿真,才能加深对于这门课程的理解。

2、对本实验内容、过程和方法的改进建议(可选项)。

控制器各个控制信号的输出功能表十分重要,可以先引导同学们列出这个对应表。