STA环境 - 时序路径

目录

- 1. 输入路径`set_input_delay`

- 2. 输出路径`set_output_delay`

- 4. 跨时钟域路径

-

- 4.1. 时序例外路径`set_false_path`

- 4.2. 引脚间路径`set_max_delay`,`set_min_delay`

- 4.3. 多周期路径`set_multicycle_path`

- 5. 恒值端口`set_case_analysis`

介绍数字设计中如何对各种时序路径进行STA约束。

● 时序路径: 信号从发起触发器(Launch Flip-Flop)D端起始,到捕获触发器(Capture Flip-Flop)D端结束构成的路径

注意“发起”和“触发”不是绝对的,一定是相对于某一条时序路径才能决定触发器到底是发起数据还是捕获数据

对于数字电路来说,需要STA分析的时序路径包括

- input2reg:从电路输入端到第一级触发器D端,组合逻辑,如下图路径1

- reg2reg:电路中发起触发器CK端到捕获触发器D端,时序逻辑,如下图路径2

- reg2output:电路中触发器CK端到输出端,时序逻辑,如下图路径3

- input2output:从电路输入端到电路输出端,组合逻辑,如下图路径4

时序检查就是针对以上几个时序路径的,显然最具代表性的时序路径就是第2条触发器到触发器路径

● 最大/小时序路径: 指整个电路中信号延迟最大/小的时序路径。

1. 输入路径set_input_delay

指定相对于某个时钟沿(默认为上升沿),输入端口数据到达时间

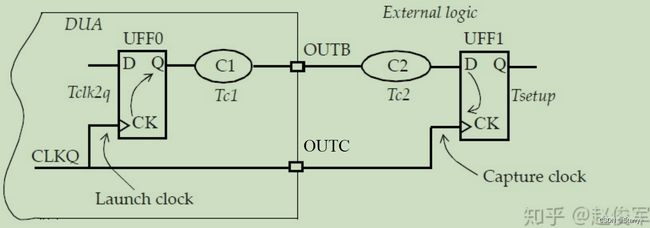

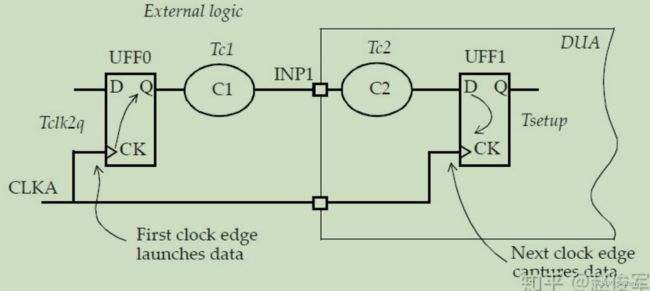

例如下图,右侧DUA表示设计内部,INP1为设计端口。

可指定INP1相比于时钟CLKA上升沿何时传来数据,即输入时延为 T C L K A 2 U F F 0 + T C K 2 Q U F F 0 + T C 1 T_{CLKA2UFF0}+T_{CK2Q}^{UFF0}+T_{C1} TCLKA2UFF0+TCK2QUFF0+TC1,可用于对UFF1进行STA

用下面的SDC指令指定输入延迟,-max表示最长路径输入延迟(用于建立时间检查)、-min表示最短路径输入延迟(用于保持时间检查),不写则表示确定时间

# 周期: 10ns

# 占空比: 50%

# 端口: CLKA

create_clock -period 2 [ get_ports CLKA]

# 每个时钟CLKA上升沿之后最长路径延迟1.5ns、最短路径延迟1ns,INP1端口传入数据

set_input_delay -clock CLKA -max 1.5 [ get_ports INP1]

set_input_delay -clock CLKA -min 1 [ get_ports INP1]

# 每个时钟CLKB上升沿之后6.7ns,INP2端口传入数据

set_input_delay -clock CLKB 6.7 [ get_ports INP2]

2. 输出路径set_output_delay

指定相对于某个时钟沿(默认为上升沿),输出端口数据要满足的输出时间

例如下图,右侧DUA表示芯片内部,OUTB为芯片端口。输出时延其实是一个差值,即 T C 2 − T O U T C 2 U F F 1 + T s e t u p U F F 1 / − T h o l d U F F 1 T_{C2}-T_{OUTC2UFF1}+T_{setup}^{UFF1}/-T_{hold}^{UFF1} TC2−TOUTC2UFF1+TsetupUFF1/−TholdUFF1

-max对应最长路径延迟时使用,用于建立时间检查

-min对应最端路径延迟时使用,用于保持时间检查

# 时钟CLKQ上升沿驱动,用于建立时间检查的外部路径延迟差为5ns

set_output_delay -clock CLKQ -max 5 [ get_ports OUTB]

# 时钟CLKQ上升沿驱动,用于保持时间检查的外部路径延迟差为1.5ns

set_output_delay -clock CLKQ -min 1.5 [ get_ports OUTB]

4. 跨时钟域路径

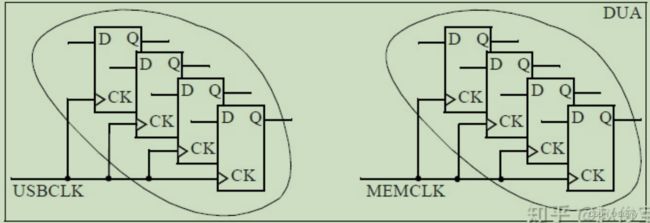

● 时钟域(clock domain): 同一个时钟驱动的一组触发器就为同一个时钟域。

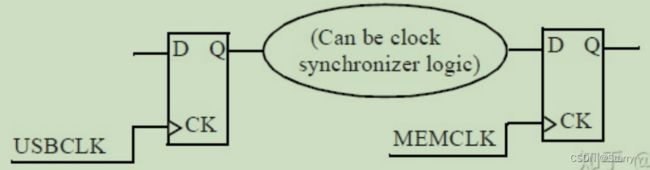

● 跨时钟域: 即一个时钟域的触发器Q端到另一个时钟域的D端存在数据路径。

针对跨时钟域路径有多种约束方式,如果SDC中多个约束方式存在重叠,则优先级最高的约束生效,如下图所示,约束越具体优先级越高。

4.1. 时序例外路径set_false_path

由于两个时钟关系不确定,必然会导致信号传输不满足setup time和holdup time,因此作STA时可以使用set_false_path设置伪路径不去分析这样的路径

# 从USBCLK时钟域到MEMCLK时钟域的所有时序路径均不作STA

set_false_path -from [get_clocks USBCLK] -to [get_clocks MEMCLK]

跨时钟域行为会导致亚稳态问题产生,所以一般需要通过同步器、异步FIFO等方式作同步。

4.2. 引脚间路径set_max_delay,set_min_delay

用于指定任意两个引脚间的最大最小延迟,而非触发器之间

set_max_delay 5.0 -to UFF0/D

set_max_delay 0.6 -from UFF2/Q -to UFF3/D

set_max_delay 0.45 -from UMUX0/Z -through UAND1/A -to UOR0/Z

set_min_delay -from U1/S -to U2/A 0.6

set_min_delay -from [get_clocks PCLK] -to [get_pins UFF/*/S]

4.3. 多周期路径set_multicycle_path

多周期路径及set_multicycle_path详解

sdc中set_multicycle_path的解释

深入浅出讲透set_multicycle_path,从此彻底掌握它

Verilog十大基本功9 (Multicycle Paths)

5. 恒值端口set_case_analysis

指定芯片的某些引脚为常值电平。

除了不必报告任何不相关的路径之外,这还有助于减少分析空间。使用set_case_analysis约束来指定此类常数信号。

set_case_analysis 0 TEST

set_case_analysis 0 [get_ports {testmode[3]}]

set_case_analysis 0 [get_ports {testmode[2]}]

set_case_analysis 0 [get_ports {testmode[1]}]

set_case_analysis 0 [get_ports {testmode[0]}]

如果设计具有多种功能模式,而只需要分析其中一种功能模式,可以使用set_case_analysis只分析某个端口某一种取值。

# 只考虑func_mode == 3'b101的情形

set_case_analysis 1 func_mode[0]

set_case_analysis 0 func_mode[1]

set_case_analysis 1 func_mode[2]