MIPI D-PHYv2.5笔记(19) -- Fault Detection

声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

检测链路的故障有三种不同的机制。总线冲突(总线竞争,bus contention)和错误检测功能包含在D-PHY内部。这些功能可以检查出许多典型的故障。但是有部分问题无法在D-PHY内部被检测到,需要协议层的解决方案来实现。因此,第三种检测机制是一系列应用专属的看门狗定时器(watchdog timers)。

冲突检测(Contention Detection)

如果一个双向Lane模块和一个单向模块组合到一起作为一条Lane使用的话,只有单向功能可用。由于在这种情况下,一侧的双向PHY模块不能被另一侧的功能受限的PHY所控制,因此双向模块的双向特性要能被安全地被禁用掉。否则会在某些情况下导致死锁的发生,只能通过系统掉电和重新初始化来解决。

在正常工作期间,一条链路任意时间点有且只有一侧去驱动一条Lane(某些特定的转换周期除外)。由于错误或系统故障,一条Lane可能会停在一个非预期的状态里,Lane可能被两侧所驱动或者Lane完全没有被驱动起来。这种情况最终会导致状态冲突,被称为冲突(竞争,Contention)。

所有带LP双向功能的Lane模块要包含冲突检测功能来检测如下冲突条件:

- 相同信号线两侧的模块在相互驱动对立的LP电平。

- 相同信号线两侧的一侧模块驱动LP-high但另一侧模块驱动HS-Low。

第一种条件能够被LP-CD和LP-RX功能组合检测到。LP-RX功能要能够检测到第二种冲突条件。关于LP-CD和LP-RX电气规范的细节和冲突检测相关电压描述,规范的第9章有比较详细的描述。对于做嵌入式软件开发来说,个人并不太关注也不熟悉这些信息,为了避免误导,相关部分不会做笔记。想要了解这些细节的朋友们,请自行参考规范。

在冲突被检测到之后,协议层要采取适当的措施解决问题。在ALP模式中不存在冲突检测机制。

Sequence Error检测

不管什么原因导致Lane信号损坏,接收的PHY可以检测到signal sequence错误。在PHY内部检测到的错误可以通过PPI和协议层进行通信。这类错误检测是可选项,但规范强烈建议用它来增强可靠性。

SoT Error

当deskew不支持时,Start of High-Speed Transimission的Leader sequence能够容忍任意的单bit错误和部分多bit错误。因此同步机制可能是可用的,但载荷数据的可信度会变低。如果发生了这种情况,会用SoT Error表示。

当deskew支持时,Leader sequence里的bit错误无法被容忍。如果在Leader sequence中有错,那么载荷数据是不可靠的。

SoT Sync Error

如果SoT Leader Sequence损坏,并且不能期望能够正确地同步,会用SoT Sync Error表示。

EoT Sync Error

EoT Sync Error出现的情况是当一次传输的最后一个bit对不上一个字节的边界时。这个错误只能在检测到LP-11时EoT处理的情况中被发出。

Escape Mode Entry Command Error

如果接收的Lane模块识别不了接收的Escaped Mode Entry Command,则这个错误被发出。

LP Transmission Sync Error

在一次Low-Power传输过程结束时,如果数据没有同步到一个字节边界时,这个错误被发出。

False Control Error

如果一个LP-Rqst(LP-10)后面没有跟着一个有效的Escape或Trunaround序列的余下部分,这个错误被发出。如果一个HS-Rqst(LP-01)后面没有正确地跟上一个Bridge State(LP-00),这个错误也会被发出。

对于Fast Lane Turnaround过程,如果Fast-BTA Control Code没有跟着一个HS-Trail sequence,这个错误也会被发出。

Protocol Watchdog Timers (Informative)

PHY不可能检测出所有错误情况。因此需要额外的协议层超时机制来限制特定模式和状态的最大持续时间。

HS RX Timeout

HS RX模式中,如果在特定的周期内没有接收到EoT,协议层会超时。

HS TX Timeout

HS TX的最大传输长度。

Escape Mode Timeout

在Escape Mode期间,设备可能会超时。这个超时时间应该大于另一个设备的Escape Mode Silence Limit。

Escape Mode Silence Timeout

在Escape Mode期间,对于LP TX-00,设备有一个边界长度,超出这个边界后另一个设备会超时。举例来说,一个显示模块应该要有Escape Mode Silence Limit,在这之后host处理器能处理超时。

Turnaround Errors

Control Mode Lane Trunaround Errors

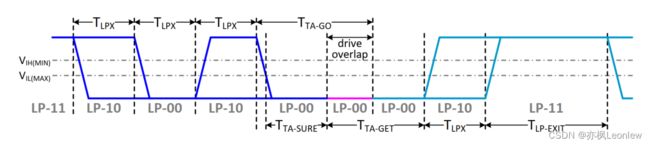

图1 Control Mode Lane Turnaround Procedure

一次Turnaround过程总是从Stop State开始。这个过程的开始于Low Power States序列,序列以Bridge State(LP-00)结束,期间驱动侧方向发生交换。这个过程最终是由另一侧所驱动的包含了一个Turn State紧跟一个Stop State的响应所完成。如果实际的事件序列违反了正常的Control Mode Lane Trunaround过程,“False Control Error”可被通知到协议层。Turn Sate响应的作用是正确地完成了Control Mode Lane Trunaround过程的确认信号。如果在特定时间内没有观察到确认信号,协议层会超时并采取适当的动作。对于一个特定系统而言,这个周期要大于Turnaround最大可能的时间。在PHY里这种情况没有超时处理。

Fast Lane Trurnaround Errors

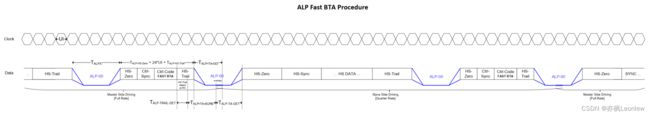

图2 Fast Lane Turnaround Procedure in ALP Mode

一次Fast Lane Trunaround过程总是从ALP Stop State开始。这个过程起始于传输一个Control Brust,这个Burst由Fast-BTA Control Code紧跟一个在HS-Trail周期完成之后的ALP-00转换所组成,期间驱动侧方向发生交换。这个过程最终是由另一侧所驱动的响应所完成,这个响应通常会包含一个由远端控制器所发送的确认包。如果实际的事件序列违反了正常的Fast Lane Trunaround过程,“False Control Error”可被通知到协议层。Turn Sate响应的作用是正确地完成了Fast Lane Trunaround过程的确认信号。如果在特定时间内没有观察到确认信号,协议层会超时并采取适当的动作。对于一个特定系统而言,这个周期要大于Turnaround最大可能的时间。在PHY里这种情况没有超时处理。