MIPI D-PHYv2.5笔记(16) -- Preamble Sequence、HS-Idle State、Sync Patterns

声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

Preamble Sequence

前导码序列(Preamble Seqence)的长度较短,它被插入到每个高速载荷的起始位置,目的是细调由于温度和电压变化导致的时钟到数据的偏斜(clock-to-data skew)。Preamble Sequence用于数据速率大于2.5Gbps的情况。

Premble Sequence由一个可编程长度的Preamble模式(pattern),持续时间为![]() ,以及一个固定长度(

,以及一个固定长度(![]() )的扩展同步模式(Extended Sync pattern)两部分组成。Extended Sync pattern的作用主要是为了避免在Leader sequence中发生特定的2-bit错误导致Preamble pattern被检测为Leader sequence。

)的扩展同步模式(Extended Sync pattern)两部分组成。Extended Sync pattern的作用主要是为了避免在Leader sequence中发生特定的2-bit错误导致Preamble pattern被检测为Leader sequence。

对于大于2.5Gbps的发送器和接收器,要支持Preamble Sequence。这种情况下,Preamble Sequence在被启用的情况下,要被插入到每一个HS burst中。

大于2.5Gbps的接收器,要检测Extended Sync pattern和Leader Sequence。发送器要允许以32 UI为步长,在![]() 允许范围能能够进行Preamble pattern的配置。

允许范围能能够进行Preamble pattern的配置。

在发送Leader序列之前,所有的Preamble pattern后面都要跟着一个Extended Sync pattern。Preamble pattern是持续周期为![]() 的101010模式所组成,默认要设置为typical值。

的101010模式所组成,默认要设置为typical值。

发送器Preamble pattern长度要能够被配置,包括能够禁用Preamble和Extended Sync,只传输HS Burst的选项。Extended Sync pattern是长度为![]() 的HS-1组成的序列。

的HS-1组成的序列。

图1 Normal High Speed Burst with LP Mode

图2 High Speed Burst and Preamble Sequence with LP Mode

图3 Preamble Timing Diagram (LP Mode)

图4 Preamble Timing Diagram (ALP Mode)

图5 Preamble Timing Parameters

HS-Idle State

对于LP-HS工作周期中的PHY来说,HS-Idle状态的支持是可选项。当使用ALP模式时,不支持HS-Idle状态。HS-Idle状态可以在两个HS Data Bursts之间被使用,此时能停留在HS信号模式中。当使用HS-Idle状态时,在两个HS Data Bursts之间没有切换到LP信号模式的过程。根据数据速率和HS-Idle的时序,两个HS Data Burst之间的延迟可以通过使用HS-Idle State来降低。HS-Idle状态包含HS-Idle-Post,HS-Idle-ClkHS0以及HS-Idle-Pre子状态,如下图所示:

图6 HS-Idle State sub-states

PHY可以让它的所有Data Lanes进入HS-Idle状态或LP Stop状态。

在Hs-Idle状态中,Clock Lane在所有Data Lanes都已经完成了它们的Data Bursts并且已经切换到了HS-0状态之后,停在HS-0状态中。PHY要产生HS-Idle状态中的Clock Lane和Data Lanes的HS-0信号。当载荷数据被传输之后,所有Data Lanes要发起一个HS-0信号,无论最后一个载荷数据bit的极性是什么。如果Clock Lane接收端在![]() 周期中没有检测到时钟活动并且所有Data Lanes都处于HS-0,RX状态机要切换到HS-Idle状态。当所有Data Lanes都处于LP-11状态时,RX状态机要切换到Stop状态。

周期中没有检测到时钟活动并且所有Data Lanes都处于HS-0,RX状态机要切换到HS-Idle状态。当所有Data Lanes都处于LP-11状态时,RX状态机要切换到Stop状态。

图7 HS-Idle State Machine Description

图7 HS-Idle State Machine Description

Clock Lane在所有Lanes的HS Data Bursts完成之后,要继续保持输出![]() 时间,以便能够有足够多的时间去清空(flush)接收器的流水线。

时间,以便能够有足够多的时间去清空(flush)接收器的流水线。

Clock Lane上的HS-0状态的持续时间为![]() 。在下一个HS Data Burst之前,Clock Lane要保持active的时间为

。在下一个HS Data Burst之前,Clock Lane要保持active的时间为![]() 。HS-Idle状态

。HS-Idle状态

HS-Idle状态要退出到SoT。下图展示了![]() 、

、![]() 和

和![]() 的开始和结束。

的开始和结束。

图8 HS-Idle Timing Diagram Example

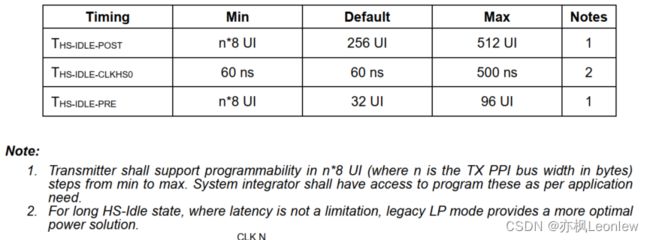

这些时序参数的值定义如下图所示:

图9 HS-Idle State Timing Parameters

发送器在启动(start-up)的时候要支持默认的时序值。系统集成者可以配置基于接收器能力来配置HS-Idle State参数为不同的值。

Sync Patterns

图10 Sync Pattern Definition