液晶显示器面板信号接口(二) —— V-by-One

V-by-One

- 1. 简介

- 2. 特点

- 3. 技术原理

-

- 3.1 发送端

- 3.2 接收端

- 3.3 数据通道

- 3.4 HTPDN信号

- 3.5 LOCKN信号

- 4. 接口

- 5. 屏线

本文主要介绍V-by-One,其它信号接口介绍可从以下链接跳转:

液晶显示器面板信号接口(一) —— LVDS

液晶显示器面板信号接口(三) —— eDP

1. 简介

V-by-One,即 V-by-One HS接口协议标准,是THine Electronics, Inc. (日本赛恩电子)面向高速发展的图像·视频设备提供更好支持而开发的新一代接口技术。

V-by-One HS技术目前已经应用于以平板电视为首的各种图像·视频设备(多功能打印机、安防摄像头、工业用摄像头、汽车导航仪、汽车后视摄像头等)之中,为设备的信号传输系统瘦身,通过节省线材、连接器及抗EMI元件降低系统整体成本,实现“低成本”,“低EMI”,“轻量化”和“高传输质量”的目标。

2. 特点

- 在设备内部连接的基础上实现视频信号的高速数据传输;

- 与目前的内部连接相比,实现更简单的使用和更低的功率消耗;

- 每对传输线支持高达4Gbps的数据率(有效数据率为3.2Gbps);

- 结合独家的均衡器技术,可以实现更好的数据传输性能;

- 支持抗干扰和时钟数据恢复(CDR),以减少EMI;

- 支持CDR,以解决传统传输系统中时钟和数据之间的偏移问题;

3. 技术原理

V-by-One HS专有的 编码方案 和 CDR架构,通过差分对传输线,传输高达40 bit的视频数据、高达24 bit的CTL数据、Hsync、Vsync和数据启用(DE),并且只需少量的元件。

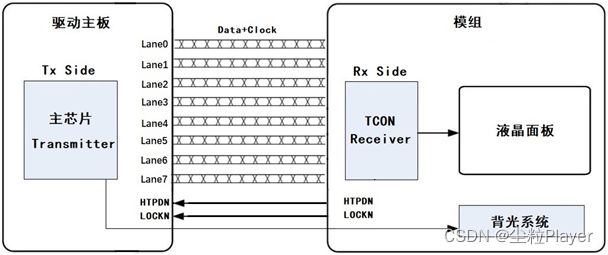

如下图所示,V-by-One HS链路包括数据通道、热插拔检测信号(HTPDN)和CDR锁定信号(LOCKN)。

数据通道的数量(1~32 Lane)由2个因素决定:

- 刷新率(60 Hz —> 240 Hz)

- 色深(18/24/30/36 位)

发送端 和 接收端 之间的【HTPDN连接】可被省略。

作为可选功能,可以实现发送端pre-emphasis和接收端equalizer。

3.1 发送端

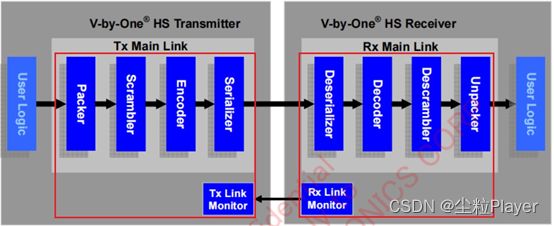

V-by-One HS 发送器由Packer、Scrambler、Encoder、Serializer和Tx Link Monitor组成。

Tx Link Monitor持续监控 LOCKN 和 HTPDN 信号,根据其状态发送CDR training 和 ALN training

3.2 接收端

V-by-One HS接收端由Unpacker、Descrambler、Decoder、Deserializer和Rx Link Monitor组成。

在CDR training模式下,接收端根据CDR training pattern,同步像素时钟。

从CDR training模式转到常规模式后,接收端根据ALN training来对齐byte和bit的位置。

3.3 数据通道

数据通道是带电阻的交流耦合差分对。

根据像素时钟和色深,通道传输速率Tr可以设置为:600Mbps ≤ Tr ≤ 4Gbps

例如当前屏型号M280DGJ-L30为:3840*2160@60Hz(10 bit色深)

根据公式:

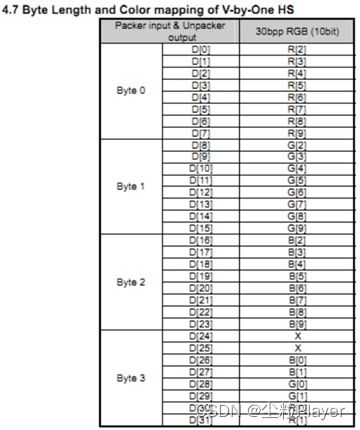

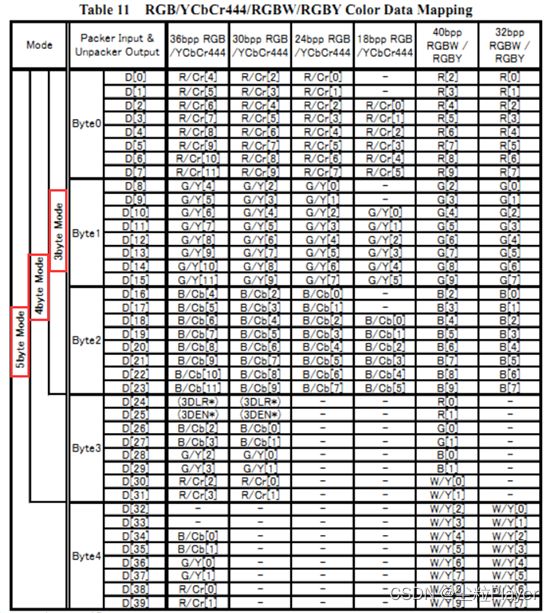

(1)参数[byte mode]

byte mode是根据色深来选的,一共有[3 byte]、[4 byte]和[5 byte]这3种模式供选择。

因为屏是10 bit色深,即每个像素需要R+G+B = 10+10+10 = 30 bit的数据。

所以,选则 4 byte模式(传输4字节= 4x8 = 32 bit)就足以承载数据。

(2)参数[10/8]

因为V-by-One HS 使用 8b/10b 编码方案,所以物理传输的编码数据量是10 bit(有效数据只有8 bit)。

(3)参数[pixel clock]

Pixel clock需要根据公式来计算:

Pixel clock = H-Total * V-Total * Rrame rate = 4400 * 2250 * 60Hz = 594MHz

将3个参数代入公式:(4 x 8) x 10/8 x 594MHz = 23.76Gbps

再代入公式:600Mbps=0.6Gbps ≤ 23.76Gbps/Lane Number ≤ 4Gbps

得出 Lane Number = 8/16/32 Lane 都符合。

综合考虑,8 Lane是最合适选择。

3.4 HTPDN信号

HTPDN:确认发送端和接收端之间的连接情况。

当接收端没有反应或没有连接时,发送端一侧的 HTPDN 为高电平(默认上拉),发送端可以进入断电模式。当接收端激活并连接到发送端时,HTPDN被接收端设置为低电平,此时发送端启动并发送CDR training pattern进行link training。

作为一种应用选择,发射器和接收器之间的HTPDN连接可以被省略,在这种情况下,发送端的HTPDN应被置为低电平。

3.5 LOCKN信号

LOCKN:确认是否完成CDR training进入锁定状态。

当接收端不工作或处于CDR PLL training状态时,发送端LOCKN输入被置为高电平(默认上拉)。

当CDR锁定完成后,LOCKN被接收端设置为低电平,等待ALN training结束,ALN training完成后,发送端转为常规模式,开始发送数据。

4. 接口

在液晶显示器中,V-by-One接口电路包括两部分,主板侧 和 液晶面板侧。

以笔者当前主板接口和屏为例:

当前的屏型号为 M280DGJ-L30,其规格使用 51Pin 8 Lane 传输

8对差分线(Lane0~Lane7)同时传输,每对差分线传输一个像素,共8个像素一起传输数据。