FPGA中亚稳态、异步信号处理、建立和保持时间违例及题目合集

文章目录

- 一、亚稳态

-

- 1.1 降低亚稳态方法

- 二、异步信号处理的方式

- 三、建立和保持时间公式推导

-

- 3.1 建立时间

- 3.1 建立时间违例解决方法

- 3.2 保持时间违例解决方法

- 四、题目

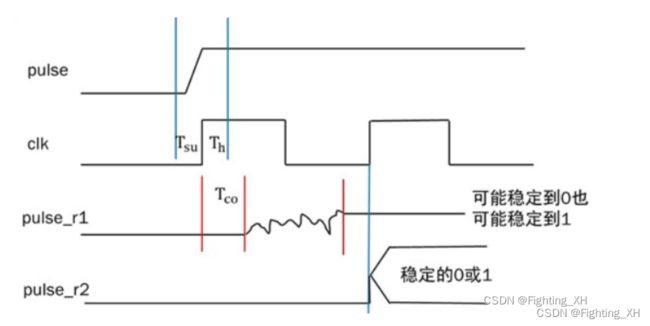

一、亚稳态

亚稳态:输入信号的变化发生在时钟有效沿的建立时间和保持时间之间,导致其不满足触发器建立保持时间的时序要求,使得输出有一段时间的不确定状态,这就是亚稳态。

1.1 降低亚稳态方法

1、降低时钟频率

2、异步信号同步处理

二、异步信号处理的方式

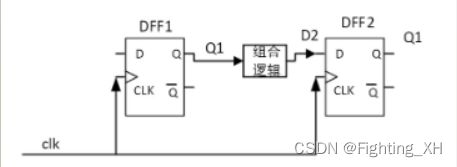

1、对于单比特数据,在慢时钟域到快时钟域的数据传输中,需要使用两级触发器进行同步,消除亚稳态,也可以采用握手协议。

2、对于多比特数据:采用异步FIFO处理,因为两级同步处理后的数据只能保持稳态,但并不能确定到底是0还是1,因此如果多比特数据也用多级触发器同步的方式,会出现乱码,因此采用FIFO。

3、握手协议常用于慢时钟域到快时钟域的多比特数据的传输中,能确定稳定时输出值是0还是1,从而让数据能正确传输。

4、对于异步复位信号,采用异步复位,同步释放的方式处理。

5、格雷码:即使在亚稳态进行读写指针抽样也能进行正确的空满状态判断

6、DMUX

三、建立和保持时间公式推导

建立和保持时间都是在STA基础上分析的。

3.1 建立时间

3.1 建立时间违例解决方法

根据公式若Tsu违例,我们应让公式左边增大,因此解决方法如下:

1、增大周期T,因此降低时钟频率

2、增大时钟延时,从而Tskew变大。

3、Tco固有属性,因此不可变。

4、Tcmob减小,从而减少组合逻辑延时(流水线的方式减少组合逻辑延时)

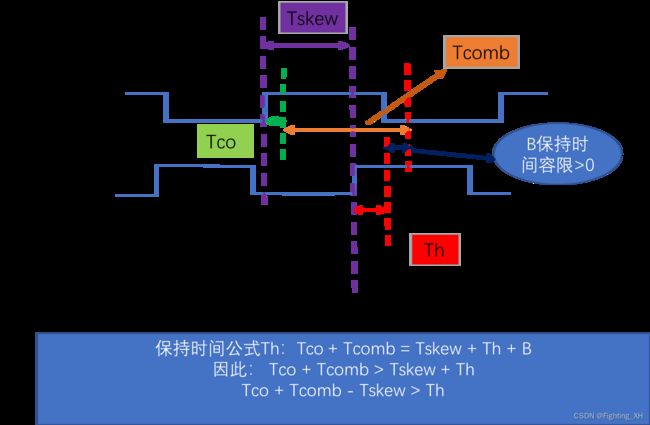

3.2 保持时间违例解决方法

同样根据公式,让左边更大即可。

1、增大组合逻辑延时

2、Tskew减小,降低时钟延时。

四、题目

题目1:

下列哪些方式可以减少亚稳态问题的影响()

A.提升系统时钟频率

B.用反应更快的FF

C.架构上增加data toggle rate

D.改善时钟质量

BCD

分析:降低时钟频率可以大大减小亚稳态导致系统错误

题目2:

125MHz时钟域的多bit信号A[127:0]需要同步到25MHz时钟域,可能使用的同步方式有(ABD)

A.双向握手

B. DMUX

C.打三拍

D.异步FIFO

分析:题目考察两点:快时钟域到慢时钟域的异步处理;多比特信号的异步处理;

其中打拍只能用于单比特异步处理。

题目3:

下面哪个不属于跨时钟域数据传递的基本方法( D )

A:使用多级触发器缓冲

B:使用FIFO

C:使用握手协议

D: 信号通路上插入isolation

分析:

A:对于单比特数据,在慢时钟域到快时钟域的数据传输中,需要使用两级触发器进行同步,消除亚稳态,也可以采用握手协议。

.

B:当多比特数据传输的时候采用异步FIFO处理,采用FIFO。

.

C:握手协议常用于慢时钟域到快时钟域的多比特数据的传输中,能确定稳定输出值是0还是1,让数据可以正确传输

题目4:

某个时钟域的建立时间要求是3ns,保持时间要求是3ns,那么如下几个寄存器,存在时序收敛问题的是:(ACD)

A.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns

B.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns

C.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效治前,保持稳定不变的时间为2ns

D.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间的2ns

分析:必须满足建立时间和保持时间的要求,否则可能出现亚稳态

题目5:

以下关于异步处理正确的是 ( C )

A:信号经过两级触发器即可完成异步信号的传递

B:只要信号传递的两端时钟频率不相等,即认为是异步信号

C:异步复位信号需要经过同步处理后再使用是安全的 (异步复位,同步释放)

D:异步FIFO中使用格雷码传递异步计数器可以保证每一拍传递的数据都是准确的

A:多比特信号不适用

B: 同一个晶振出来的时钟,如果用了PLL分频,也属于同步信号。只要不是同一个晶振出来的时钟,就是异步的

D:异步FIFO使用格雷码的唯一目的就是“即使在亚稳态进行读写指针抽样也能进行正确的空满状态判断。

题目6:

关于跨时钟域电路的设计,以下说法正确的是 ( D )

A:单bit信号经两级D触发器同步后即可进行跨时钟域传递

B:采用单一时钟的电路不会产生亚稳态

C:异步FIFO的两个时钟频率相同也可以正常工作

D:跨时钟域电路当中的亚稳态无法消除 (只要系统中有异步元件,亚稳态就无法避免)

解析 :

A:单bit跨时钟域中可用两级触发器同步,适用于慢时钟域数据到快时钟域;

.

B:亚稳态产生原因是不满足建立时间setup或保持时间hold,单路时钟情况下也有可能不满足

.

C:要设置一个优先级,否则有可能在满、空状态时出现问题

.

D:亚稳态是无法消除的,通过同步处理可减少亚稳态的出现。

题目7:

假设一个3bit计数器(计数范围为0~6)工作在38M时钟域下,要把此计数器的值传递到另一个异步100M时钟域,以下不正确的是(C)?

A. 使用异步FIFO

B. 锁存+握手信号

C. 使用格雷码

D. 使用DMUX电路

分析:3位格雷码进行二进制转十进制的计算,发现若计数范围是0-7才可用格雷码

[多选题]下列关于Setup/Hold Time说法正确的是?(AD)

题目8:

[多选题]下列关于Setup/Hold Time说法正确的是?(AD)

A.如果DFF的Hold时间不满足,通常可以通过增加数据路径延时来解决

B.如果DFF的Setup时间不满足,通常可以通过增加数据路径延时来解决

C.如果DFF的Hold时间不满足,通常可以通过增加时钟路径延时来解决

D.如果DFF的Setup时间不满足,通常可以通过增加时钟路径延时来解决

根据上面的建立保持时间图和公式分析即可

A:增大Tcomb

D:增大Tskew

题目9:

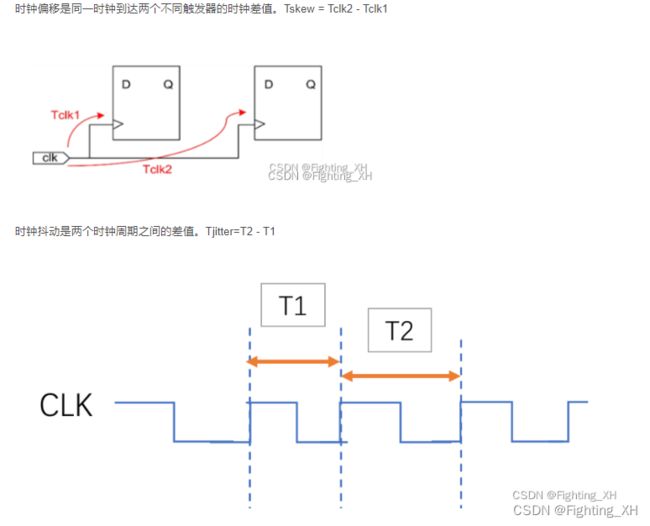

在静态时序分析中计算时钟延迟需要考虑一下哪些因素? CD

A. 寄存器的建立和保持时间

B. 工艺特性造成的on-chip variation

C. 时钟源的抖动(jitter)

D. 时钟树不平衡引入的偏差(skew)

E. 系统时钟干扰

题目10:

以下关于格雷码的描述哪些是正确的? ABCD

A. 卡诺图的坐标是按照格雷码的顺序标注的

B. 格雷码0110对应的二进制数是0100

C. 格雷码相邻的码组间仅有一位不同

D. 格雷码从编码形式上杜绝了逻辑冒险的发生

E. 格雷码常用于提高单一时钟域内总线数据的可靠性

格雷码使得组合逻辑的输入端只有一个发生变化,因此杜绝了逻辑冒险的发生。

题目11:

关于电路处理说法正确的是:A

A:同步电路系统中可以有一个时钟以及三分频时钟进行驱动;

B:DFF的setup时间是根据DFF和DFF之间的时序路径分析出来的,把时钟变慢可以增加DFF的setup时间

C:数字电路设计中是竞争和冒险会带来电路上的毛刺,需要加入RC滤波电路清除

D:如果DFF的hold时间不满足,通常可以通过时钟运行速度来解决

E:异步reset信号因为和时钟是异步的,因此不需要加时钟约束

解析:

A:电路采用PLL进行分频,但最终都是在全局时钟下,为同步电路

.

◆B:setup时间是由寄存器内部的结构决定的,与时钟无关。

.

◆C:竞争和冒险是由不同路径的延时不同导致的。

.

◆D Th由寄存器内部的结构决定的,但如果不满足,通过增大组合逻辑或者减小时钟延迟来解决

.

◆E要加时钟约束,有恢复时间和移除时间

题目12:

D触发器:Tsetup=3ns,Thold=1ns,Tck2q=1ns,该D触发器最大可运行时钟频率是 B

A 1GHZ B 250MHZ

C 500MHZ D 200MHZ

解析:算最大时钟频率先求最小时钟周期,也就是找到最大的延迟,Tsetup + Tck2q

是整个路径上delay,最大频率和Thold无关,所以就是4ns,为1000/4=250MHZ,答案为B。

题目13:

关于建立setup和保持hold时间的表述哪些是正确?AC

A:解决setup time violation的方法之一是适当降低时钟频率

B:解决hold time violation的方法之一是适当降低时钟频率

C:setup time 不受系统时钟频率影响

D:setup time 是指有效的时钟沿来临之后的数据需要保持的时间

题目14:

如下图所示:clk到Q的输出延时为T1min

Tsetup < T-T1max-T2max; T1min + T2min > Tholdup

题目15:

下列关于多bit数据跨时钟域的处理思路,错误的有(A)

A. 发送方给出数据,接收方用本地时钟同步两拍再使用.

B. 发送方把数据写到异步fifo,接收方从异步fifo里读出.

C. 对于连续变化的信号,发送方转为格雷码发送,接收方收到后再转为二进制.

D. 发送方给出数据,发送方给出握手请求,接收方收到后回复.

题目16:

关于异步处理,以下说法正确的是:AC

A. 静态配置信号可以不做异步处理.

B. 异步FIFO采用格雷码的原因是为了提高电路速度.

C. 异步处理需要考虑发送和接收时钟之间的频率关系.

D. 单比特信号打两拍之后可以避免亚稳态的发生.

解析D:快到慢就没办法只使用“打两拍”,如C所说,要考虑频率关系,比如快到慢,需要展宽信号。亚稳态不能消除,只能降低。

参考

题目17:

which of the following files are necessary for timing analysis? CD

A. SPEF. B. DEF. C. SDC. D. Netlist.

题目18:

Which among the following methods are applicable to fix setup violation? ABD

A. Swap high Vt cells into low Vt cells.

B. Increase driver size of long net.

C. Delaying the clock to the end point.

D. Decreasing the size of certain cells in the data path.

解析: 建立时间公式:T - Tco - Tcmob + Tskew > Tsu

若不满足,则措施:

1、增大T和Tskew——B

2、增大Tcmob ——AD正确——因为将高电压换成低电压,组合逻辑延时增大

题目19:

寄存器如果出现亚稳态,则其亚稳态的持续时间为(D)

A、1个时钟周期

B、小于1个时钟周期

C、大于1个时钟周期

D、不确定

题目20:

下列说法错误的是(C)

A、管脚静态配置信号可以不用做异步处理

B、异步FIFO设计时需要考虑两个时钟之间的频率关系

C、异步FIFO设计中使用格雷码的目的只要是为了提高电路速度

D、异步电路中,只有信号电平翻转才可能引入亚稳态

题目21:

150MHz时钟域的多bit信号A[63:0]需要同步到50MHz时钟域,可能使用的同步方式有(ABD)

A、DMUX

B、双向握手

C、打拍

D、异步FIFO

题目22:

以下哪些设计会导致STA分析困难(ABCD)

A将时钟之间作为数据使用——时钟是有偏移的

B同一模块中存在大量异步逻辑

C组合逻辑环

D使用latch锁存器

题目23:

在一个FPGA项目中,既有建立时间异常(setup violation),也有保持时间异常(hold violation),应该如何修改设计以使其正常工作?

解析:首先我们根据STA原理得到满足时序设计的Tsu和Th的公式。

1、对于Tsu来说:T + Tskew - Tco - Tcomb > Tsu。 当建立时间异常时,根据公式可知,应左边增大。

方法:周期增大从而降低时钟频率;适当增大时钟延时;减少组合逻辑延时;Tco固有属性;

2、同理,对于Th来说,Th + Tskew < Tco + Tcomb ;Tco + Tcomb - Tskew > Th

当保持时间异常的时候,左边尽可能大。

方法:Tcomb增大, Tskew减少。

题目24:

![]() 根据第二部分建立保持时间的公式推导,代入即可,其中Tskew= T5; Tcmob = T2 + T3 + T4 ; Tco = T1;

根据第二部分建立保持时间的公式推导,代入即可,其中Tskew= T5; Tcmob = T2 + T3 + T4 ; Tco = T1;

最后一个正确。

题目25:

[单选题]以下对hold timing有帮助的是 ——D**

A.提高时钟频率

B.降低时钟频率

C.提高工作电压

D.降低工作电压

解题:

*根据Th的推导公式来选择,其和时钟频率的提高降低无关;

.

Tco+Tcomb-Tskew > Th;因此两种方法:1、增大组合逻辑延时,2、减小时钟偏移

本题降低工作电压,速度变慢,组合逻辑延时增大,从而保证 Th满足要求

题目26:

[多选题]EDA验证中,下面哪种方式可以对时序进行检查(BCD)

A.即时断言 —— 基于时间的,无时序关系

B.并发断言——基于时钟的

C.建立时间约束

D.保护时间约束

题目27:

在IC设计中,复位设计面临的主要问题包括(ABCD)

A.时钟域的同步

B.去毛刺

C.可否做STA检查

D.对时钟的依赖程度

题目28:

以下关于FIFO描述正确的是

A. 空信号是在写时钟域产生的,满信号是在读时钟域产生的

B. 外部可以直接操作FIFO的读写地址

C. FIFO可以分为同步FIFO和异步FIFO

D. FIFO是先进先出的存储器

解析:C:写满,读空。D:外部不可以直接操作FIFO的读写地址

题目29:

现有三个输入信号分别是a,b,c,并且前级DFF Clock到a,b,c的延时分别是Ta,Tb,Tc(Ta>Tb>Tc),请用两个二输入选择器对a,b,c实现三输入选择输出,画电路图并解释设计思路,不需要考虑Clock Skew的影响。

题解:由于Ta>Tb>Tc,因此a延时最大,c延时最小,因此电路图如下:

![]()

题目30:

时序检查中对异步复位电路的时序包含什么?

对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recovery恢复时间:在有效的时钟沿来临前,异步复位信号保持稳定的最短时间;

.

removal移除时间:在有效的时钟沿来临后,异步复位信号保持稳定的最短时间;

题目31:

于亚稳态,以下说法错误的是(A)

A. 亚稳态打两拍就可以消除

B. 亚稳态出现的概率与器件工艺,时钟频率等有关

C. 数字系统中,信号无法满足set up 和 Hold 时容易出现亚稳态

D. 当一个触发器进入亚稳态,即无法准确预测寄存器输出电平,也很难预测何时输出才能稳定在某个正确的电平上

题目32:

同步电路设计中出现setup time 不满足,不可以采用下面哪种措施解决 D

A. 减小时钟信号延迟

B.降低时钟频率

C.pipeline

D 增加时钟频率

题目33:

高频时钟数据(每个时钟周期数据都在变化)传递给低频时钟域,用什么方法:C

A.使用低频时钟2级寄存器同步

B. 使用握手信号同步

C.使用异步FIFO同步

D.使用同步FIFO同步

题目34:

异步电路都不需要STA进行约束检查 B

A. 正确

B. 错误