嵌入式开发之以太网

近几年的接触到了很多以太网的项目,网上也有很多关于以太网的问题,本文会将遇到的以太网问题包括以太网的基础知识,做一个自我总结,也顺道分享给有需要的人。

文章先从理论知识进行介绍,然后结合遇到的各种案例进行分析。

首先是是整体架构:MAC→PHY→接口,首先得明白理解各个部分功能和含义。这其中有个疑问就是:为啥不把MAC和PHY放在一起更简单呢,其实受制于制程工艺 的难度,PHY整合了大量模拟硬件,而MAC是典型的全数字器件,芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因。不过目前更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合

MAC:即媒体访问控制子层协议。该部分有两个概念:MAC可以是一个硬件控制器 及 MAC通信以协议。该层位于OSI七层结构中数据链路层的下半部分,主要负责控制与物理层与连接物理层的物理介质。

![]()

上图为MAC的主要架构图。

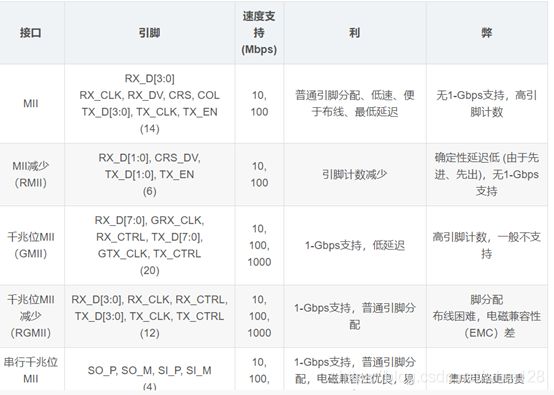

可以看出MAC与PHY接口有两个

1.一个是MII总线接口或者SGMII(区别视SGMII属于串行);

2.一个是MDIO接口。

下面介绍下MII接口,这里面是有个总线总结。

MII接口还有RGMII,GMII等,

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线;和MII一样,RMII支持10M的总线接口速度。

GMII是千兆网的MII接口,RGMII表示简化了的GMII接口。下面这个图介绍的很好:

这些是数字接口,负责传输数据,MDIO接口是配置管理接口,MAC通过此接口来配置PHY接口。

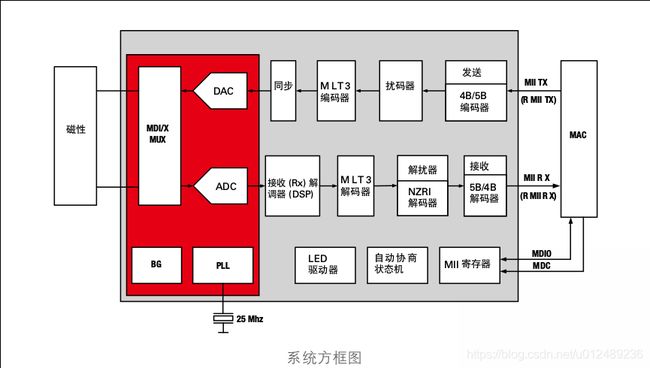

其实硬件设计主要在PHY这一层,然后两边的电气连接,下图为PHY的基础架构。

PHY负责把MAC的数字信号进行编码,串行化等操作后,转化为模拟信号进行发送。PHY在数据接受时, 进行如上所述的逆操作,将模拟信号转化为数字信号,解码,并行化后,传给MAC。

这里面PHY在硬件设计时,要注意区分电流型phy还是电压型phy,这是非常容易出错的一个地方,最简单的判断方式,就是查询其参考电流,观察变压器中心抽头的接法,细节将在具体案例中给与解释。

最后是变压器

变压器本身是被动元件,主要将信号耦合到网线上, 使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用(如雷击); 当接到不同电平(如有的PHY芯片是2.5V,有的PHY芯片是3.3V)的网口时,不会对彼此设备造成影响。

另外还有以太网数据帧的格式,ARP协议,TCP及UDP传输协议等,在本文中就不做介绍了,建议有空的可以自我了解。

以下列举几个案例,常见的误区,

1.最常见的问题当属于100M可以通,而1000M link不通?

首先考虑到,千兆速率相对百兆有了大幅度的提升,不得不考虑信号完整性问题。在硬件设计上,差分对内PN需要跨界100欧姆电阻,但是确出现了有的项目千兆增加了这个电阻才通,而有的项目去掉之后才通。这其实就是常犯的第一个问题,因为有的PHY内部集成了,所以不用加。

另外一个就是中心抽头的接法,由于PHy分为电压型和电流型,电压型phy的中心抽头需要接电容到地,而电电流PHY需要接到电压VCC。下路就是电流型phy与电压型phy的电流路径,所以导致了推荐用法就是电压或者电流型用法,需要特别注意。

某项目采用不用的RJ45链接器,也出现了这个问题,这其实也是这个知识点。

![]()

![]()

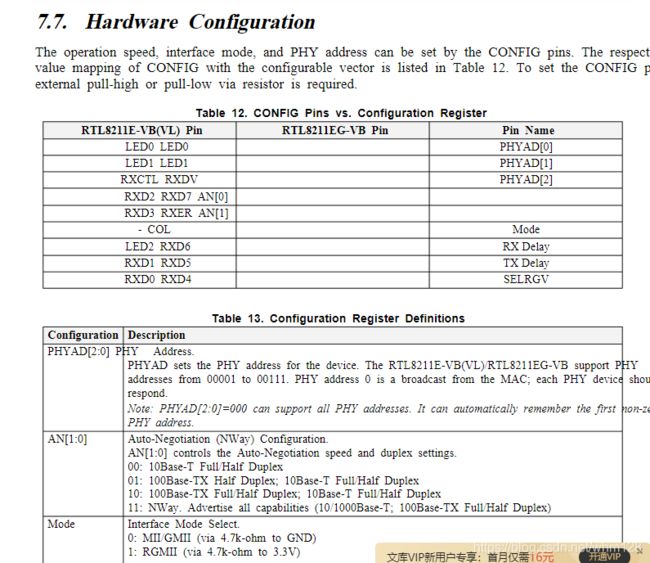

最后就是一些基本的配置,默认配置建议按datesheet说明进行配置,下图就是RTL8211E的一些配置,

另外需要特别注意的就是,有些PHY芯片会有一些低功耗的设置,在无特殊要求下,尽量不使用低功耗模式。

最后一个和这个相关的点就是,某些MAC芯片的输出电平要求并符合RGMII的电平规范,最常见的就是我们xinlinx的7系列的某款FPGA,他的3.3V电平并不符合RGMII的电平。

2.另一个经常出现的问题就是,千兆可以link,但是UDP传输时容易产生误码,而TCP传输时,速率上不去?

之前在设计中多次遇到这个问题,首先是电源设计问题,见下图是RTL8211的设计,在PCB设计时有严格的要求,记得有项目就是这个设计有问题所导致。

另外关于这个问题还有MAC核的内部的一些配置,像寄存器输出之类的这也很关键。关于MAC最好能自己手写一个,这样会加深对协议的理解。

,![]()

3.另外就是在时钟设计上

PHY的设计有个25M时钟,一般在采用无源晶振,如果要使用有源晶振,需与供应商确认清楚,内部起振电流的类型,一般90%以上的内部起振电流都是皮尔斯振荡器,这类震荡器结构我们建议有源晶振输入接在out口。

案例介绍并不全面,想起来整理完我会在更新。

第二层皮 2021.04.03于合肥

以下为本文一些知识的参考链接原文:

电流型和电压型PHY_电流型phy和电压型phy_谁de如花的博客-CSDN博客

以太网基础-MAC和PHY_奇小葩的博客-CSDN博客