PCB高频电路设计中的差分信号设计

目录

1、差分信号的定义

2、如何布置差分线路?

3、微带线和带状线的概念

4、布线中常用的匹配方法

1、差分信号的定义

什么是差分布线:差分布线主要是区别传统的信号线对应一根地线的信号传输方式,差分信号传输主要是两条线上都有信号传输,两个信号振幅相等,相位相反而已。

相对于传统的单端信号,它具有抗干扰性强、能有效抑制电磁干扰和时序定位准备等优点。

2、如何布置差分线路?

线路板设计时差分对的布线要注意两点:

(1)一是两条线的长度要尽量一样长;

(2)另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。

平行的方式通常有两种,一种是PCB板上两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以同意走线层实现的方式较多。要用差分布线一定是信号源和接收端也都是差分信号才有意义。所以对只有一个输出端的时钟信号是无法使用差分布线的。接收端差分线对间的匹配电阻通常会加,其值应等于差分阻抗的值,这样信号品质会好些。对差分对的布线方式应该要适当的靠近且平行。为何要适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。

若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。

1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰,走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线,误差允许在20mil以内。

2.地址、片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil,尽量走成菊花链拓补,可有效控制高次谐波干扰,可比时钟线长,但不能短。

3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

一般大于 5Gbps 的高速差分信号对干扰和抖动等都很敏感,因此在设计高速差分信号线布线时,应尽量选用性能良好的微带线和带状线,在整个信号通路上保持一致的阻抗特性。对差分信号线进行布线之前,必须定义好层叠结构,以使走线能够保证严格的阻抗匹配。

由于传输的差分线信号频率很高,两根差分信号必须在长度上尽量匹配,长度失配会产生共模噪声和辐射,严重的失配还会产生抖动 (Jitter))和不可预测的时序问题。比如 :6.25Gbps 差分信号来讲,其码元时间长度仅为160ps,而 FR4 PCB 线路中微带线上的信号,大概以每英才180ps 的速度传送,因此 50mil 的布线差别就会导致大约 9ps 的时序偏移,因此原来在低频差分布线中可以接受的 50mil 非耦合长度,在高于 5Gbps 的设计中就会带来时序问题。保持严格的长度匹配,是高速差分布线的首要任务。

3、微带线和带状线的概念

- 带状线:线走内板层,信号线是嵌在两层导体之间的带状导线,它的电场分布都在两个包它的导体(平面)之间,不会辐射能量出去,也不会受到外部的辐射干扰。但由于它的周围全是电介质(介电常数比1大),所以信号在里程中的传输速度比在表层中慢。

![]()

- 微带线:线走在板层表面, 如下图,蓝色部分是导体,绿色部分是PCB的绝缘电介质, 由于微带线的一面裸露在空气里面(可以向周围形成信号辐射或受到周围的辐射干扰),而另一面附在PCB的绝缘电介质上,所以它形成的电场一部分分布在空中,另一部分分布在PCB的绝缘介质中。但是微带线中的信号传输速度要比带状线中的信号传输速度快,这是其突出的优点。

![]()

蓝色部分是导体,绿色部分是PCB的绝缘电介质,上面的蓝色小块儿是microstrip line。

![]()

其中黄色部分是环氧有机材料。

- 和微带线带状线相关的概念和公式

-

微带线是一根带状导线(信号线).与地平面之间用一种电介质隔离开。如果线的厚度、宽度以及与地平面之间的距离是可控制的,则它的特性阻抗也是可以控制的。

-

带状线是一条置于两层导电平面之间的电介质中间的铜带线。如果线的厚度和宽度、介质的介电常数以及两层导电平面间的距离是可控制的,那么线的特性阻抗也是可控制的.

-

单位长度微带线的传输延迟时间,仅仅取决于介电常数,而与线的宽度或间隔无关

-

微带线速度块,抗干扰能力弱,带状线速度慢些,抗干扰能力强些

因为微带线一面是FR4(或者其他电介质)一面是空气(介电常数低)因此速度很快,利于走对速度要求高的信号(例如差分线,通常为高速信号,同时抗干扰比较强) -

带状线两边都有电源或者地层,因此阻抗容易控制,同时屏蔽较好,但是信号速度慢些。

-

通常同样的介质条件微带线的损耗小(线宽),带状线的损耗大(线细,有过孔)。

-

当设计一个电路板时,首先要考虑的是需要多少布线层(routing layer)及电源平面(在可接受的成本价格内)。层数之决定在于功能规格、杂讯免疫力、信号分类、需布线之net、trace数目、阻抗之控制、VLSI元件密度、汇流排之布线,等等。适当使用microstrip及stripline方式以在PCB层面压制射频辐射。在PCB内之平面(Ground或VCC)是压制PCB内Common-mode RF之重要方法之一,理由是这平面会降低高频电源分布阻抗(power distribution impedance)。

-

Microstrip:指PCB之外层的trace,经一介电物质邻接一整平面(solid plane). Microstrip方式提供PCB上之RF压制,同时也可容许比sctripline较快之clock及逻辑讯号。此较快之clock及逻辑讯号是因为较小之耦合电容及较低之空载传输延迟。Microstrip的缺点是此PCB外部信号层会辐射RF能量引入环境,对非在此层之上下加入金属屏蔽。

-

Stripline:信号层介于两个solid planes (Voltage或Ground)之间。Stripline有达到较佳RF辐射防制,但只能用在较低之传输速度,因信号层介于两个Solid planes之间,两平面间会有电容性耦合,导致降低高速信号之边缘速率(edge rate), Stripline之电容耦合效应在边缘速率快于1ns之信号较为显著,使用Stripline的主要效应是对内部trace之RF能量之完整屏蔽,因而对射频有较佳之抑制能力。

要注意的是辐射仍然会从其他元件产生,虽然内部之trace可不令其产生辐射,其它之内部边线(bond接线、元件脚、插座、内部连线能及其他类似者)仍会产生问题。随着系统、元件、trace之阻抗,会存在阻抗不匹配(impedande mismatch)之问题,此不匹配之阻抗会使RF能量由内部trace耦合到其他电路或是自由空间(free space)。使元件之接脚电感最小(minimizing lead impedance)可降低辐射现象。 -

微带线和带状线的阻抗计算:

a.微带线(microstrip)Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)]

其中,W为线宽,T为走线的铜皮厚度,H为走线到参考平面的距离,Er是PCB板材质的介电常数(dielectricconstant)。此公式必须在0.1<(W/H)<2.0及1<(Er)<15的情况才能应用。

b.带状线(stripline)Z=[60/sqrt(Er)]ln{4H/[0.67π(T+0.8W)]}

其中,H为两参考平面的距离,并且走线位于两参考平面的中间。此公式必须在W/H<0.35及T/H<0.25的情况才能应用。

4、布线中常用的匹配方法

长度匹配方式有很多种,以下是常见的处理方法。

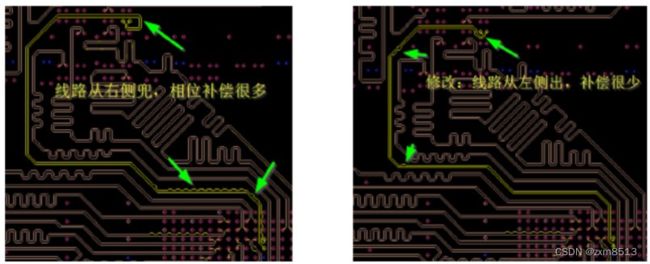

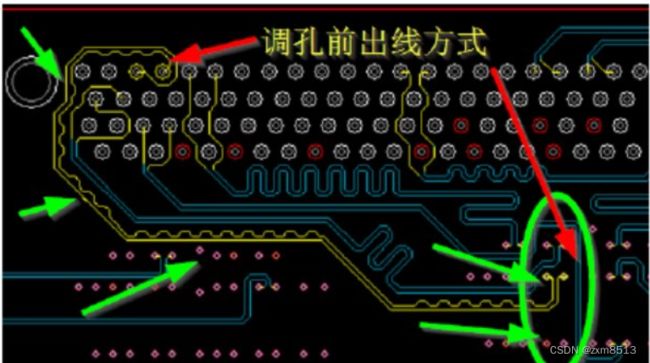

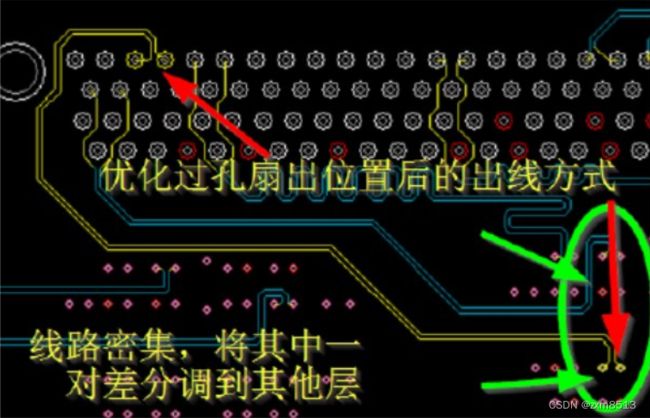

1、差分线走线时,思考最有利的出线方式,否则会增加不耦合长度、增加对内误差长度,从而影响差分信号质量。例如以下几组对比:

(1)调整一侧走线方向

(2)调整两侧走线的方向

模块化布局时,需要整整齐齐;整体布局后,结合走线情况,可以调整模块化布局时的扇出方式,使走线更合理,这里的调整也要注意美观性,不能太随意。

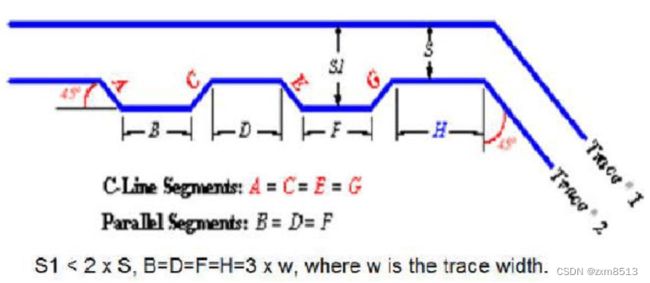

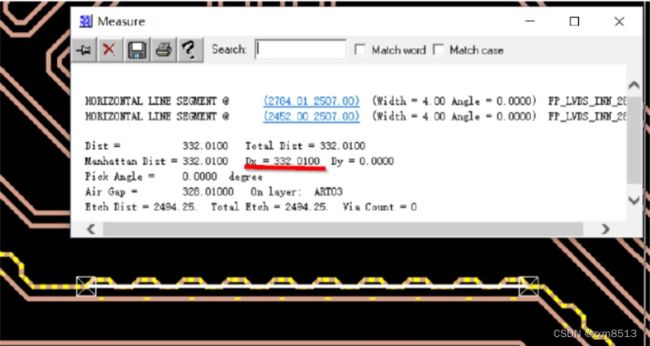

2、差分线要对内等长,本质是为了减小相位误差,原则上在线路长度不一致处进行补偿,速率越高,越要坚持此原则;对于速率不高的线路,通常习惯在阻抗不连续处 (包括不耦合处)一次补偿完,对内等长的 3W2S 原则;

3、多个小波浪要紧相邻,即上图中的 B=D=F=H;

4. 对内小波浪连续长度尽量不要超过 200mil;见下图:长度超过 200mil,此时考虑是否可以通过改变出线方式减小对内误差,或者通过在其他相位不一致处进行补偿;

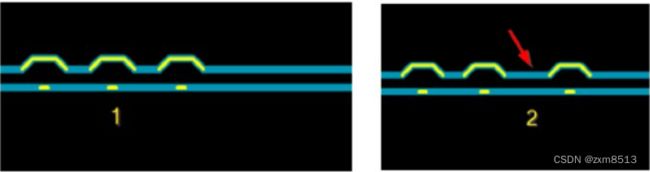

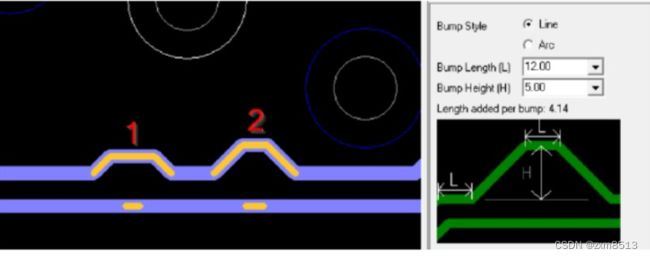

5. 小波浪要满足规范要求,下图 1 号突起满足规范,2 号不满足规范;L=3W;H=1gap;(W:差分线宽;gap:差分线的耦合间距)

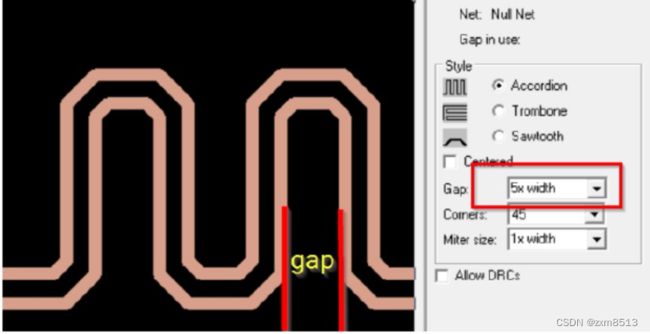

6. 绕对间等长时,gap 优先 5W;空间比较密集时,可根据情况减小;

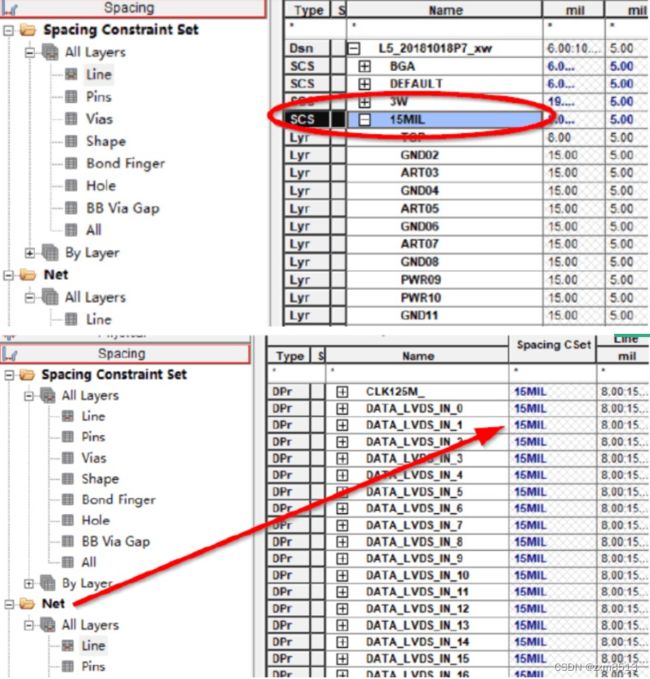

7. 差分线和其他线间距 4W 以上;一般不小于 15mil;通过间距规则进行约束;

一般差分线在出线、拐角、换层的地方容易产生长度误差,因此匹配长度的时候,尽量选择在这些点进行走线长度补偿。

另外,高速差分线除了长度需要控制之外,还需要注意所有信号必须要有一个完整的参考平面,最好是地平面。

在低频差分线布线中,有时可以使差分线跨分割,或者通过过孔换到其他层面,因为差分线中的电磁波能量大部分被控制在耦合差分对之间,参考平面的转换对其性能影响不是很大。

但是在高于 5Gbps 的信号中,高频量的辐射和损耗本身就比较严重,就不能按照低频差分的处理方式来处理高频差分。在整个高频差分的布线中,必须保持一个完整并且一致的参考平面,如果没有办法,必须换层或者跨平面,那么最好在两个参考平面之间跨接一个 0.01uF 的电容,并且使其靠近信号换层处的过孔或者连接器管脚处。