如何选择复位方式?

在一个FPGA项目设计之初,全局网络的建立至关重要,其中包括时钟网络和复位网络。而通常设计者对时钟网络的规划尤为小心,可却忽视了复位网络,这个复位跟时钟一样也是一个覆盖全局、高扇出的信号,如果处理不当也会导致意想不到的错误。很多人会问,到底复位信号选择同步还是异步、高电平还是低电平有效?对于这个问题,下文做了论述:

异步or 同步?

以下是同步、异步复位的Verilog和VHDL代码:

// 同步复位(Verilog) always@(posedge clk) if(rst) begin a<=1’b0; end else begin a<=b; end

--同步复位(VHDL) process(clk,rst) begin if clk’event and clk=’1’ then if rst=’1’ then a<=’0’; else a<=b; end if; end if; end process;

// 异步(Verilog) always@(posedge clk or posedge rst) if(rst) begin a<=1’b0; end else begin a<=b; end

--异步复位(VHDL) process(clk,rst) begin if rst=’1’ then a<=’0’; else if clk’event and clk=’1’ then a<=b; end if; end if; end process;

| 同步复位 |

异步复位 |

| 综合出来的FF面积小,需要额外的组合逻辑 |

无需额外的组合逻辑 |

| 需要时钟触发,可以使电路100%的同步,可以消除毛刺的影响 |

无需时钟,但是会因毛刺发生错误复位,并且易出现亚稳态 |

| 脉冲宽度需要长于一个时钟周期 |

脉冲宽度无限制,快速复位 |

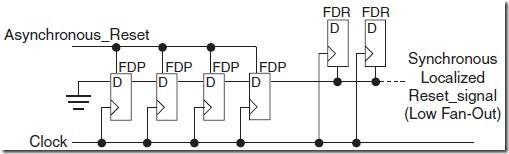

基于同步和异步复位各自的优缺点,很多经典文献都推荐一种异步复位、同步释放电路,如图1所示,此电路既节省了同步所需的额外逻辑资源又消除了异步带来的毛刺和亚稳态的影响。其中FF的数量决定了复位脉冲的宽度,图中为4个,即复位脉冲宽度为4个时钟周期。

图1

高电平 or 低电平有效?

在上文描述同步、异步复位的HDL代码中都为高电平有效复位,异步复位只要在判断条件中取个反即可。关于选择高电平有效还是选择低电平有效的复位,不像选择同步还是异步有那么些理论根据,因此有些设计者就根据个人代码编写的喜好来选择是高电平复位还是低电平复位。

| 电平标准 |

低 |

高 |

|

| CMOS |

0V ~ VDD/2 |

VDD/2 ~ VDD |

VDD=供电电压 |

| TTL |

0V ~ 0.8V |

2V ~ VCC |

VCC=5V ±10% |

TTL电平低电平和高电平是对称的,端口经常外接上拉电阻,因此由高到低的转换会快一些;并且TTL端如果在悬空状态下默认是高电平的,因此如果选用低电平有效复位抗干扰能力比较好。

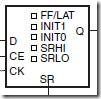

反观FPGA的逻辑,最近在研究Xilinx 7系列FPGA的结构,其中复位可以通过两种方式实现:全局复位网络(GSR)和普通复位端,如图2所示为7系列FPGA中的Storage Element结构,它既可以配置成Flip-Flop也可以配置成Latch,由输入端D、输出端Q,三个控制信号时钟使能CE、时钟CK和置位/复位SR组成;内部还有INIT0、INIT1、SRLO和SRHI 四个选项,其中INIT0和INIT1配对,表示通过GSR全局复位,此复位网络是异步的,并且铺设在整个芯片区域,属于硬核,用户无法自定义修改;而SRLO和SRHI配对,表示高电平有效信号SR驱动的复位,此信号可以配置成异步或者同步,根据此特性,如果使用低电平有效的复位,实现时则需要在SR端额外加入一个非门,因此在7系列FPGA设计时推荐使用高电平有效的复位。

图2

选择高还是低,需要根据具体的电平标准、器件结构来选择,并不是一概而论低电平有效的好或者高电平有效的好。

注:另外在设计中复位信号有时可能出现一些问题。

1. 如果在一个设计的顶层定义了一个异步复位信号,而为了减小高扇出的影响,可以将这个复位信号分配到全局布线资源上。

但是有些情况下,使用全局复位信号可能导致recovery和removel时序问题。如图4所示使用级联复位结构,将异步复位信号同步释放,根据模块进行分区,在每个分区内再级联同步释放结构,这样可以降低复位信号的扇出,从根本性上解决了问题。

图4

2. 往往在一个大系统中有多个时钟,是否需要为每个时钟域分配一个复位?如果只有一个全局复位,当然在这种情况下肯定是异步复位,它与系统中所有时钟都没有关系,并且必须满足所有时钟域的时序要求,同时满足所有时钟域的recovery和removel时序在某些情况下就不是那么容易了,因此为每个时钟分配复位是有必要的,如图5所示,此结构使用了一个全局复位,在不同时钟域分别对其进行同步,这样满足所有时钟域的时序应该是轻松些了。

图5

参考文献:

Clifford E. Cummings, Asynchronous & Synchronous Reset Design Techniques

Xilinx White Paper, WP272 Get Smart About Reset: Think Local, Not Global

Xilinx User Guide, 7 Series FPGAs Configurable Logic Block