AXI4-Stream Switch IP核介绍

此介绍是把IP核手册直接用有道翻译的,有一些语病,不影响大概意思。

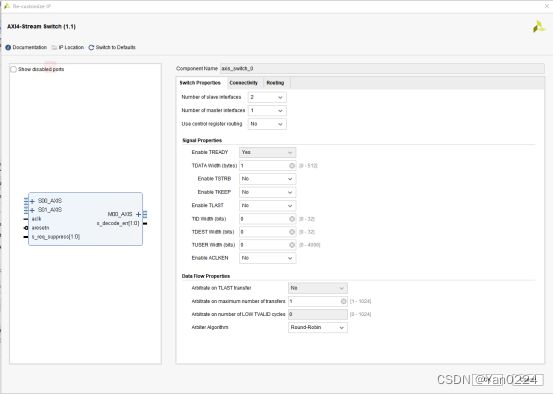

一.IP核设置

Switch Properties

Number of Slave Interfaces

此参数指定IP上存在的AXI4-流从接口的数量。这个值可以为1和16。当主接口数为1时,此值不能设置为1。

Number of Master Interfaces

此参数指定IP上存在的AXI4-流主接口的数量。 该值可以为1和16。当从属接口数时,此值不能设置为1 是1。

Use Control Register Routing

此参数指定路由模式。控制寄存器路由启用AXI4-Lite 控制寄存器接口来处理传输路由。如果将此选项设置为“否”,则为内联TDEST值用于路由。启用此选项将禁用“路由”选项卡。

Signal Properties

当使用Vivado IP积分器时,Vivado IDE会自动计算这些参数的值。

TDATA Width (bytes)

此参数指定所有AXI4-流上的TDATA信号的字节宽度 界面此参数是整数,可以从0到512。设置为0以省略TDATA信号。如果省略TDATA信号,则也省略TKEEP和TSTRB信号。端口的宽度乘以8可以得到位的宽度。

Enable TSTRB

如果设置为“是,则此参数指定可选的TSTRB信号是否存在于所有的 AXI4流接口。此选项只能在TDATA宽度(字节)时启用 参数取值大于0。

Enable TKEEP

如果设置为“是,则此参数指定可选的TKEEP信号是否存在于所有的 AXI4流接口。此选项只能在TDATA宽度(字节)时启用 参数取值大于0。

Enable TLAST

如果设置为“是,则此参数指定可选的TLAST信号是否存在于所有的 AXI4流接口。

TID Width (bits)

如果大于0,此参数指定所有AXI4-Stream接口上是否存在可选的TID信号。值为0将省略这个信号。值1和32相应地设置该信号的宽度。

TDEST Width (bits)

如果大于0,此参数指定所有AXI4-Stream接口上是否存在可选的TDEST信号。值为0将省略这个信号。值1和32相应地设置该信号的宽度。

TUSER Width (bits)

如果大于0,此参数指定所有AXI4-Stream接口上是否存在可选的TUSER信号。值为0将省略这个信号。值1和32相应地设置该信号的宽度。

Enable ACLKEN

如果设置为“是”,则此参数指定可选的ACLKEN信号是否包含所有AXI4-流接口时钟。

Data Flow Properties

数据流属性选项只有在从属接口的数量时才可以修改 是否大于1,并且使用控制寄存器路由被设置为No.

Arbitrate on Maximum Number of Transfers

此设置指定在放弃授予的传输之前要计算的传输数仲裁如果设置为零,则数字是无限的,必须设置TLAST传输的仲裁。如果设置为1,则在每次传输后,互连开关放弃控制并请求另一个仲裁。如果设置为大于1的值,则在指定的转移次数之后,将放弃仲裁。例如,将此值设置为16允许每个仲裁授予16个传输从从接口传递到主接口。

Arbitrate on Number of LOW TVALID Cycles

这种设置允许在不转让的情况下放弃已授予的仲裁。看门狗计时器,并计算授予的SI和MI接口连续LOW TVALID信号的数量。当按照这里指定的方式计算必要的低TVALID周期数时,开关将放弃已授予的仲裁,并向仲裁者发出交易已完成的信号。如果此设置设置为0,则没有实例化看门狗计时器。如果有多个从接口、多个主接口,且最大传输数上的仲裁率设置大于1,则此设置不能设置为零。这将确保不会发生死锁。

Arbitrate on TLAST Transfer

如果选中此选项,此设置表示当使用断言的TLAST的传输从从接口传递到互连交换机的主接口时,事务已完成。然后,仲裁者就可以向下一个仲裁的获胜者进行仲裁。

Arbiter Algorithm

有三种仲裁算法可供选择。真正的循环算法以循环的方式在所有从接口之间进行仲裁。如果所有的从接口都不是活动的,那么它将适应于为每个活动的从接口提供一个相等的权重。排序从S00开始,然后是S01,下降到S15。最后授予的接口之后的从接口具有最高的优先级。循环算法的操作方式与真正的循环选项类似,只是在成功授予后,不管授予了哪个从属接口,它都会进入下一个仲裁命令。固定优先级算法对每个仲裁周期发出S00的最高优先级,对S15发出最低优先级。必须仔细理解固定优先级算法的系统级流量配置文件,以避免低优先级端口的饥饿。

考虑到有一个带有S00、S02和S03端口的4 SI到1 MI交换机的场景 持续地请求具有大规模交易的转移。经过大量的研究 仲裁时,该算法产生不同的用途。真正的循环为S00、S02和S03端口提供了33%的可用带宽。循环算法为S00和S03端口提供25%的可用带宽,为S02端口提供50%的可用带宽。这是因为端口S02获得了端口S01的带宽。固定优先级算法为端口S00提供100%的带宽,并饿死其他2个请求端口。

无论仲裁器算法如何,仲裁器都不支持来自同一从属接口的背靠背传输。此配置有两个含义。如果只有一个接口请求到一个特定的主节点,那么就只能实现50%的带宽。如果在前面描述的场景中使用固定优先级仲裁,那么端口S00和S02将获得50%的带宽分配。

Pipeline Registers

当使用“Use control register routing”设置为“Yes”时,可以设置管道寄存器选项。

Enable Input Pipeline Register

启用时,交换机的从接口侧在IP边界处有每个端口的寄存器片。

Enable Output Pipeline Register

启用时,交换机的主接口侧在IP边界处的每个端口都具有寄存器片。

Connectivity

Slave to Master Interface Switch Connectivity Map

交换机配置如图4-11所示,可以优化交换机的连通性。默认情况下,完全连接是启用的,这意味着每个从接口都连接到每个主接口。取消选中复选框将删除该列中列出的从接口到该行中主接口的连接。当知道从接口永远不会向特定的主接口发送传输时,删除连接是可取的。这消除了不必要的逻辑,从而减少了区域利用率、路由和逻辑复杂性。

IMPORTANT: 任何接口都不应该没有连接性。每个从接口必须至少连接到一个主接口。相反,每个主接口必须至少连接到一个从接口。

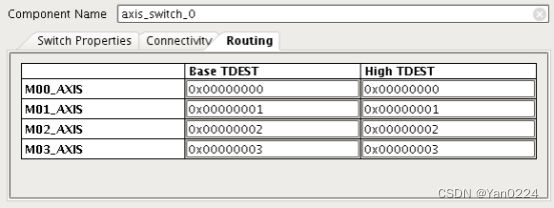

Routing

Routing Parameters

图4-12所示的路由参数设置了交换机根据TDEST信号将从接口传输到主接口所使用的解码。每个主接口的BASE/HIGH范围必须在前面指定的TDEST宽度的有效宽度内。BASE/HIGH对不能重叠主接口。当从接口接收到传输时,TDEST根据该表进行解码。然后将请求发送到与TDEST对应的主接口的仲裁器。如果仲裁程序选择了从接口,则传输继续到主接口。此选项卡仅在“使用控制寄存器路由”设置为“No”时可用。

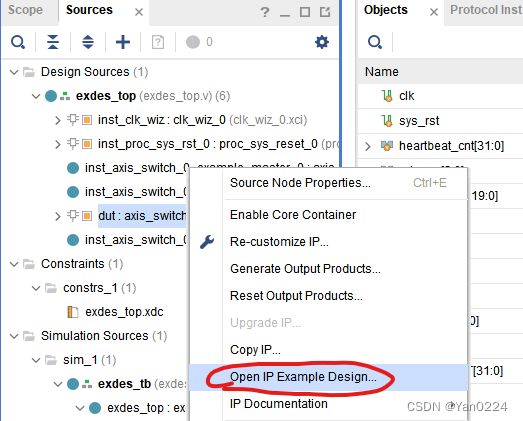

二.IP核示例

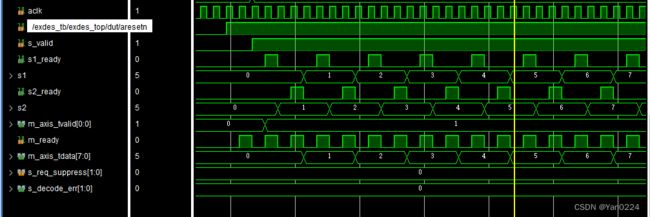

仿真结果:

从图中可以看出,此时是两个从端valid持续拉高,随着主端口的ready不断输入,switch会依次读取两个从端口的数据。如果控制从端valid的输入,也可以做到读完一通道再读取二通道。