【DRAM存储器一】基本存储单元、阵列结构、读写原理

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《Memory Systems - Cache, DRAM, Disk》

目录

最小存储单元

存储阵列结构

读写过程

最小存储单元

DRAM存储器的基本原理相信但凡有接触过DDR的都略知一二了,但是其基本存储原理是学习某存储器的基础,有了这个基础才能更好地理解整个存储器的框架,所以这里还是要啰嗦一个章节。

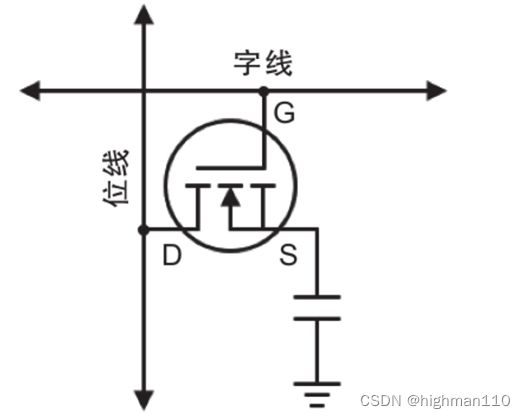

DRAM的基本存储单元是一个MOSFET加一个电容,通常称为一个cell,这个电容的容量一般是皮法级别,在90nm工艺下,为30pf。如下图:

这个结构和我们之前介绍过的EEPROM存储器的结构类似,现在把EEPROM的基本存储单元也贴出来。如下图:

可以看到从EEPROM到DRAM就是把存储单元从浮栅晶体管换成了电容,这样做一是电容的占地面积比浮栅管更小,容量能做大,二是电容的充放电速度比浮栅要快很多,更适合做内存。

存储阵列结构

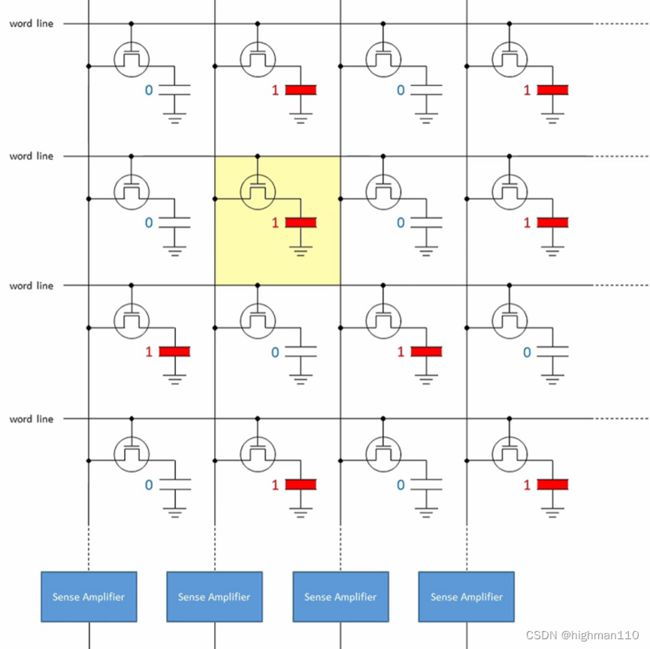

DRAM存储器内部的存储阵列就是由大量上述基本存储单元组成,如下图所示:

每一行连着一串MOS管栅极的线称为字线,每一列连接MOS管漏极的线称为位线,只要选中对应的字线和位线,就能直接访问对应的存储单元,这是几乎所有半导体存储器的访问基本原理。关于字线、位线的选择与颗粒封装上的地址线、数据线的关系,这个我们后面介绍。

从上面的阵列图可以看到,每个存储单元的状态存储在电容中,电容器上的低电压表示0,高电压表示1。在实际的DRAM设备中,低电压接近0V,高电压通常接近1.2V(就是颗粒的DQ信号供电,如DDR4的VDDQ=1.2V),每一根字线就控制着一整行的“激活”情况,所谓行激活就是在字线上加上高电压使MOS管打开,这个高电压就是颗粒外部供的VPP(如DDR4 VPP=2.5V,DDR3外部没有供,由颗粒内部的电荷泵产生)。

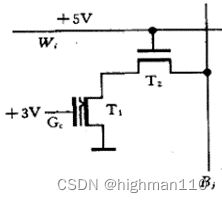

我们来看一下读取的情况,某字线被加高压,该字线控制的所有MOS管被打开,假设某电容存储的是1,MOS管打开后,电容上的电荷将流向位线,但是位线上的分布电容相对这个存储单元电容来说非常大,这么少量的电荷无法在位线上形成比较可观的电压变化,还需要在输出前增加一个放大器来使输出值达到可观测的既定水平,称为sense amplifier。感应放大器的实现如下图:

此感应放大器为差分放大器,差分放大器的两个输入端为两根位线,关于这两根位线在阵列中的分布有两种结构,一种叫Open Bitline Array Structure,其抽象布局如下图所示:

在开放式位线结构中,用于每个感应放大器的位线对来自两个单独的阵列段。开放式位线结构的阵列结构具有高度的规则性,使得开放式位线上的单元可以紧密地封装在一起。通常,开放位线结构中的DRAM单元可以占据小到6F2(F的是芯片制造工艺的最小特征尺寸Feature Size)的面积。

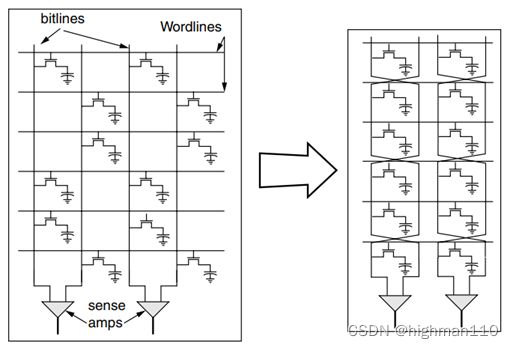

另一种叫Folded Bitline Array Structure,其抽象布局如下图所示:

可以看到折叠位线结构是先在原来的阵列中交替地删除了一些存储单元对,然后对阵列进行压缩,形成了一个有两根位线穿过阵列区的结构。可想而知,折叠位线结构的DRAM单元占地面积会比开放位线结构更大(开放位线结构只有一根位线穿过阵列区域),需要8F2。

既然折叠位线结构的占地面积更大,那这么设计的目的是什么呢?我们知道差分放大器的两个输入端理论上是要求完全对称的,这样才能发挥出其对共模干扰的良好抑制能力。在开放位线结构中,感应放大器的两个输入位线是分开的,非差分走线形式,这样外部对其形成的干扰可能只作用在某一根位线上,这就不是共模干扰,而是一个差模干扰,这种情况显然会影响感应放大器的正确输出。而折叠位线结构的差分放大器的两个输入端是差分双绞走线形式,这样外部干扰对感应放大器来说就是共模干扰,此干扰会被差分放大器抑制掉,能保证更稳定的输出。这里再提一句,针对芯片内部的差分放大器这么小范围的干扰,通常不是板级的原因,比如电源噪声、信号串扰这些,芯片内部的干扰一般来自外部射线,比如外部的α射线的撞击,这种局部撞击会产生局部电压尖峰,也就是干扰,存储器发生比特跳变的案例也是屡见不鲜。

当然,当下的DRAM阵列结构随着工艺的进步可能会与上面的两种都有所不同,总体原理应该是不变的,目标是占地面积尽量小,且抗干扰能力尽量强。

读写过程

接下来看一下DRAM阵列的读写过程:

读:

1、预充电开关闭合,旁路了感测电路,所有的位线都被充电至VDD*1/2。

2、预充电关闭,因位线上分布电容够大,其可短时间维持VDD*1/2的电压值。

3、所访问行的字线加电压VPP,打开某行,则与存储电容连接的晶体管导通。

若电容储存值为1(电平为VDD),则存储电容将向位线充电。因位线电容远大于存储电容,位线电压会冲至略大于VDD*1/2。

若电容储存值为0,则位线将向存储电容充电。位线电压将略小于VDD*1/2。

4、感应放大器将放大其两端奇偶行位线的电压差,直到一端是稳定的高电平,而另一端是稳定的低电平。其输出将锁存到行latch,由于整行都被锁存,对该行中的每一个地址的读访问不需要额外的延时(这句话应该有点问题,输出不用再锁存了,感应放大器阵列本身就是行缓冲器,详情请见后续对感应放大器结构的分析)。

5、一旦感应放大器的两端稳定,存储电容将被感应放大器的输出所刷新。由于位线较长,感应放大器电平传输到存储电容需要一定的时间。

6、一旦读取结束,字线被关闭。感应放大电路被关闭(旁路),所有的位线重新开始预充电。

写:

写和读类似,外部输入将驱动对应的位线电平发生变化,然后感应放大器将两根位线电平驱动到稳态,然后对存储电容充电或者放电。详情请见后续感应放大器功能分析文章。

本篇是DRAM存储器系列开篇,后续还有更多深度内容,敬请期待!