【第六次】21级计科计算机组成原理课外练习

【第六次】21级计科计算机组成原理课外练习

- 一、单选题

- 二、多选题

- 三、填空题

一、单选题

2-1

假定某计算机按字节编址,采用小端方式,有一个float型变量x的地址为0xffffc000,x=12345678H,则在内存单元0xffffc001中存放的内容是

A.00110100B

B.0101B

C.0001001000110100B

D.01010110B

2-2

下列关于SRAM工作原理的描述中 ,错误的是( )

A.6管SRAM中保存“1"的存储单元有两个工作管处于饱和导通状态

B.6管SRAM中保存“0"的存储单元有两个工作管处于饱和导通状态

C.对任何一个SRAM存储单元的读写,一定需要通过对应的行选通和列选通信号使与该存储单元对应的4个门控管都处于选通状态

D.现有一个1KB的SRAM存储器,若只使用其低端地址的前16个单元,则只要使用该存储器的前4位地址线,其余地址线可以不做任何端接处理

2-3

若计算机主存地址为 32 位,按字节编址,Cache 数据区大小为 32KB,主存块大小为 32B,采用直接映射方式和回写(Write Back)策略,则 Cache 行的位数至少是

A.275

B.274

C.258

D.257

2-4

设x86寄存器位数为16位,机器数采用补码形式(含1位符号位),寄存器内容默认为0。将9DH存于寄存器低字节后,寄存器内容对应真值的十进制为( )。

A.-87

B.169

C.157

D.-99

2-5

存储周期是指( )。

A.存储器的写入时间

B.存储器进行连续写操作允许的最短间隔时间;

C.存储器进行连续读或写操作所允许的最短间隔时间

D.指令执行时间

2-6

如果一个被访问的存储单元,很快会再次被访问,这种局部性是( )

A.时间局部性

B.空间局部性

C.数据局部性

D.程序局部性

2-7

某存储器容量为32K*16位,则()。

A.地址线为16根,数据线为32根

B.地址线为32根,数据线为16根

C.地址线为15根,数据线为16根

D.地址线为16根,数据线为15根

2-8

一个16K*32位的SRAM存储芯片,其数据线和地址线之和为( )

A.48

B.46

C.36

D.39

2-9

一个16K*32位的SRAM存储芯片,其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为( )

A.2^14

B.2^7

C.2^8

D.2^16

2-10

假定用编号为0-3片16K* 8位的存储芯片组成一个64K* 8位的存储器,从第0片到第3片依次使用64K存储空间中从低到高的16K空间,则编号为2的存储芯片在64K全局空间中的地址范围是( )

A.8000H - BFFFH

B.C000H - FFFFH

C.4000H-7FFFH

D.2000H-5FFFH

2-11

下列关于存储扩展的描述中,错误的是( )

A.字扩展时,存储芯片的片选信号一般由地址译码器产生

B.只做位扩展时,所有存储芯片的片选信号都固定接0

C.CPU的读写控制线应连接到SRAM的读写控制线

D.只做字扩展时,不同存储芯片相同编号的数据位(如D2)不能连接到CPU数据总线的同一位上

2-12

为实现 Cache地址映射,需要将来自CPU的物理地址根据映射方式进行不同划分,下列描述中错误的是 ( )

A.全相联映射方式下,将地址划分为主存块地址和块内偏移地址两部分

B.直接相联映射方式下,根据Cache大小将地址划分为标记(Tag)、索引(Index)和块内偏移地址三部分。其中Index指向Cache特定行位置

C.组相联映射方式下,根据Cache 分组数大小将地址划分为标记(Tag)、索引(Index)和块内偏移地址三部分。其中Index指向Cache特定组位置

D.K路组相联是指Cache被分成K组

2-13

15.假定用若干个16K x1位的存储器芯片组成一个64K x8位的存储器,芯片内各单元连续编址,则地址BFFOH所在的芯片的最小地址为_______。

A.4000H

B.6000H

C.8000H

D.A000H

2-14

16.假定用若干个16K x8位的存储器芯片组成一个64K x8位的存储器,芯片各单元交叉编址,则地址BFFFH所在的芯片的最小地址为_______。

A.0000H

B.0001H

C.0002H

D.0003H

2-15

9.需要定时刷新的半导体存储器芯片是_______。

A.SRAM

B.DRAM

C.EPROM

D.Flash Memory

2-16

10.通常采用行、列地址引脚复用的半导体存储器芯片是_______。

A.SRAM

B.DRAM

C.EPROM

D.Flash Memory

2-17

假定主存按字节编址,cache 共有64行,采用直接映射方式,主存块大小为32字节,所有编号都从0开始。问主存第2593号单元所在主存块对应的cache行号是_______。

A.1

B.17

C.34

D.81

2-18

32.假定主存按字节编址,cache共有64行,采用4路组相联映射方式,主存块大小为32字节,所有编号都从0开始。同主存第2593号单元所在主存块对应的cache组号是_______。

A.1

B.17

C.34

D.81

2-19

假定用若干块4K*4位的存储芯片组成一个8K8位的存储器,则地址1B1F所在芯片的最大地址是( )

A.1BFFH

B.1FFFH

C.1000H

D.0B00H

2-20

某计算机的存储器总线中有 24 位地址线和 32 位数据线,按字编址,字长为 32 位。若 00 0000H ~ 3F FFFFH 为 RAM 区,则需要 512K × 8 位的 RAM 芯片数为

A.8

B.16

C.32

D.64

二、多选题

3-1

下列关于局部性的描述中正确的是 ( )

A.局部性包括时间局部行和空间局部性

B.局部性是保证存储系统层次结构高效的基础

C.顺序程序结构具有空间局部性

D.循环程序结构具有时间局部性

3-2

下列关于大端与小端模式的描述中,正确的是 ( )

A.大端模式(Big-endian)是指数据的低位保存在内存的高地址中,而数据的高位,保存在内存的低地址中

B.小端模式(Little-endian)是指数据的低位保存在内存的低地址中,而数据的高位保存在内存的高地址中

C.0x12345678 按大端模式存放时,其所在存储单元最低字节单元存放的数据是0x12

D.0x12345678 按小端模式存放时,其所在存储单元最高字节单元存放的数据是0x12

3-3

在下列因素中,与Cache的命中率有关的是

A.Cache块大小

B.Cache的总容量

C.替换算法

D.主存的存取时间

三、填空题

4-1

某计算机字长32位,CPU访问按双字边界对齐的存储单元时,地址的最低三位全零,则该存储器的存储字长为( )位 64

4-2

假定主存按字节编址,cache共有64行,采用直接映射方式,主存块大小为32字节,所有编号都从0开始。问主存第3000号单元所在主存块映射到的cache行号是( )。(本题中的数字都是十进制数,答案也填十进制数)。 29

4-3

计算机主存容量8MB,分为4096个主存块,Cache数据区容量为64KB,若Cache采用直接映射方式,则Cache的总行数为 ( 只需要填写阿拉伯数字 )。32

4-4

某系统的存储器为128MB,每字块为16个字,每字64位,若cache为4MB,采用字节编址方式。问:

(1)存储器块内地址共有 7 位

(2)Cache行号地址共有 15 位

(3)采用全相联映射,块表中的主存标记位共有 20 位

(4)采用直接映射,块表中的主存标记位共有 5 位

(5)采用16路组相联映射,块表中的主存标记位共有 9 位

4-5

用16K×8的芯片构成64K×8的存储器时(地址线从1开始编号),第 16 位和第 15 位的地址分别表示1、0时,表示选中编号0-3的第2块存储芯片。(直接填数字即可)

4-6

用32K×8的芯片构成128K×8的存储器时(地址线从1开始编号),第 17 位和第 16 位的地址分别表示1、0时,表示选中编号0-3的第2块存储芯片。(直接填数字即可)

4-7

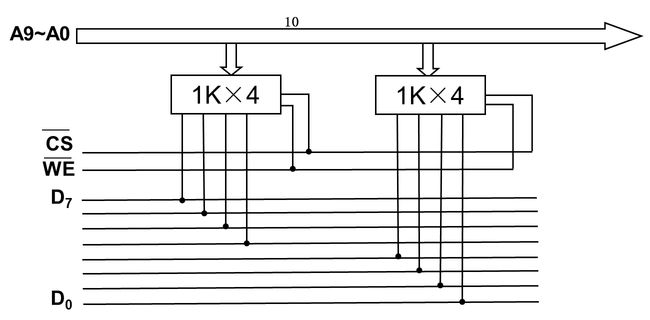

下图中显示的存储单元扩展方式是 位扩展 。(提示:填 字扩展/位扩展/字位扩展 中任一项 )

4-8

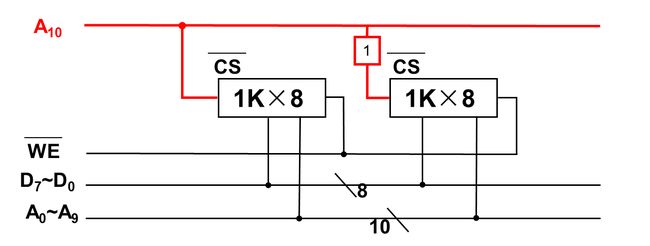

下图中显示的存储单元扩展方式是 字扩展 。(提示:填 字扩展/位扩展/字位扩展 中任一项 )

4-9

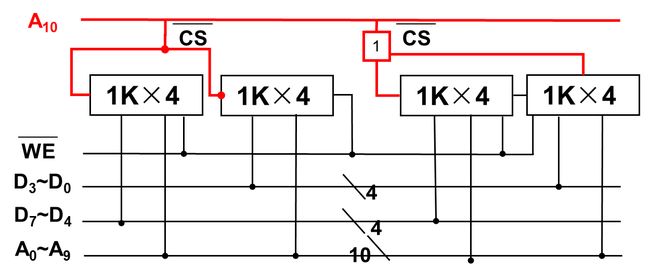

下图中显示的存储单元扩展方式是 字位扩展 。(提示:填 字扩展/位扩展/字位扩展 中任一项 )

4-10

已知cache存储周期50ns,主存存储周期200ns。cache主存系统平均访间时间为55ns.则cache的命中率= 97 %(直接四舍五入,填整数部分)

4-11

某计算机主存容量为64KB,其中ROM区为4KB,其余为RAM区,按字节编址,现要用4K×2位的ROM芯片和2K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别 4 、60 (直接填数字)

4-12

华科教材P147(2)类型1:

某容量为256MB的存储器由若干1M x 8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是 18 (填写十进制数)

4-13

华科教材P147(2)类型2:

某容量为256MB的存储器由若干16M x 8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是 20 (填写十进制数)

4-14

华科教材P148(3)类型1:

某计算机主存容量为64KB,其中ROM区为8KB,其余为RAM区,按字节编址。现要用2K x 8位的ROM芯片和4K x 4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数是 4 (填写十进制数)和RAM的芯片数是 28 (填写十进制数)

4-15

华科教材P148(3)类型2:

某计算机主存容量为64KB,其中ROM区为16KB,其余为RAM区,按字节编址。现要用2K x 8位的ROM芯片和4K x 4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数是 8 (填写十进制数)和RAM的芯片数是 24 (填写十进制数)

4-16

假定用若干个2Kx4位的芯片组成一个16Kx8位的存储器,则地址0FB1H所在芯片的最小地址是 0800 H。(填写4位十六进制数)

4-17

假定用若干个2Kx4位的芯片组成一个16Kx8位的存储器,则地址05CEH所在芯片的最大地址是 07FF H。(填写4位十六进制数)

4-18

某计算机的cache共有32块,采用八路组相联映射方式(即每组8块)。每个主存块大小为32B,按字节编址。主存201号单元所在主存块应装入的cache组号为 2 (填阿拉伯数字)。