sdf与timingCheck和后仿真

目录

1.Distributed delays

2.specify--endspecify

1.1 specify内部语法

2.sdf

2.1 sdf的格式

3.timingCheck和网表后仿真

4.关于负值delay

可以参考:

HDL抽象等级 仿真模型 网表 delay speicfy与sdf_cy413026的博客-CSDN博客

sdf和 module 里面的specify--endspecify都可以对路径延时进行赋值和检查;HDL语言中的‘#()’也可以描述延时【叫做Distributed delays】,但不能检查timing。

timing检查项可以包括 setup/hold/ recovery/ skew/ width period等。

这三种形式在描述延时 都有下面的结构:

(min:typ:max)

分别是最小,典型和最大延时,可以没有typ延时(min::max),可以只有最大(::max),也可以只有一个延时值(xxx),此时认为min/typ/max都是xxx。

如果出现(a,b)括号中用','隔开则一般表示上升沿delay为a,下降沿delay为b。

1.Distributed delays

下面两图就描述了使用 '# delay' ,来体现gate,net等时延。摘自:

Verilog中的specify block和timing check

![]()

2.specify--endspecify

其中specify--endspecify的作用如下:

一、描述横穿整个模块的各种路径及其延时。(module path delay)

二、脉冲过滤限制。(pulse filtering limit)

三、时序检查。(timing check)

1.1 specify内部语法

下图摘自Verilog中的specify block和timing check 给出了 specify的语法。

上图是添加delay信息的用法,下图则是timingCheck的用法:

详细可参考以下文档:

Verilog中的specify block和timing check - 知乎

Verilog中的specify block和timing check---cnblog

这两篇有侧重不一样的地方

2.sdf

SDF文件包含指定路径延时(specify path delay),参数值(specparam values),时序检查约束(timing check constraints),互连线延时(interconnect delay),以及一些和仿真不相关的说明信息。反标SDF文件的过程,也算是更新specify block相对应信息的过程,如果SDF文件没有包含某些信息,则参考specify block中的相应信息。

需要注意的是SDF文件制定module内部延时必须要有对应的specify

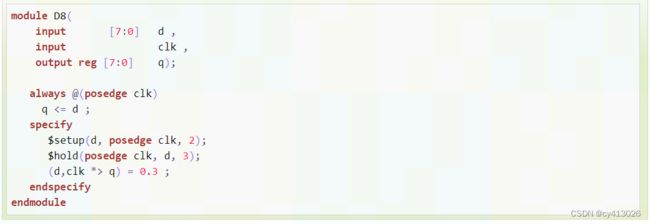

SDF 文件指定模块内路径延迟时,原模块的 specify 块必须保留,且 specify 块与 SDF 文件中指定的延迟的条件、类型等均需一致,延迟值可以不同。例如在 specify 块中无条件指定延迟:

(A => Z) = (1.3, 1.7) ;

在 SDF 文件中指定条件延迟:

(COND A==1'b1&&B==1'b1 (IOPATH A Z (1.5::1.8) (1.3::1.7)))

则在编译阶段就会报告"IOPATH from A to Z is not found."的 SDF Warning。SDF 文件设置的延迟是无效的。此处 SDF 文件也应该使用无条件的方法指定路径延迟。

上面一段摘自:Verilog 延迟反标注_一只迷茫的小狗的博客-CSDN博客

实际上sdf是工具PrimeTime生成的,自然和specify保持格式的一致,不需要手动去改写

2.1 sdf的格式

下图可以看出 第一部分给出了DELAY 第二部分给出了TIMINGCHECK。

需要说明的是SDF 3.0及后续版本 有了 setup和hold的联合检查 即“SETUPHOLD” 这种情况下是允许setup和hold为负值delay的情况,但两个值的和必须大于0。如果是单独检查SETUP,HOLD则只能是正的delay。

详细可参考以下文档:

论 STA | 可以想到的抽SDF 相关的一切-腾讯云开发者社区-腾讯云

3.timingCheck和网表后仿真

参考以下文章:

关于后仿我知道得不多

上面文章给了

1.后防的意义

2.如何反标sdf

3.如何设置vcs仿真参数

4.常见的后防warning

5.常见后防问题定位

4.关于负值delay

深度解析为什么net delay会是负值(静态时序分析基础篇) - 知乎

下面一段讲为何会有负的setup和hold delay

当ASIC Cell内部有时序器件,而Cell的输入时钟和输入数据到这个时序器件是有延时的,而且当我们以ASIC Cell为边boundary去进行timing检查时,

就有可能出现负的setup/hold time. 具体见下图。摘自关于后仿我知道得不多