【期末必备~~数电95+】数字电子技术超强超全芯片总结

目录

目录

前言

组合逻辑电路芯片

❤️74LS153(四选一数据选择)

74LS151(八选一数据选择)

74LS148(8-3优先编码器)

74LS138(3-8译码器)

74LS283(四位全加器)

CC14585(数值比较器)

时序逻辑电路芯片

️74LS175(数码寄存器)

74LS116(锁存器)

⚛️74LS194(双向移位寄存器)

74LS290(二-五-十异步计数器)

74LS161(四位二进制同步加法计数器)

74LS160(同步十进制加法计数器)

74LS190(同步十进制可逆计数器)

⚖️组合逻辑电路的芯片拓展

16线-4线优先编码器

4线-16线译码器

16选1数据选择器

前言

对于数电,不管是考试还是平常使用,我们都会遇到很多芯片,而这些芯片一个一个去查是很麻烦的,并且如果是考试,一般不会告诉你它们的功能,所以,这篇文章就会对一些常见的芯片做一个总结,包括它们的代号、逻辑图和功能。

认真仔细看完本文的小伙伴们,可以点赞收藏并评论出你们的读后感或者指出文章的错误。本博主将在今后的日子里会用心写出更多更好的文章分享,让我们共同进步!

组合逻辑电路芯片

❤️74LS153(四选一数据选择)

数据选择器(data selector) 根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。有时也把它叫做多路选择器或多路调制器(multiplexer)。

下面是74LS153的逻辑图:

芯片的功能表如下:

| S非 | A1 | A0 | Y |

|---|---|---|---|

| 1 | ~~ | ~~ | 0 |

| 0 | 0 | 0 | D0 |

| 0 | 0 | 1 | D1 |

| 0 | 1 | 0 | D2 |

| 0 | 1 | 1 | D3 |

74LS151(八选一数据选择)

功能表:

| S非 | A2 | A1 | A0 | Y |

|---|---|---|---|---|

| 1 | ~~ | ~~ | ~~ | 0 |

| 0 | 0 | 0 | 0 | D0 |

| 0 | 0 | 0 | 1 | D1 |

| 0 | 0 | 1 | 0 | D2 |

| 0 | 0 | 1 | 1 | D3 |

| 0 | 1 | 0 | 0 | D4 |

| 0 | 1 | 0 | 1 | D5 |

| 0 | 1 | 1 | 0 | D6 |

| 0 | 1 | 1 | 1 | D7 |

可见当选通端为1,无论地址输入线输入什么,输出Y总是为0

74LS148(8-3优先编码器)

74LS148 是8 线-3 线优先编码器,共有 54/74148 和 54/74LS148 两种线路结构型式,将 8 条数据线(0-7)进行 3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

逻辑图:

需要注意的地方:

1.输入当中 i7非 的优先级最高,i0非的优先级最低,在下面的功能表中也可以体现出来

2.所有均为低电平有效

3.Ys非和Yex非实现了功能的拓展

当电路工作(即S非为低电平)但无有效编码输入(即i7非到i0非均为高电平)Ys非为0,当电路工作,并且有编码信号输入时,Ys非为1

当电路工作但无有效编码输入时,Yex非为1,当电路工作并且有编码信号输入时,Yex非为0

功能表如下:

| i0非 | i1非 | i2非 | i3非 | i4非 | i5非 | i6非 | i7非 | S非 | Y2非 | Y1非 | Y0非 | Yex非 | Ys非 |

| ~~ | ~~ | ~~ | ~~ | ~~ | ~~ | ~~ | ~~ | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

| ~ | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| ~ | ~ | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| ~ | ~ | ~ | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| ~ | ~ | ~ | ~ | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| ~ | ~ | ~ | ~ | ~ | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| ~ | ~ | ~ | ~ | ~ | ~ | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| ~ | ~ | ~ | ~ | ~ | ~ | ~ | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

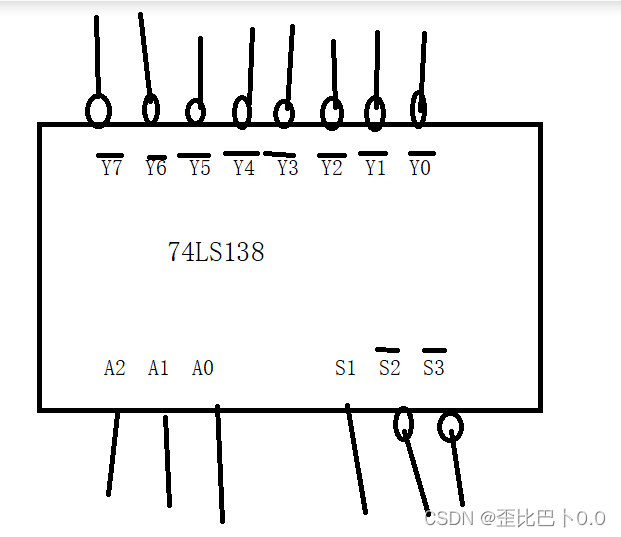

74LS138(3-8译码器)

译码器是电子技术中的一种多输入多输出的组合逻辑电路,负责将二进制代码翻译为特定的对象(如逻辑电平等),功能与编码器相反。译码器一般分为通用译码器和数字显示译码器两大类。

注意!

这个选通端有三个分别是s1 s2非 s3非,易知有效的话,应该分别设置为1 0 0

下面是功能表(均s1=1 s2非=0 s3非=0的情形,不满足的,输出全为1!与输入无关)

| A2 | A1 | A0 | Y0非 | Y1非 | Y2非 | Y3非 | Y4非 | Y5非 | Y6非 | Y7非 |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

74LS283(四位全加器)

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

提示

Ci在构成全减器中可以起到算补码的作用,而C0位进位输出,当为1时,说明,这个数的和已经无法用4位二进制表示啦

这个的功能就是两个四位二进制的相加,比较简单,不再给出功能表,在进行两数相加时,Ci的值一般设置为0

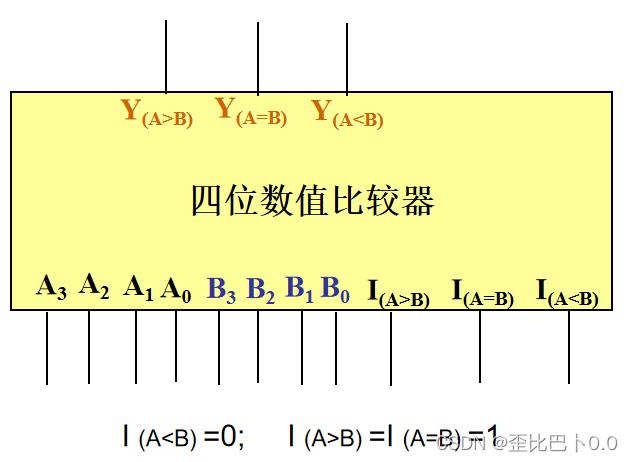

CC14585(数值比较器)

C14585是4位数值比较器,它是由单片结构上的P 沟道和N 沟道增强型器件构成。该电路具有8 个数据输入端(A0~A3、B0~B3),3 个级联输入端(AB)in,三个输出端(AB)out,该器件在此比较两组4 位字时,通过对应输出的高电平来确定该两组字是“等于”、“小于”、或“大于”。对于大于4 位的字,可通过级联电路来实现。

除了这种常规的四位数值比较器,实际上还有一种比较常见的多位的数值比较器,它的功能表如下:

这种数值比较器有着很明显的优先级,A3B3到A0B0的优先级依次减小,优先级大的只有在a=b的情况下,才能对优先级小的ab进行判断。

时序逻辑电路芯片

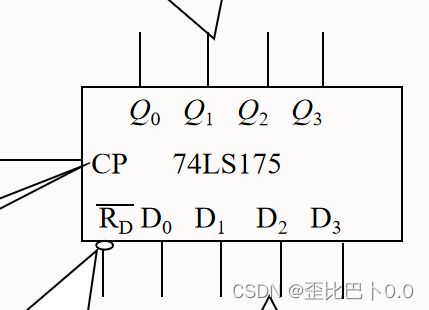

️74LS175(数码寄存器)

寄存器分数码寄存器和移位寄存器。数码寄存器是用于暂时存放数码的一种逻辑记忆电路,简称寄存器。它可以接收、暂存、传递数据。

注意:

在这个芯片中,Q为寄存数据的输出端,D为并行数据的输入端,CP为脉冲端,Rd非是一个异步清零端,当值为0时,无论D为多少,Q直接为0.

下面是它的功能表:

74LS116(锁存器)

这个对于考试要求很低,仅仅了解即可

需要注意的是,此处多了一个LEa非与LEb非,当且仅当LEa非+LEb非=0时,才能进行并数送数(无需脉冲上升沿触发)此值不为0,那么输出就会保持不变。

⚛️74LS194(双向移位寄存器)

移位寄存器(外文名:shift register)在数字电路中,是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。

移位寄存器可分为一维和多维移位寄存器。多维移位寄存器的输入、输出的数据本身就是一些列位。

分析:

双向移位寄存器有左移(又称下移)、右移(又称上移)两种状态,取决于Dir与Dil的电平,S1与S0也是一个重要的控制端,在设置的时候需要注意其特定的功能。

拓展:

74LS194通过两个芯片一定的连接可以实现相应的拓展,即可以移动更多位数的数!

此时应该进行以下的连接:

1.把两个芯片的CP、Rd非、S1、S0连在一起

2.把第一个的Q3链接到第二个的Dir,把第一个的Dil链接到第二个的Q0

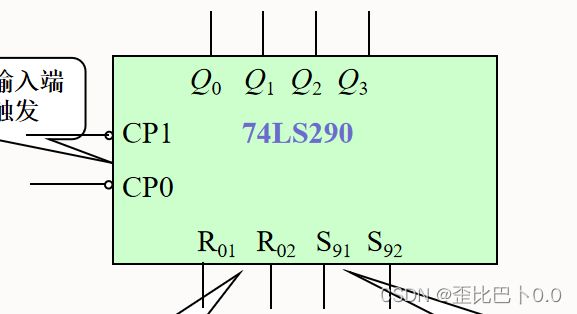

74LS290(二-五-十异步计数器)

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按运算功能不同,分为加法计数器、减法计数器和可逆计数器(也称双向计数器,既可进行加法计数,也可进行减法计数)。

它可以显示产品的工作状态,用来表示产品已经完成了多少份的折页配页工作。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数等。

☄️☄️☄️74LS290是一个重要的芯片,而且它的功能十分多,下面我将一一道来:

R01=R02=1:异步清零,无需脉冲 (Q0=Q1=Q2=Q3=0)

S91=S92=1: 异步置9,无需脉冲(Q3Q2Q1Q0=1001)

CP0=CP,CP1悬空(相当于1):Q0为二进制计数器(Q1Q2Q3不变)

CP0=CP,CP1=Q0: Q3Q2Q1Q0为十进制计数器

CP1=CP,CP0悬空: Q3Q2Q1为五进制计数器,Q0不变

74LS161(四位二进制同步加法计数器)

74ls161是一个常用的四位二进制可预置的同步加法计数器,74ls161能够在各种的数字电路上灵活运用,并且74ls161还能在单片机系统里实现分频器的一些重要功能。

可以看出,这个芯片有几个特别的输入,第一个是LD非,LD非为0是同步预置数,这个对于设计n进制加法计数器的同步置数法起着极大的作用,第二个是ET EP可以发现,只有当这两个都为1时才能进行二进制加法计数的功能,但此处是4位二进制,所有相当于16进制,也就是说当Q3Q2Q1Q0=1111时C这个进位脉冲输出端才为1

74LS160(同步十进制加法计数器)

这个与74LS161是一模一样的,只不过是10进制的,Q3Q2Q1Q0=1001时,C就会为1

74LS190(同步十进制可逆计数器)

U非/D决定了是加法还是减法,为0是加法,为1是减法

CT非决定了保持与否,低电平有效,为0时加减,为1保持

⚖️组合逻辑电路的芯片拓展

16线-4线优先编码器

左边是高位片,右边是低位片,当启用高位片时(即高位片上输出出现0),Yex非就会输出0,那么Z3就会为1,此时最右上角的Yex非也会是0,说明在工作,这里用的是与门,说明高低位片任一一个工作,总体呈现的就是Yex非为0

其余的,我们把Z2 Z1 Z0通过与非门分别和高低位片上的相应端连接,只要任一一个有0就可以输出1

最后把高位片的YS非与低位片S非相连,说明只有当高位片不工作时,才轮得上低位片工作

4线-16线译码器

左边为低位片,右边为高位片,第一步,把高位片的S2非S3非结点,工作与否全取决于S1,也就是D3,第二步,令低位片S1有效,为1,S2非S3非连D3,D3为1时,低位片不工作,然后再把D2 D1 D0如图链接就可以了,灰常地《简单》。

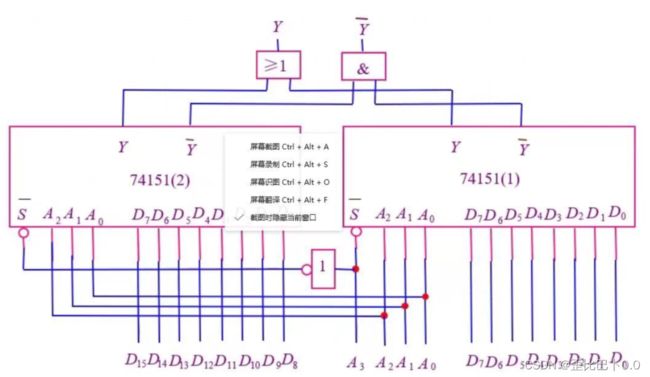

16选1数据选择器

左边高位片,右边低位片,第一步,高位片S非通过反相器与低位片S非链接,并令其为A3,说明A3=1时,可以自动启用高位片的D8~D15

第二步,直接把地址输入端两两对应链接

第三步,输出通过或门连接,两芯片只要有一个为1最终就是1

看都看完了,还不点个赞吗