一颗芯片的前世今生(4)——流片制造

今天我们讲讲芯片的流片制造那些事儿。这个流程的输入是设计的版图文件,输出是做好的芯片晶圆。

这是芯片的第四个流程。这块儿,我国65nm这个量级的做的还可以,14nm应该SMIC也凑活,先进制程7乃至5nm的商业化基本是空白。属于真正被大洋彼岸卡脖子的部分。这篇文章科普一下整个制造流程。技术部分应该比较少,所以我们讲点儿故事。管中窥豹,我们的故事不妨从台积电展开。

二、芯片的制造流程

我们扯了一堆台积电,那么台积电到底怎么用沙子把版图造成芯片的?这个流程的图我是从intel 《From Sand to Silicon》这篇文章里贴的。

step1, 挖沙子,然后做成硅锭

其中,硅要足够的纯,要9个9,99.9999999%纯度。我们为什么要用SI做芯片?也简单,硅是半导体,能做开关,世界上沙子也多,还容易提纯,与是就决定是它了。

step2, 硅锭切成硅片

将硅锭切成1mm左右一片片的wafer(晶圆)。晶圆尺寸有大有小,比如8inch, 12inch的晶圆,光刻的时候直接刻整个圆,然后切下来好多小芯片。

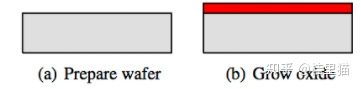

硅片切好以后,需要在上面氧化一层二氧化硅,用来做栅极。我们来看看下面的剖面图,红色的就是二氧化硅。

step3, 光刻

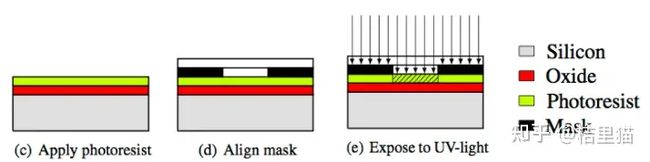

这个步骤首先在硅片上抹上一层光刻胶,一般来讲光一照,光刻胶就溶解(正胶)。然后用做好的掩模mask来照射wafer。

我们看上面这个剖面图,黄色的就是我们加入的光刻胶。黑色是我们根据版图制作出来的模板。然后用UV光去照,把光刻胶镂空。

step4, 刻蚀与粒子注入

这个步骤,我们用药水把oxide刻蚀了,然后把光刻胶洗掉,最后注入离子。

我们看剖面图。f就是刻好的oxide. 然后在洞里注入离子,形成源极和漏极。至此我们的晶体管就造好了。

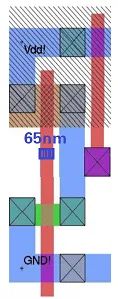

此处要插播一个小知识。我们平时说的工艺制程,比如28nm, 14nm指的是晶体管栅极宽度,也就是导电沟道的长度,不是指的线宽,最小线宽一般比制程要粗了现在。我在图上标注了65nm指的是什么。

在GDS版图上是这个距离,下面画了个非门的版图。

step5 金属线制作

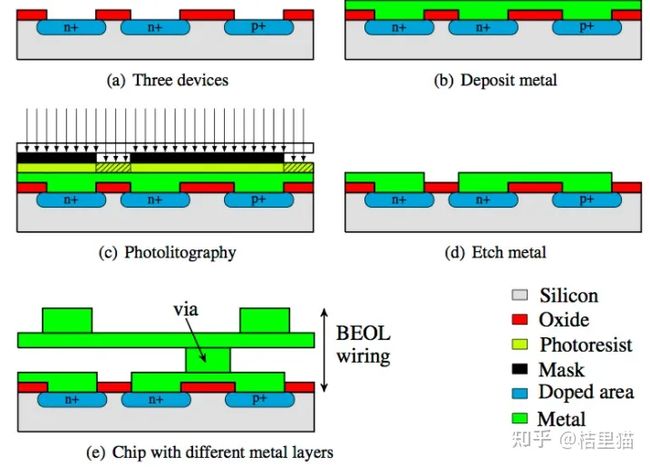

这个步骤主要是上硅片上连上金属线。这个过程我们依旧看下面的剖面图比较清楚。

看b图,首先在上面电镀一层金属,c图用光刻胶和掩膜版再刻蚀一遍得到d图,然后一层一层刻蚀叠加起来就行,层与层之间只有固定的通孔via用于连接。

step6 硅片测试与切片

接下来代工厂还要做几个事儿。

第一件事儿是先检查一下晶圆和芯片是不是好的。主要包含了两个测试。

WAT (Wafer Acceptance Test), 这个主要是测试一下晶圆的电学特性是不是正常的。WAT测试电路代工厂在流片的时候就直接加入到晶圆里了,主要包括了各种晶体管参数比如阈值电压,漏电流,电阻,电容是不是正常的。WAT的测试向量是代工厂自己搞的。

CP(Chip Probing)测试。WAT测试没问题以后,接下来进行CP测试,先用探针看看芯片是不是好的,有问题的芯片直接扔掉,免得浪费封装成本。一般会用到前面讲的DFT三把斧,sacn chain, JTAG, BIST。CP测试向量由设计商提供。如果CP不合格,直接标记出来,扔掉。

CP测试完了以后,就把芯片按照划片槽切成一个个小的芯片,装盒。寄出来了。

三、总结

实际上芯片的制作的工艺流程要复杂非常多,比如现在制程越来越小,光刻的时候量子隧穿效应非常严重,做出来模板肯定不是你想想的镂空的窗花,这里只是讲了最重要最基础的步骤。这篇文章的输入是设计的GDS, 输出是一个个芯片裸片。这些裸片没办法直接接到PCB上的,需要经过后续的封装和测试,才算是真正的芯片。