ICC 图文学习——LAB5:Route 布线

floorplan阶段,创建电源地网络时已经完成了电源地网络的布线,且给标准单元供电的rail也已经生成;routing阶段的主要内容如下:

·完成标准单元的信号线的连接

·对时序、congestion、power 和 SI 等进行优化

·进行物理验证和修复

LAB5:Route 布线

- 1. 加载设计和公共设置

- 2. 确保设计已准备好布线

- 3. 进行布线和优化

- 4. 进行DRC和LVS检查和修复

- 5. 使用GUI工具分析

相关文件的准备:

orca_lib.mw/CEL:

clock_opt_route 在CTS和布线后的ORCA_TOP设计

./scripts 本lab用到的脚本

如果遇到问题,可以使用命令脚本帮助恢复: /.soloution/run.tcl

1. 加载设计和公共设置

- 加载设计

在lab5_route目录下调用ICC,然后从库orca_lib.mw中复制名字为clock_opt的CEL,进行重新命名并打开设计,启动GUI,如下:

open_mw_lib orca_lib.mw

copy_mw_cel -from clock_opt_route -to signal_route

open_mw_cel signal_route

start_gui

注:该CEL 是 CTS 和时钟树布线后得到的结果。

- 检查库列表,验证 max 库和 min 库是否对应

在 Post-CTS ,我们一般使用 max delay 对setup 进行检查和优化,使用 min delay 对hold 进行检查和优化;而库变量一般定义在.synopsys_dc.setup 文件,所以需要检查库列表,验证每个 max 库有对应的 min 库,如下:

list_libs

- 加载公共设置

本设计在cts 和placement 阶段使用了公共设置,在route 阶段也需要加载(内部有些命令不适用于旧版本),如下:

source scripts/common_optimization_settings_icc.tcl

source scripts/common_placement_settings.tcl

source scripts/common_post_cts_timing_settings.tcl

source scripts/common_route_si_settings_zrt_icc.tcl

2. 确保设计已准备好布线

- 报告是否存在setup、hold 和逻辑 DRC 违反

report_constraint -all

由报告结果可以知道,只存在面积违反,没有setup、hold 和逻辑DRC违反

- 检查是否存在理想网络和高扇出网络

all_ideal_nets

all_high_fanout -nets -threshold 501

注:运行完命令后没有返回任何东西,表明该设计没有理想网络或扇出大于501pf。

- 验证布线方向是否符合预期,并加载TLU+文件

report_preferred_routing_direction

report_tlu_plus_files

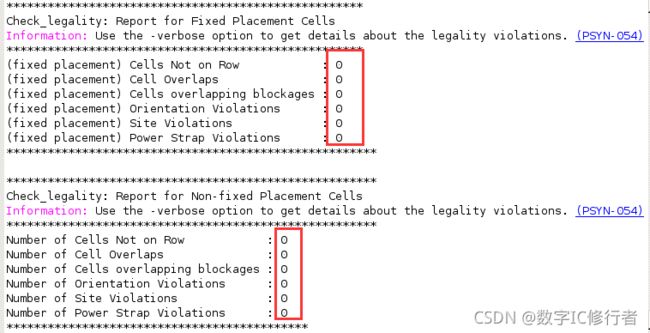

- 检查所有placement是否合法

check_legality

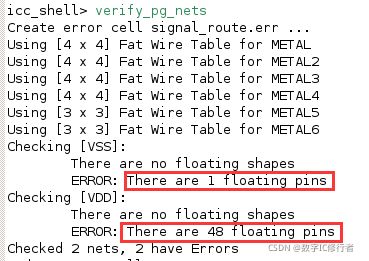

- 检查所有电源地引脚是否物理连接到 P/G 网络(是否有引脚悬空)

verify_pg_nets

我们可以通过 " error browser " 来找到问题的位置,依次选择 Layout Window—Verification—Error Browser,在弹出窗口中选择 " rail " (因为是 P/G问题),然后在 rail 空白框中选中高亮的cell,点击OK,最后单击 " Load Error Cell "底部的 OK 按钮,可以看到出现问题的原因是因为标准单元引脚缺少了VDD rail,导致VDD连接断开,使他们成为floating pins。

- 解决 P/G 连接问题(在std cell 的P/G rail上布线)

preroute_standard_cells -remove_floating_pieces

verify_pg_nets

3. 进行布线和优化

布线知识补充:

ICC有两种布线模式,一种是传统的类似于Astro中基于格点的布线方法,另一种是Zroute模式,这是对传统基于格点的布线模式的延伸,线可以不用非沿着格点进行布线。下面分别介绍这两种布线模式:

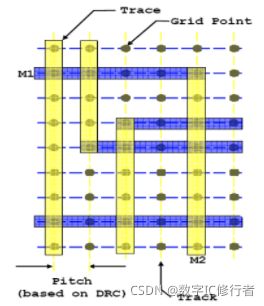

1. 首先介绍基于格点的布线理论

Track(走线轨道):图中黄色和蓝色的虚线,其没有实际的宽度,用于约束布线方向;

Pitch:两条Track之间的间距;

Grid point:两条Track的交点;

Trace:布在Track上的实际金属线,其是有宽度的,图中黄色和蓝色条。

注: 不同的金属线走线方向是不同的,一般奇数层金属默认走水平方向,偶数层默认走竖直方向。

2. Routing过程可以分为三个阶段:

·Global routing(全局布线)

·Track assignment(布线通道分配)

·Detail routing(详细布线)

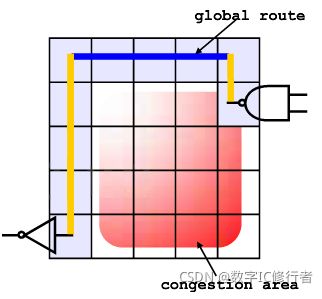

a.Global routing(GR)

全局布线,简称GR。其并没有进行任何实际的走线,而是在GRC(global route cell)上考虑拥塞的布线,为指定的的金属层和 GRC 分配线路。其主要目标有:

· 使总连接线最短;

· 布线分散均匀不致引起局部拥塞;

· 使关键路径延时最小,遵守时序规则;

· 理解信号完整性的要求,避免串扰。

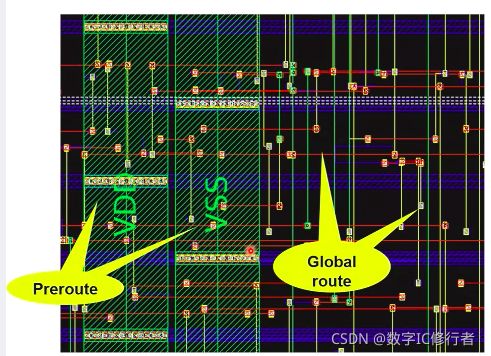

依次选择GUI—Route—Global Route,可进行全局布线,查看GR结果发现是没有宽度的细线,如下图:

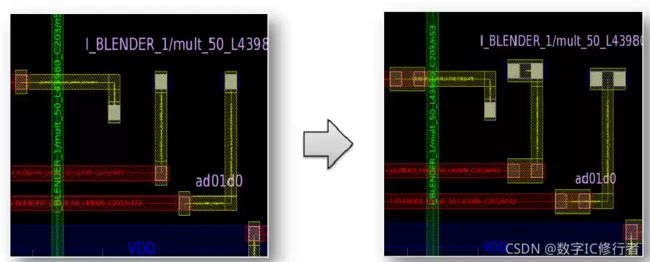

b.Track Assignment(TA)

布线通道分配,是将GR设计的每一条连线分配到一定的track上,并对连线进行实际布线,该阶段不考虑DRC问题。

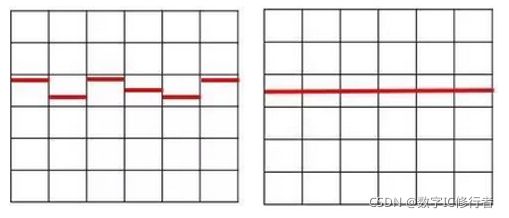

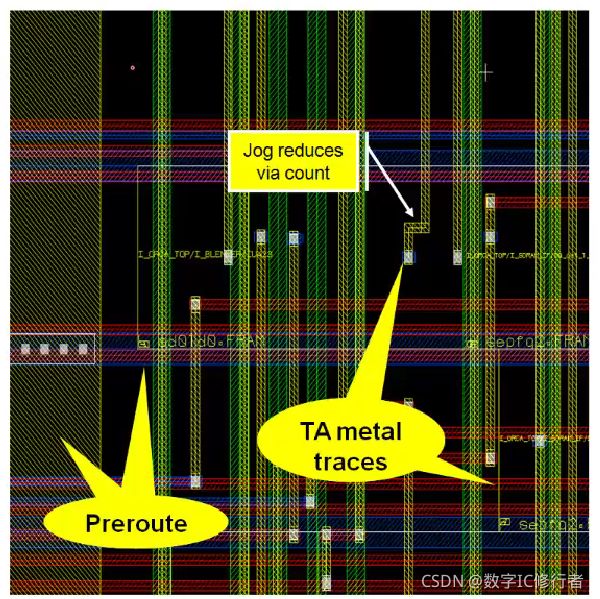

左图是GR形成的net,并没有进行首尾相连,在经过Track Assignment后,形成完整的连线,如右图。同时,在该阶段布线会尽可能走长直的金属连线,减少via通孔的个数(会形成jog,小范围改变走线方向),如下图:

注: TA阶段不会对设计做DRC检查,故存在的违例将在Detail Route阶段修复。

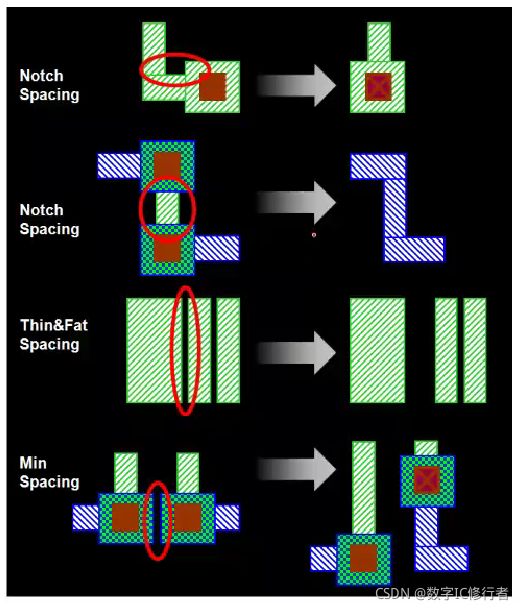

c.Detail Route

详细布线阶段主要是修复布线的物理 DRC 违反。

以上是关于exception pin知识的介绍,接下来我们将进行lab,实际运用

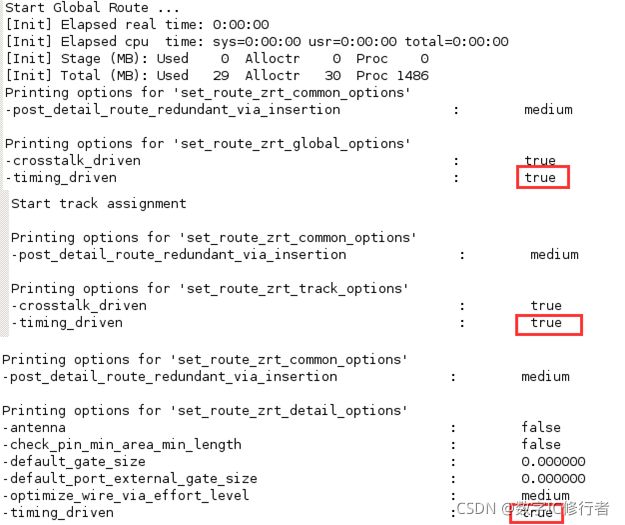

- 插入并行冗余通孔via

set_route_zrt_common_options -post_detail_route_redundant_via_insertion medium

set_route_zrt_detail_options -optimize_wire_via_effort_level medium

注: a. -post_detail_route_redundant_via_insertion 后设置为(低、中或高值),工具会在每次详细布线改变后,执行插入 via 操作,包括初始详细布线、ECO布线和增量布线。启动该选项可使设计的 via 随布线的更改而进行更新。

b. 当插入 via 通孔时,需要将命令 -optimize_wire_via_effort_level 设置为medium(默认是low)

- 检查非默认布线(NDR)规则和布线设置

report_routing_rules

report_route_opt_strategy

report_route_zrt_common_options

report_route_zrt_global_options

report_route_zrt_track_options

report_route_zrt_detail_options

- 进行初始布线(全局布线、分配布线通道和详细布线)

route_opt -initial_route_only

- 布线完成后,生成相应的报告

view report_clock_tree -summary

view report_clock_timing -type skew

view report_qor

view report_constraints -all

- 对布线进行优化,同时优化功耗

route_opt -skip_initial_route -power

注: -skip_initial_route选项可以防止初始布线被拆除和重新布线

- 确认逻辑 P/G 连接处于最新状态(布线后)

derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS -ground_pin VSS

derive_pg_connection -power_net VDD -ground_net VSS -tie

4. 进行DRC和LVS检查和修复

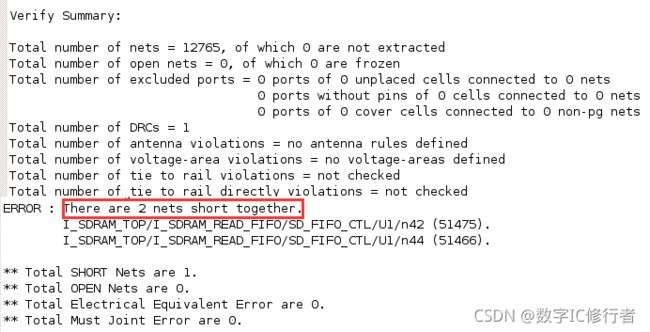

- 查看是否存在DRC 和 LVS 违反

verify_zrt_route #检查是否存在布线DRC问题

verify_lvs #检查是否存在短路

- 运行增量路径,修复短路问题

route_opt -incremental

注: 对于本设计,incremental route_opt 没有修复short,我们采用下面方案。

- 采用ECO route 修复short

route_zrt_eco

- 查看插入并行 via 通孔的的版图,并生成报告

report_design_physical -route

- 保存设计

save_mw_cel -as route_opt_final

5. 使用GUI工具分析

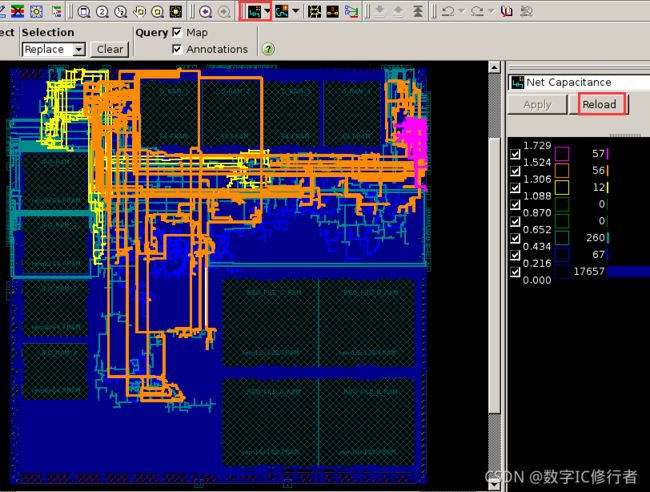

- 用 net capacitance 值对显示减小着色

依次选择菜单栏中的 " draw snapshot data on layout " — " Net Capacitance ",点击 Reload, 再点击对话框中的 OK ,不同电容阻值的 nets 用不同颜色高亮显示。

- 根据timing slack 来高亮cells

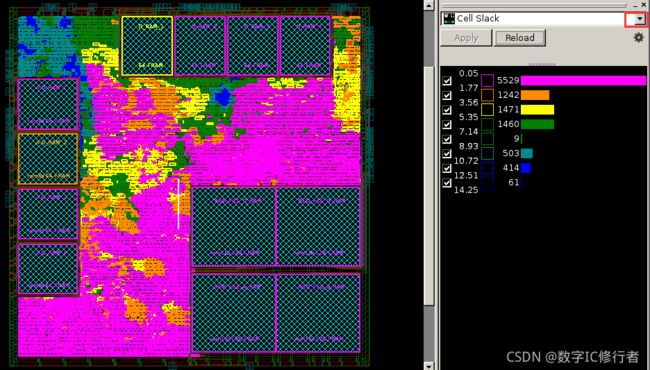

选择 " Cell Slack ",点击Reload ,再单击OK,即可得到设计的slack分布,如下

注: 通过相同方法可以查看布线后的时钟树、层次模块再版图各个位置等。