信号完整性分析与电源完整性分析学习笔记(一)

做项目开始做一些信号频率较高的板子,自学一下信号完整性分析,边学边记录,巩固学习,参考书为Eric Bogatin的《信号完整性与电源完整性分析》第三版和一些网络查阅的资料,会在相关位置附上原文链接,有错误还希望大佬批评指正。

本篇对应课本第一章

- 概论

遵循课本内容,先对信号完整性相关概念进行了解

1.1含义

广义上,信号完整性指在高速产品中由互连线引起的所有问题。可以将问题归结为以下三类:

- 信号完整性(SI):信号波形的失真。

- 电源完整性(PI):有源器件供电的互连线及各相关元器件上的噪声。是指与电源分配网络(Power Delivery Network,PDN)相关的问题。

- 电磁兼容(EMC):产品自身电磁辐射和外场导入产品的电磁干扰。

以上三个领域中6种问题:

- 单一网络信号的信号失真。

- 互连线中频率相关损耗引起的上升边退化(包含在单一网络信号中)。

- 两个或多个网络之间的串扰。

- 作为串扰特殊形式的地弹和电源弹。

- 电源和地分配中的轨道塌陷。

- 来自整个系统的电磁干扰和辐射。

具体解释见以下小结

1.2单一网络信号完整性

单一网络上的信号失真分为三个方面。

- 反射。引起反射唯一原因:信号遇到的瞬时阻抗变化,一旦发生阻抗变化,信号就在变化处发生反射。引起阻抗变化的所有特征称为突变。来源:互连线末端;线宽变化;层转换;返回路径平面上的间隙;接插件;路由的拓扑改变(分支线、T型线、桩线)。

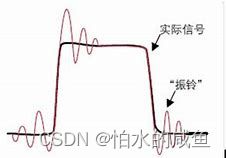

阻抗突变时产生振铃

( 在高速信号的拓扑结构中,某一个器件两端都有Trace连接到其他的器件,如chip、connector等。那么我们就把这两端中trace很短的那部份走线叫做桩线(stub)。在做layout的过程中要避免出现桩线。如果不能避免,那么就把这根trace lay短于200mil。可以较好的避免反射等影响信号质量的情况。)-百度百科

解决方法:使用均匀的传输线;控制末端反射,采用端接电阻;使用沿线拓扑的阻抗维持恒定的布线规则,点到点布线,最小化支路(例子:菊花链);对线的几何特征进行精细设计,以修正边缘场。

(端接,butt joint,是指消除信号反射的一种方式。在传输线中,当阻抗出现不匹配时,会发生反射,而减小和消除反射的方法是根据传输线的特性阻抗在其发送端或接收端进行阻抗匹配,从而使源反射系数或负载反射系数为零。通常传输线的端接采用以下两种策略,使负载阻抗与传输线阻抗匹配,即终端端接,使源阻抗与传输线阻抗匹配,即源端端接。)--百度百科

菊花链是相对最为常见的一种拓扑方式。菊花链拓扑的原理可以解释为:将所有的总线视作拓扑的干路,从处理器引出之后,每个存储设备所需要的总线视为支路,也称为“SUB线”。从微机原理的角度上讲,更像是将所有的总线视作一条“大总线”,每个内存设备需要总线的时候,直接从“大总线”中引入自己需要的数据总线、地址总线与控制总线。菊花链拓扑结构没有保持驱动端到各个负载走线长度尽量一致,而是确保各个驱动端到信号主干道的长度尽量短。菊花链拓扑结构走线的特点,牺牲了时钟、地址和控制信号的同步,但最大的特点是尽可能降低各负载分支走线长度,避免分支信号对主干信号的反射干扰。

原文链接:高速电路中菊花链、fly-by与T点拓扑_师范大学生的博客-CSDN博客_fly-by

等长走线 | 菊花链拓扑结构_明纬笔谈的博客-CSDN博客

2.互连线中频率相关损耗引起的上升边退化,即上升边被拉长。当上升边沿退化到接近信号的单位间隔时,1bit的信息将会泄漏到下一个甚至下下个bit,造成符号间干扰。

3.两个或多个信号路径之间的时延差称为错位。解决:等长线。

1.3串扰

一个网络(动态网络)上信号质量很好,一些信号也会以有害的形式耦合到第二个静态网络上。分为容性耦合和感性耦合。

容性耦合

回忆一下我们所熟悉的平行板电容,两个规则平行板导体,周围充满介质就形成了一个电容器。对于PCB板上的情况,两条走线之间和参考平面之间也会形成电容器,图3中C1表示走线和参考平面之间形成的电容,C2表示两走线之间形成的电容。从电容的角度来看,当一条走线上电压变化时,相当于电容C2两端电压变化,电容C2充电邻近的导体(电容的另一端)上必然也会有电流,串扰随之产生。走线之间的电容与走线之间的间距密切相关,当间距增大时,耦合电容迅速减小,耦合作用急剧减弱。如果在两条走线之间放入另一根走线,这两跳走线之间耦合电容会进一步减小,这种现象正是使用隔离底线抑制串扰的出发点之一。

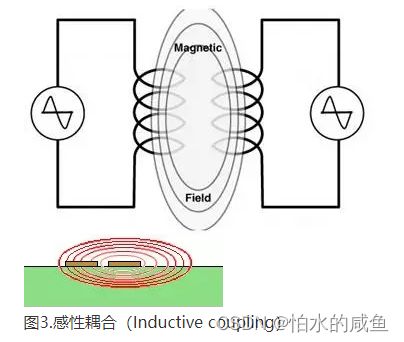

感性耦合

如果一条走线上有数字信号传输,在信号电平跳变过程中,即信号处于跳变边沿时,走线上电压不断变化,走线上的电流也不断变化,这样在走线周围产生变化的磁场,而变化的磁场在邻近走线上产生感应电流。这就是感性耦合。同样的拉开PCB板上走线的间距,能明显减小两天线之间的互感耦合。感性耦合机理如图3

原文连接https://bbs.elecfans.com/jishu_1706422_1_1.html

信号返回路径为均匀平面时的结构时实现最低串扰的结构,一旦返回路径的均匀平面发生变化,就会增加两个传输线之间的耦合噪声,例如信号经过接插件且多个信号共用的返回路径是一个引脚而不是一个平面。地弹实际上是同一个导体上返回电流重叠而出现的一种特殊情况。

1.4轨道塌陷噪声

当通过电源路径和地路径的电流发生变化(如芯片输出翻转),电源和地路径之间的阻抗产生一个压降,这个压降意味着供给芯片的电压减小,可以看作电压的突然减小或塌陷。

解决方案:将电源分配网络设计成低阻抗的。考虑一下特性:相邻电源和地分配层平面介质尽可能薄;加装多个低电感去耦电容器;封装安排多个很短的电源和地引脚;低阻抗稳压模块;封装去耦电容器;片内去耦。

1.5电磁干扰

电磁干扰问题有三个方面:噪声源、辐射传播路径和天线。

解决方法:使用屏蔽盒减少噪声;连接电缆上使用铁氧体,使用低阻抗连接的屏蔽电缆。