logisim模拟实现的微程序CPU各部件详解+分析理想流水线MIPS处理器的数据通路电路。

【如果需要circ文件,可以点赞+收藏,私信我~】

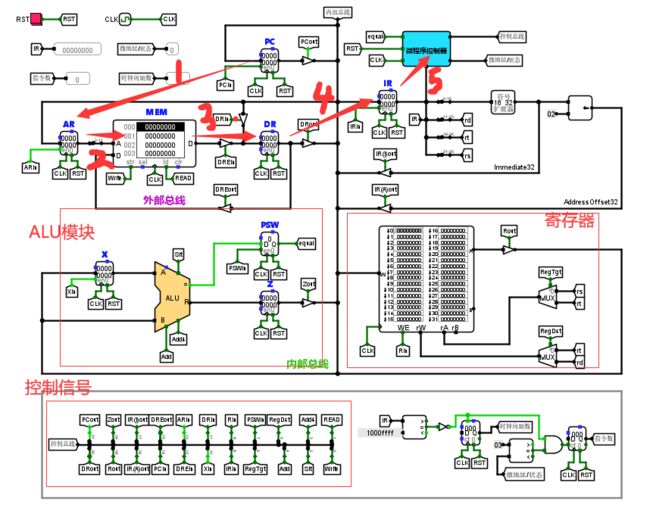

一、数据通路解析:

1、程序开始,PC中存储当前正在执行的指令地址。CPU从PC中读取指令地址,传递给AR。

2、AR将存储的地址传递给MEM。

3、MEM的控制器根据AR内容(地址)从指令地址中取指令,将指令存储到DR数据寄存器中。

4、指令被读取到DR后,将指令从DR传输到IR。

5、IR中存储该指令所有位,微程序控制器分析IR中存储的指令,依位转换成控制信号,执行相应的操作。然后PC值加1以便执行下一条指令。

Register File用于表示寄存器堆,用于读取写入和存储数据。

Register File用于表示寄存器堆,用于读取写入和存储数据。

ALU作为运算器,主要用于执行加减、比较和位移等操作。

控制信号用于控制总共22位的控制信号。

通过时钟信号(CLK)来控制PC计数器的更新,不断读取MEM随机存储器中的指令。

二、微程序控制器解析:

1、先看输入引脚,将32位的指令字传入“指令字”隧道,作为指令译码器的输入数据。

2、指令译码器输出指令译码信号(在这里是7个信号),信号传入微程序入口查找逻辑,通过分线器传入比较器。

3、比较器的使能端是测试判断电路,用于选择向后传输的是:下址字段、微程序地址还是beq分支地址。

4、微指令存入微地址寄存器uAR,控制存储器根据微地址提供的地址选择微指令,然后输出具体的控制信号。

下面分别解析:指令译码器、微程序入口查找逻辑、判别测试逻辑:

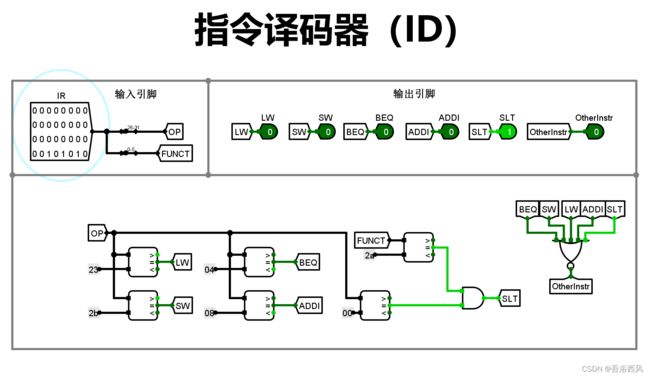

三、指令译码器解析:

输入32位的指令字,低6位是FUNCT(功能码在特定类型的指令中确定具体操作),高6位是OP(代表操作码是指令的主要类型或功能代码)。

LW(load word)将数据从内存中读取到寄存器,SW(store word)将数据从寄存器存储到内存中,BEQ(Branch if equal)比较结果分支到指定的程序地址,ADDI(Add Immediate)将常量添加到寄存器,SLT(是Set Less Than)比较寄存器的值,第一个寄存器的值小于第二个寄存器值,则将特定位置1,否则置0。OtherInstr表示其它类型的指令。

插入关于比较器的用法说明:(比较器的输入接口有两个,分别为“a”和“b”,表示要比较的两个元件或信号。比较器的输出接口有三个,分别为“a=b”、“a

如图中:OP截取了IR的高6位,从右到左计算值(右端为低位,高位仅2位),在比较器中与常量的中比较,若相等,则让功能的图标被点亮。23(十六进制)相当于10 0011。2b相当于10 1011。FUNCT取IR的低6位与2a进行比较(2a相当于10 1010)。

然后将FUNCT和OP比较的结果进行相“与”运算,若FUNCT等于2a,0P等于0,SLT图标被点亮。倘若FUN

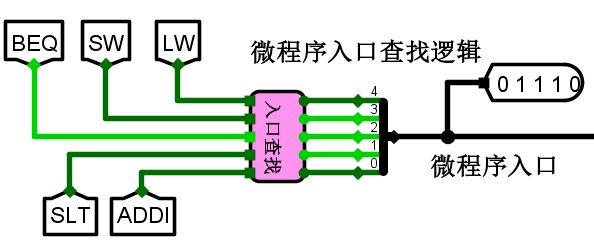

四、微程序入口查找逻辑:

下图是微程序入口查找逻辑的具体实现:

原理:根据指令的类型,会触发不同的状态位(S0~S4),通过分线器转化为一个5位数的二进制组合,依此来指示指令的类型,进而实现指令的执行和操作数的存储等功能。

五、判别测试逻辑:

主要功能是:判断当前微操作的执行条件是否满足,以决定是否执行当前微操作。常用于分支语句中,根据不同的条件选择不同的分支执行路径。

下图是判别测试逻辑的具体实现:

原理:通过返回的不同P0,P1,EQUAL的值,来生成M1,M0的值,作为多路选择器的选择端来决定要取得输入端的什么值作为后续地址?

CT和OP一个没成立,SLT都不会被点亮。

六、杂谈:

可能有同学会疑惑:当数据被传输到总线上之后,又是如何进入到各个电路组件中的。其实这个问题的关键在于:控制信号。

当数据被传输到总线上后,指令中的控制信号(写信号),会控制待写入的组件写入该数据。

如果数据在总线上经过若干个时钟周期,仍旧没有组件写入该数据,那么该数据会被后面的数据覆盖并丢失。

所以要时刻牢记:电路是一个动态的过程,由时钟信号的更新,导致控制信号不断改变,进而控制具体的组件实现不同的功能。

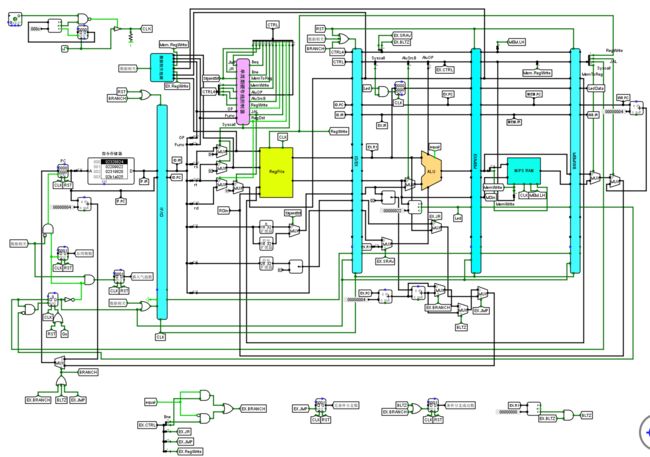

七、分析理想流水线MIPS处理器的数据通路电路:

IF段:PC寄存器保存即将执行指令的字节地址,每一个时钟周期到来,指令寄存器会根据输入的地址输出指令,IF/ID流水寄存器锁存指令寄存器取出的指令字和PC+4的值。

ID段:单周期硬布线控制器根据指令的OP和Func值,输出控制信号,统一汇入CTRL隧道。寄存器堆根据rs,rt,rd等值取操作数向后输出(还负责WB段指令执行结果的写回操作)。立即数扩展模块负责对指令0~15位的数进行扩展。ID/EX流水寄存器锁存从寄存器堆中取出的两个操作数RS和RT与写寄存器编号并向后输送。

EX段:逻辑运算单元ALU负责计算运算结果。分支地址计算模块生成跳转地址,与IF段PC+4的值进行选择,作为PC下一次指令的地址。EX/MEM流水寄存器锁存ALU运算结果、数据存储器待写入数据WriteData写寄存器编号向后输送。

MEM段:数据存储器读写模块A接口用于接收地址,D接口用于接收待写入数据,str是写使能信号,D接口用于输出存储的数据。MEM/WB流水线寄存器锁存ALU运算结果,数据存储器读出的数据和写寄存器编号并向后输送。

WB段:寄存器写回控制模块向寄存器堆写回数据。

八、分析理想流水线MIPS处理器的4个流水寄存器电路

流水寄存器主要的功能是:锁存值和向后输送。

IF/ID流水寄存器:IRin32用于锁存指令字,PCin32用于锁存PC+4的值,IRout32和PCout32用于向后输送值。

ID/EX、EX/MEM、MEM/WB流水寄存器:同IF/ID一样,是通过输入引脚进行数据和控制信号的输入,唯一不同的是,不同的流水线阶段传入的数据数量和位数是不同的,在此不过多赘述。

接下来我将介绍一下如何进行数据的输入:首先让上图的使能端为0,所控制的线路此时为高电平,寄存器可以接受时钟信号。只要CLK跳动1个周期,寄存器就会把左侧的输入数值输出往右侧的输出引脚,进而实现数据的锁存和传送。

那又如何进行数据的清空呢?此时不仅需要让使能端的值为0,还要让同步清零端的值为1,因为该端口所引出的导线连接MUX选择器的使能端,当为高电平时值为1,此时MUX选择的端口是地线,地线值为0,只要CLK跳动1个周期,寄存器就会把左侧全0的数值输出往右侧的输出引脚,实现数据清零。

九、分析气泡流水线MIPS处理器的数据通路电路:

数据通路的介绍见上面理想流水线MIPS处理器。差异点在于:在译码ID段加入数据相关检测,将rt,rs,Func,OP,Mem.RegWrite,EX.RegWrite等控制信号传入数据相关检测,输出是数据相关隧道,数据相关隧道传入ID/EX流水线寄存器,传入的是同步清零端,意思是如果数据相关发生冲突就将流水寄存器清空,插入气泡。

(补充:气泡流水线是通过延缓ID段取操作数的动作解决冲突问题,根源是目的操作数被更改后还未写回,又被重新当作源操作数使用。什么时候会发生冲突?比如EX段需要用到$2寄存器的值,但由于对$2寄存器的值的修改在WB段还没有写回(先写后读冲突),因此要将对$2寄存器的值的操作阻塞在ID、IF段,用插入气泡来实现。)

十、分析气泡流水线MIPS处理器的数据相关检测电路

rs传入的是ID.R1,rt传入的是ID.R2。

rs和rt用于表示当前指令的源操作数,分别是寄存器1和寄存器2的编号。主要用于比较当前指令的源操作数和前面已经发出但未执行指令的目的操作数,检测数据相关问题。

op和func值用于表示当前指令的操作码和函数码,这些值用于判断当前指令的类型,以便在检测数据相关时采用不同的处理方式。

EX.WriteReg和MEM.WriteReg值表示rs或rt在执行阶段或访存阶段的指令是否会写回寄存器,如果要写回,说明当前指令会影响后面指令,有可能会产生冲突。

如果在EX、MEM段需要写回寄存器,操作数来自源寄存器,指令类型满足要求,三者同时满足,与门高电平,上下两个与门与或门连接,只要有一个高电平,说明冲突,需要插入气泡。

十一、分析重定向流水线MIPS处理器的数据通路电路:

(补充:重定向的原理是将,EX段执行的结果,也就是已经存放在EX/MEM、MEM/WB寄存器中的正确操作数直接重定向到EX段的合适位置,作为后续操作的源操作数,而不必等到WB段写回,提高效率)

还是说说和理想数据通路的差异之处 :新增了一个重定向检测模块,输出的控制信号是ForwardR1和ForwardR2还有数据相关,其中ForwardR2连接F,F是多路选择器的使能信号,用于选择需要重定向的数据,R2是一个32位的数据,是重定向的结果,作为ALU的其中一个输入。

ForwardR1是作为后续多路选择信号的使能端,用于选择是否选择MEM/WB端流水线的数据RD作为重定向的数据。

ForwardR1用于判断ALU的X端口输入的数据是否可以从后面的执行阶段(EX)或访存阶段(MEM)中的结果中获取。ForwardR2则是判断ALU的Y端口输入的数据是否可以从后面两个阶段的结果中获取。

数据相关隧道用于判断Load-Used相关,当发生Load-Used相关需要ID/EX流水线清空自身,数据相关与或门相连,只要为高电平,即可清空流水线。

实现的原理就是:通过取不同的值,控制多路选择器输出不同的内容。以ForwardR1为例,当值为0时是无冲突,数据正常输入。值为1时是ID段与EX段冲突,所以选择输出数据的值是ALURes,也就是ALU运算的结果。当值为2时是ID段与MEM段冲突,所以输出是RD的值,相当于把MEM/WB流水线锁存的数据重定向到ALU的输入端。