system Verilog 验证测试平台编写指南——读书笔记(持续更新)

第一章 验证导论

1、基本测试平台的功能

测试平台的用途在于确定待测设计的正确性。包含下列步骤:

(1)产生激励。

(2)把激励施加到DUT上.

(3)捕捉响应。

(4)检验正确性。

(5)对照整个验证目标测算进展情况。

2、方法学基础

本书使用如下原则:

(1)受约束的随机激励。

(2)功能覆盖率。

(3)使用事务处理器的分层测试平台。

(4)对所有测试通用的测试平台,

(5)独立于测试平台之外的个性化测试代码。

3、随机化对象

1、考虑设计输入

(1)设备配置。

(2)环境配置。

(3)输入数据。

(4)协议异常。

(5)错误和违例。

(6)时延

4、测试平台

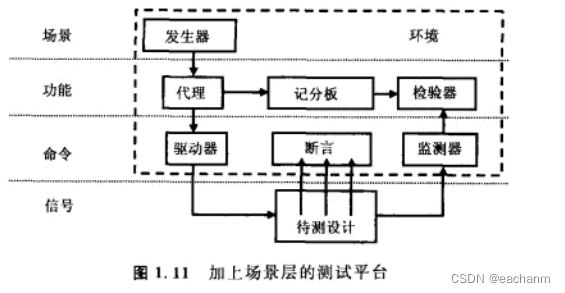

5、建立一个分层的测试平台

1、创建一个简单的驱动器

首先,来仔细看看其中的一个模块一驱动器。图1.13所示的驱动器接收来自代理的命令。驱动器可能会注人错误或者增加时延,然后再把命令分解成一些信号的变化,例如总线请求或握手。这样一个测试平台模块通常被称为“事务处理器(transactor)”,它的核心部分是一个循环:有关事务处理器的示范代码如例1.4所示。

task tun ();

done = 0;

while (! done) begin

//获取事务

//变换

//发送事务

end

endtask2、仿真环境

三个基本阶段: 建立 、 运行、 收尾。

1、建立

(1)生成配置:把待测设计的配置和周围的环境随机化。

(2)建立环境:基于配置来分配和连接测试平台构件。测试平台构件指的是存在于测试平台中的部分,注意与设计中的物理构件区分开,后者是采用RTL代码描述的。例如,如果配置选择了三个总线驱动器,那么测试平台应该在这个阶段对它们进行分配和初始化。

(3)对待测设计进行复位。

(4)配置待测设计:基于第一步中生成的配置,载入待测设计的命令寄存器。

2、运行阶段是指测试实际运行的阶段,可分为以下步骤。

(1)启动环境:运行测试平台构件,例如各种BFM和激励发生器。

(2)运行测试:启动测试然后等待测试完成。

3、收尾

(1) 清空:在最下层完成以后,你需要等待待测设计清空最后的事务。

(2)报告:一且待测设计空闲下来,你就可以清空遗留在测试平台中的数据了。

第二章 数据类型

System Verilog引进了一些新的数据类型,它们具有如下优点。

(1)双状态数据类型:更好的性能,更低的内存消耗。

(2)队列、动态和关联数组:减少内存消耗,自带搜索和分类功能。

(3)类和结构:支持抽象数据结构。

(4)联合和合并结构:允许对同一数据有多种视图(view)。

(5)字符串:支持内建的字符序列。

(6)枚举类型:方便代码编写,增加可读性。

一、内建数据类型

1、逻辑(logic)类型

S V对经典的reg数据类型进行了改进,使得它除了作为一个变量以外,还可以被连续赋值、门单元和模块所驱动。为了与寄存器类型相区别,这种改进的数据类型被称为logic。任何使用线网的地方均可以使用logic,但要求logic不能有多个结构性的驱动,例如在对双向总线建模的时候。此时,需要用线网, logic类型只能有一个驱动。

module logic_data_type(input logic rst_h);

parameter CYCLE=20;

logic g, q_1, d, clk, rst_1;

initial begin

clk = 0;

过程赋值

forever # (CYCLE/2) clk = ~clk;

end

assign rst_1 = ~rst_h;

/连续赋值

not nl(q_1,q);

/q_1被门驱动

my_dff dl(q,d,clk,rst_1);

//q被模块驱动

endmodule2、双状态数据类型

bit 无符号,另外4种 数据类型byte , shortint, int, longint 带符号

带符号的数据类型

bit b; //双状态,单比特

bit[31:0]b32: //双状态,32比特无符号整数

int unsigned ui; //双状态,32比特无符号整数

int i; //双状态,32比特有符号整数

byte b8; //双状态,8比特有符号整数

shortint s; //双状态,16比特有符号整数

longint 1; //双状态,64比特有符号整数

integer i4; //四状态,32比特有符号整数

time t; //四状态,64比特无符号整数

real r; //双状态,双精度浮点数二 、定宽数组

1、声明和初始化

定宽数组的声明

int lo hi[0:15]; //16个整数[0]..[15]

int c_style[16]; //16个整数[0]..[15]

int array2[0:7][0:3]; //完整的声明

int array3 [8][4]; //紧凑的声明

array2[7][3] = 1; //设置最后一个元素

若越界读取数组,,对于一个元素为四状态类型的数组,例如1og1c,返回的是X, 而对于双状态类型例如int或bit, 则返回0。

三、常量数组

初始化一个数组

int ascend []=(0,1,2,3); //对4个元素进行初始化

int descend[5];

descend='{4,3,2,1,0}; //为5个元素赋值

descend[0:2]='{5,6,7}: //为前3个元素赋值

ascend='{4{8}}; //四个值全部为8

descend ='(9,8,default:1); //{9,8,1,1,1)]1、基本的数组操作

例2.8在数组操作中使用for和foreach循环

initial begin

bit [31:0]src[5],dst[5];

for (int i=0;i例2.9

初始化并遍历多维数组

int md[2][3]='{'{0,1,2},'(3,4,5}};

initial begin

Sdisplay("Initial value:")

foreach (md[i,j]) //这是正确的语法格式

$display ("md[%0d][%od]=%0d",i,j,mdli);

$display("New value:")

//对最后三个元素重复赋值5

md='{'{9,8,7},'{3(32'd5}}}:

foreach (md[i, j])

//This is the correct syntax format

$display ("md[%0d][%0d]=%0d",i,j,md[i][j]);

end