FPGA-DFPGL22学习7-gpio

系列文章目录

FPGA-DFPGL22学习6-led

文章目录

- 系列文章目录

- 前言

- 一、原理图

-

- 1)key

- 2)beep+touch

- 端口对应

-

- 1)key

- 2)beep+touch

- 二、程序设计

-

- 1)KEY

- 2)beep+touch

- 三、程序编写

-

- 1.KEY代码:

- 2.beep+touch代码:

- 结论

前言

@和原子哥一起学习FPGA

开发环境:正点原子 ATK-DFPGL22G 开发板

参考书籍:

《ATK-DFPGL22G之FPGA开发指南_V1.1.pdf》

个人学习笔记,欢迎讨论

一、原理图

1)key

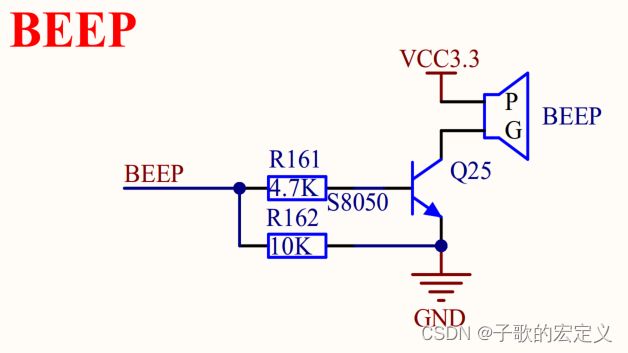

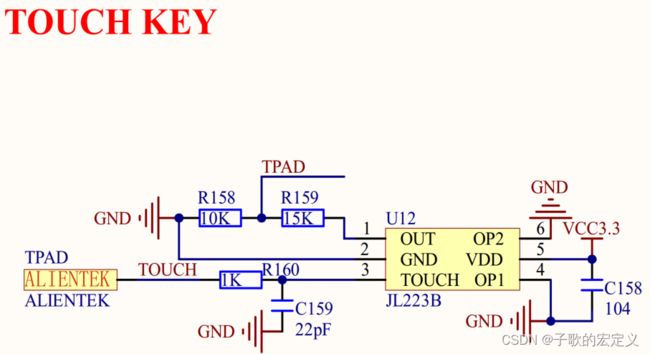

2)beep+touch

端口对应

1)key

define_attribute {p:key[0]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:key[0]} {PAP_IO_LOC} {F2}

define_attribute {p:key[0]} {PAP_IO_VCCIO} {1.5}

define_attribute {p:key[0]} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:key[0]} {PAP_IO_PULLUP} {TRUE}

define_attribute {p:key[1]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:key[1]} {PAP_IO_LOC} {H5}

define_attribute {p:key[1]} {PAP_IO_VCCIO} {1.5}

define_attribute {p:key[1]} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:key[1]} {PAP_IO_PULLUP} {TRUE}

define_attribute {p:key[2]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:key[2]} {PAP_IO_LOC} {H6}

define_attribute {p:key[2]} {PAP_IO_VCCIO} {1.5}

define_attribute {p:key[2]} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:key[2]} {PAP_IO_PULLUP} {TRUE}

define_attribute {p:key[3]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:key[3]} {PAP_IO_LOC} {G3}

define_attribute {p:key[3]} {PAP_IO_VCCIO} {1.5}

define_attribute {p:key[3]} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:key[3]} {PAP_IO_PULLUP} {TRUE}

2)beep+touch

#------------------------------touch-----------------------------------

define_attribute {p:touch} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:touch} {PAP_IO_LOC} {F1}

define_attribute {p:touch} {PAP_IO_VCCIO} {1.5}

define_attribute {p:touch} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:touch} {PAP_IO_PULLUP} {TRUE}

#-----------------------------------beep-----------------------------------------

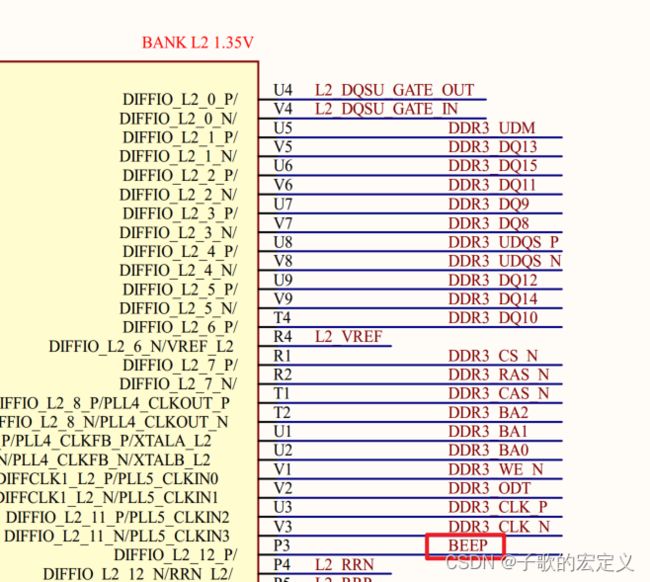

define_attribute {p:beep} {PAP_IO_DIRECTION} {OUTPUT}

define_attribute {p:beep} {PAP_IO_LOC} {P3}

define_attribute {p:beep} {PAP_IO_VCCIO} {1.35}

define_attribute {p:beep} {PAP_IO_STANDARD} {LVCMOS15}

define_attribute {p:beep} {PAP_IO_DRIVE} {4}

define_attribute {p:beep} {PAP_IO_PULLUP} {TRUE}

define_attribute {p:beep} {PAP_IO_SLEW} {SLOW}

二、程序设计

1)KEY

想要实现的效果在流水灯的基础上按下一个按键后,对应的LED灯常量

2)beep+touch

三、程序编写

1.KEY代码:

代码如下(示例):

module flow_led(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位

output reg [3:0] led,

input [3:0] key

);

reg [23:0] counter;

reg [3:0] led_contorl;

//时钟上升沿有效,复位信号下降沿有效

always @(posedge sys_clk or negedge sys_rst_n )begin

if (!sys_rst_n)

counter <= 24'd0; //非阻塞赋值,同时赋值

else if (counter < (24'd1000_0000 - 1'b1))

//else if (counter < (24'd10 - 1'b1))

counter <= counter + 1'b1;

else

counter <= 1'd0;

end

always @(posedge sys_clk or negedge sys_rst_n )begin

if (!sys_rst_n)

led_contorl <= 4'b0001;

else if (counter == (24'd1000_0000 - 1'b1))

//else if (counter == (24'd10 - 1'b1))

led_contorl <= {led_contorl[2:0],led_contorl[3]};

else

led_contorl <= led_contorl;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0000;

else if (key != 4'b1111)

led <= ~key;

else

led <= led_contorl;

end

endmodule

2.beep+touch代码:

module top_all(

input sys_clk,

input sys_rst_n,

input touch_key,

output beep

);

wire key_flag;

key_module u_key_module(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.touch_key (touch_key),

.key_flag (key_flag)

);

beep_module u_beep_module(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.beep (beep),

.key_flag (key_flag)

);

endmodule

module key_module(

input sys_clk,

input sys_rst_n,

input touch_key,

output reg key_flag

);

reg key_reg0;

reg key_reg1;

wire key_en;

assign key_en = (~key_reg1)&(key_reg0);

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

key_reg0 <= 1'b1;

key_reg1 <= 1'b1;

end

else begin

key_reg0 <= touch_key; //非阻塞赋值,同时赋值

key_reg1 <= key_reg0;

end

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

key_flag <= 1'b0;

end

else begin

if (key_en) begin

key_flag <= ~key_flag;

end

end

end

endmodule

module beep_module(

input sys_clk,

input sys_rst_n,

output reg beep,

input key_value,

input key_flag

);

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

beep <= 1'b1;

else if (key_flag)

beep <= ~beep;

end

endmodule

结论

gpio的基本操作,学习到了如何使用不同文件的实例化