PLL设计-仿真

线性相位裕锁相环模型

out都代表噪声,PFD+CP的gain是Icp/2π,LF的传输函数是![]() ,VCO传输函数是

,VCO传输函数是![]() ,分频器增益是1/N

,分频器增益是1/N

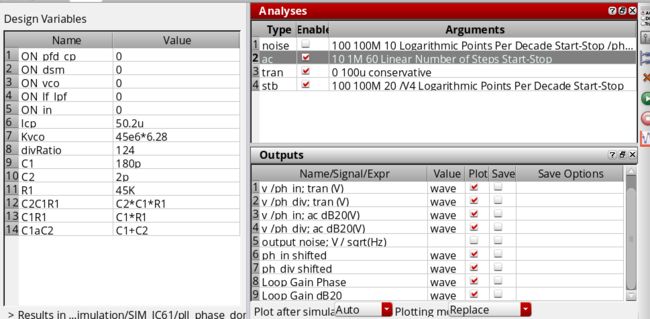

首先不考虑噪声模型

阶跃响应-查看建立时间,下面两条线是上面两条线减1V后的结果,方便查看。

放大上图,输入频率在10us处阶跃,假设25uV的时候算成功建立,输出频率在62us处与输入频率相差在接受范围内,那么建立时间为62us。

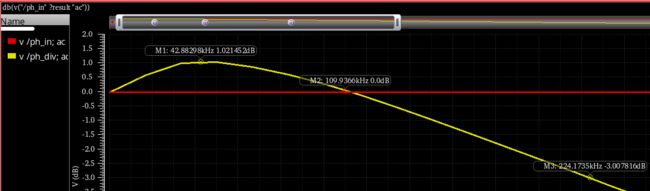

查看闭环频率响应特性,传输函数和3dB带宽

放大查看,锁相环在42kHZ处具有增益峰值,3dB带宽为224kHZ

查看稳定性,相位裕度

VCO

VCO频率为5GHZ,VCO差分输出驱动二分频器,提供正交2.5GHZ,VCO的控制有5个带选择线,共有32条频带以供选择,vunte接滤波器的输出。

VCO内部是一个LC VCO,二元加权电容器控制调频,vunte由中间的可变电容产生

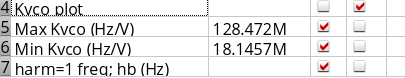

KVCO

对vunte进行扫描可以得到Kvco,VCO完整的特性需要对32条band都进行分析,这里为了方便起见,只考虑中心频率即bandNum-15时。

HB(谐波平衡)用于分析VCO在频域中精确的周期性稳态。HB分析需要对振荡频率进行初始猜测。预计本设计的中心频率为5G。Number of Harmonics 设置为自动,这样会自动确定呢谐波数,以满足精度要求标准。准确度默认值设为保守(conservative)。HB分析振荡设置需要设置振荡节点,这里选择振荡器输出信号a和b。同时禁用自动计算初始条件(ic)选项。为了在整个调频范围内表征Kvco,对vunte进行扫描,扫描范围0-1.2V,步长0.1

确保选择基频谐波频率。

下图斜率就是Kvco,send to calculate

对其求导,再调用abs函数取绝对值,画出图形

最大Kvco和最小Kvco

![]()

VCO相位噪声

VCO相位噪声用HBnoise来分析

HBnoise分析与常规噪声分析相似,不同之处在于HBnoise分析包含了变频效应。因此,它可用于预测混频器、开关电容滤波器和其他周期性驱动的噪声行为。它对预测自主(如振荡器)的相位噪声特别有用。

HBnoise将HB分析计算出的周期性工作点的电路线性化。正是线性化电路的周期性时变特性导致了频率的转换。此外,还包括周期性时变偏置点对电路中各元件产生的噪声的影响。

电路输出处噪声的时间平均值以频谱密度对频率的形式计算。在本设计中,电路的输出由一对节点vcoclk和vcoclk_n指定。

噪声分析总是计算输出端的总噪声,包括输入源和输出负载的贡献。可归因于电路中每个噪声源的输出噪声的量也被单独计算和输出。

本例中的噪声分析是对几个绝对扫频点(100>1GHz)进行计算的。最大边带场定义了用于噪声计算的最大谐波数。在实际应用中,噪声可以与HB分析中应用的周期驱动信号的每个谐波混合,并最终在输出频率处结束。

如果Ki代表边带i,那么对于周期性噪声,

![]()

对于HB分析中多音调的准周期噪声,假设有一个大音调和一个中等音调,Ki表示为[Ki_1 Ki_2]。相应的频移为

假设HB分析中有L个大色调和中等色调,一组n个整数向量表示边带

![]()

![]()

查看相位噪声

Corner

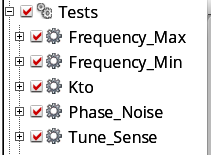

上面在标称条件下测量Kvco和相位噪声的VCO。其中标称条件是指典型工艺转角、电源电压(VDD=1.2V)和默认模拟温度(27C)的组合。实际需要做PVT仿真。用ADE XL

前2个测试分别测量最高频段(bandNum=0)和最低频段(bandNum=31)的VCO中心频率(VCO有32个重叠的调谐频段)。Kto(温度灵敏度)、相位噪声和调谐灵敏度(Kvco)。

双击第一个测试,检查完选择session-quit关闭。

工艺角

双击其中一个工艺角测试查看,检查完之后点击OK

典型进程(命名为C1_Model_MC_VCO_Temp), C2_Model_FF_VCO_Temp(快速进程)和C3_Model_SS_VCO_Temp(慢进程)。每个过程角包含3个值(最小值,类型,最大值),用于温度[-40,27,127]和电源电压[1.14,1.2,1.26]。

为了节省时间和减少要模拟的角的数量,禁用C2_Model_FF_VDD_Temp和C3_Model_SS_VDD_Temp角。禁用除相位噪声和Tune_Sense之外的所有测试。将模拟次数减少到2个测试x 9个corne= 18。

从ADE XL- window->Option->Job Setup…可以指定作业分配和并行作业的最大数量。当需要进行大量的仿真时,如corner分析、蒙特卡罗分析和电路优化时,这种能力变得尤为重要。

禁用运行标称corner。这个corner已经在corner设置中被覆盖了。点击第三个Run

想查看所有测试的一组保存的结果,Data View->History->PreLayout->Nomina-右击->Load Setup to Active

File-closed关闭

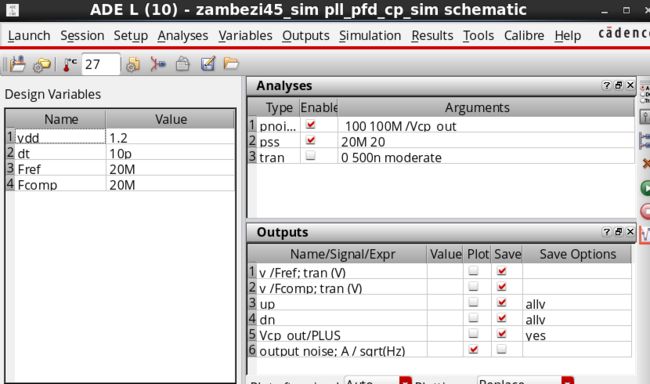

PFD/CP相位噪声

注意Fref和Fcomp的延迟时间。两个周期性噪声源被dt抵消,在ADE设置为10ps。dt越大,噪声越高。理想情况下,应该将值设置为更接近PLL锁定时的情况。

运行PSS分析,然后运行pnoise。

使用了Shooting方法,因为周期波形VFref和VFcomp是方波形状。

选择全频谱是为了让模拟器自动确定最大边带。

闪烁噪声(-10 dB/dec)和热噪声(0 dB/dec)。交汇处大概在10^5HZ

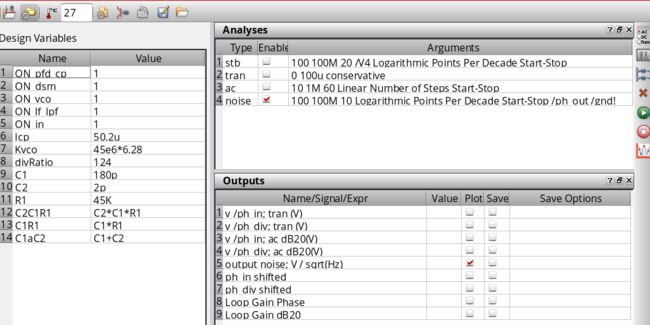

闭环PLL的相位噪声

打开所有噪声贡献者,然后依次打开单个噪声源。评估锁相环闭环总输出相位噪声和注入环路的单个块噪声源所贡献的噪声分量

VCO2G5模块表示5GHz VCO、Buffer、DIV2分频块的级联链。

参考输入相位噪声是从市售晶体振荡器估计的。相频检测器和电荷泵(PFD_CP)噪声是驱动电路PFD_CP链的晶体管级频谱噪声仿真曲线拟合。环路滤波器和低通滤波器(LF_LPF)噪声是LF_LPF链噪声分析的曲线拟合(另一种方法是使用真实的RC网络替换LF和LPF的两个svcvs分量,设置电阻参数“isnoisy =yes”,并去掉该噪声注入)。在我们的例子中,LF表示R2C2和C1并联到地的分支。LPF代表一个简单的RC滤波器,用于抑制来自Delta-Sigma调制器(DSM)的额外高频噪声。DSM噪声建模方法在下面的注释中描述。

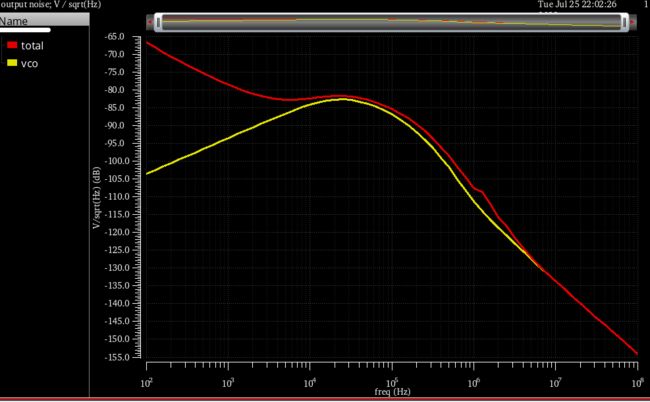

总输出噪声

查看单独各个模块的噪声贡献

注入的VCO的相位噪声通过闭环PLL传递函数对输出相位噪声进行低通滤波。

注入的Delta-Sigma模块(DSM)噪声通过闭环锁相环传递函数对输出相位噪声进行高通滤波。

使用XL分析噪声贡献

在zambez45_sim:pll_phase_domain_sim:1 test, 选择output noise V/sqrt(Hz), 右击->Plot Across Corners.

分数N-PLL功能验证

使用AMS Designer模拟器执行混合信号模拟来验证分数n锁相环的功能。包含delta-sigma调制器和校准电路的主要数字块将由verilog HDL (RTL或门verilog)表示,而其他模拟/混合信号块将由VerilogAMS模拟行为模型表示。

此功能模拟执行各种测试。它开始于一个上电序列,以便将锁相环重置到其初始默认状态。然后执行RC环路滤波和VCO校准序列。校准将需要锁定锁相环并绕过DSM电路。最后,校准电路断电,锁相环准备正常工作。

点击Simulation-Netlist and Run

Session-Design Window

左边的模块为右边的被测设备(DUT)——锁相环提供刺激。

PLL核心模块

出现SimVision控制台和设计浏览器窗口。

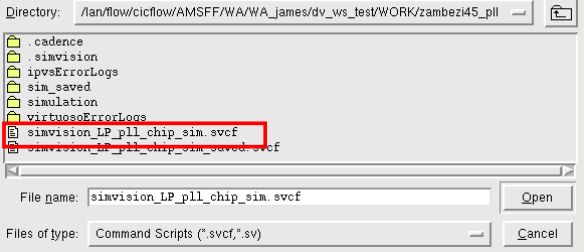

File-Source Command Script-选择 simvision_LP_pll_chip_sim.svcf,点击ok

Simulation-Run

File-Exit SimVision关闭

ADE -Session-Quit to 关闭ADE

在启动virtuoso的路径下启动simvision,输入simvision &

File-Open Database打开$PROJECT/WORK/pll_zambezi45/sim_saved/LP_pll_chip_sim/ams/config_pmc0_saved/psf

点击open&Dismiss

File-Source Command Script.打开simvision_LP_pll_chip_sim_saved.svcf

可以看到RC环路滤波器的校准结果在R修订值' h7(保存在rcal[3:0]中,起始长脉冲为1,rcal完成短脉冲为1)。

还可以看到' h0e ' VCO波段选择中的第一个VCO校准结果和' h14 ' VCO波段选择中的第二个VCO校准结果。第三个结果是h14,第四个结果是h13(保存在vcocal[3:0]中,每个startvcocal长脉冲为1,vcocaldone短脉冲为1)。

还可以看到每次目标频率设置为新频率时VCO模拟控制信号的调谐。PLL锁指示灯plllock在满足锁条件后断言1。

File-Exit SimVision

ADE-Session-Quit