6、Lctech Pi(F1C200S)4.3寸(480*272)16位RGB565LCD屏驱动适配(CherryPi,Mangopi,F1C100S)

本次主要参考:

https://blog.csdn.net/wending1986/article/details/106837597/

http://blog.chinaunix.net/uid-20543672-id-3246283.html

https://wiki.sipeed.com/soft/Lichee/zh/Nano-Doc-Backup/index.html

李山文大佬

(如果方便请给这几位大佬一个关注)

注意代码块之间的空行

如有不足之处,欢迎指出。

1、设置LCD基础参数(需要自己去根据屏幕参数进行适配)

在drivers/gpu/drm/panel/panel-simple.c文件中,第2713行开始修改如下:

static const struct drm_display_mode qd43003c0_40_mode = {

.clock = 9000,

.hdisplay = 480,

.hsync_start = 480 + 8,

.hsync_end = 480 + 8 + 4,

.htotal = 480 + 8 + 4 + 43,

.vdisplay = 272,

.vsync_start = 272 + 8,

.vsync_end = 272 + 8 + 4,

.vtotal = 272 + 8 + 4 + 12,

.vrefresh = 60,

};

部分参数含义如下:

hdisplay:有效显示区水平像素数量,对应Active Width

hsync_start:水平同步开始,对应hdispay + HFP

hsync_end:水平同步结束,对应hdisplay + HFP + HSYNC width(HPW)

htotal:水平总像素,对应hdisplay + HFP + HSYNC width + HBP

vdisplay:垂直显示像素,对应Active Height

vsync_start:垂直同步开始,对应vdispay + VFP

vsync_end:垂直像素结束,对应vdisplay + VFP + VSYNC width(VPW)

vtotal:垂直总像素,对应vdisplay + VFP + VSYNC width + VBP

vrefresh:刷新率

第2726行开始修改如下:

static const struct panel_desc qd43003c0_40 = {

.modes = &qd43003c0_40_mode,

.num_modes = 1,

//.bpc = 8,

.size = {

.width = 95,

.height = 53,

},

.bus_format = MEDIA_BUS_FMT_RGB565_1X16//MEDIA_BUS_FMT_RGB888_1X24

};

其中需要注意,参数bus_format设置为:MEDIA_BUS_FMT_RGB565_1X16;width与height为液晶尺寸。

2、配置设备树

2.1、修改suniv-f1c100s.dtsi文件

打开linux-5.7.1/arch/arm/boot/dts/suniv-f1c100s.dtsi文件。

在第38行插入如下代码:

de: display-engine {

.compatible = “allwinner,suniv-f1c100s-display-engine”;

.allwinner,pipelines = <&fe0>;

.status = “disabled”;

};

在soc->pio 下(第104行)添加如下代码:

lcd_rgb565_pins: lcd-rgb565-pins {

pins = “PD1”, “PD2”, “PD3”, “PD4”, “PD5”,

“PD6”, “PD7”, “PD8”, “PD9”, “PD10”, “PD11”,

“PD13”, “PD14”, “PD15”, “PD16”, “PD17”,

“PD18”, “PD19”, “PD20”, “PD21”;

function = “lcd”;

};

在第172~173行中间,添加如下代码:

tcon0: lcd-controller@1c0c000 {

compatible = "allwinner,suniv-f1c100s-tcon";

reg = <0x01c0c000 0x1000>;

interrupts = <29>;

clocks = <&ccu CLK_BUS_LCD>,

<&ccu CLK_TCON>,

<&osc24M>; /* Still unknown */

clock-names = "ahb",

"tcon-ch0",

"tcon-ch1";

clock-output-names = "tcon-pixel-clock";

resets = <&ccu RST_BUS_LCD>;

reset-names = "lcd";

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

tcon0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

tcon0_in_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_out_tcon0>;

};

};

tcon0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

};

};

fe0: display-frontend@1e00000 {

compatible = "allwinner,suniv-f1c100s-display-frontend";

reg = <0x01e00000 0x20000>;

interrupts = <30>;

clocks = <&ccu CLK_BUS_DE_FE>, <&ccu CLK_DE_FE>,

<&ccu CLK_DRAM_DE_FE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_FE>;

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

fe0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

fe0_out_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_in_fe0>;

};

};

};

};

be0: display-backend@1e60000 {

compatible = "allwinner,suniv-f1c100s-display-backend";

reg = <0x01e60000 0x10000>;

reg-names = "be";

interrupts = <31>;

clocks = <&ccu CLK_BUS_DE_BE>, <&ccu CLK_DE_BE>,

<&ccu CLK_DRAM_DE_BE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_BE>;

reset-names = "be";

assigned-clocks = <&ccu CLK_DE_BE>;

assigned-clock-rates = <300000000>;

ports {

#address-cells = <1>;

#size-cells = <0>;

be0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

be0_in_fe0: endpoint@0 {

reg = <0>;

remote-endpoint = <&fe0_out_be0>;

};

};

be0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

be0_out_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_in_be0>;

};

};

};

};

完成之后,保存退出。

2.2、修改suniv-f1c100s-licheepi-nano.dts文件

打开linux-5.7.1/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts文件。

在第9行插入如下代码:

#include

在第26行~27行中间,添加如下代码:

panel: panel {

compatible = "qiaodian,qd43003c0-40", "simple-panel";

#address-cells = <1>;

#size-cells = <0>;

enable-gpios = <&pio 4 6 GPIO_ACTIVE_HIGH>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

panel_input: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_out_lcd>;

};

};

};

在第40行下面,也就是文档最后添加如下代码:

&be0 {

status = "okay";

};

&fe0 {

status = "okay";

};

&de {

status = "okay";

};

&tcon0 {

pinctrl-names = "default";

pinctrl-0 = <&lcd_rgb565_pins>;

status = "okay";

};

&tcon0_out {

tcon0_out_lcd: endpoint@0 {

reg = <0>;

remote-endpoint = <&panel_input>;

};

};

完成之后,保存退出。

3、修改内核代码,配置fb

在linux-5.7.1/drivers/gpu/drm/sun4i/文件夹下,需要修改sun4i_tcon.c、sun4i_drv.c、sun4i_backend.c等文件。因为这些文件的配置是参考其他大佬给的资料完成,不予以外示。

4、uboot相关配置

本次不进行uboot的相关编译。因为在uboot启动完成到内核启动,会有花屏一闪而过。一直没有很好的解决。相关参数如下(有些为下面单词前两个字母的缩写):

xres; /* 可见分辨率 /

yres;

/ 时序: 所有值都以像素时钟为单位(当然除了像素时钟本身) /

pixclock; / 像素时钟(单位:微秒) /

left_margin; / 从行同步到图像左边沿的像素时钟数 /

right_margin; / 从行同步到图像右边沿的像素时钟数 /

upper_margin; / 从场同步到图像上边沿的行数 /

lower_margin; / 从场同步到图像下边沿的行数 /

hsync_len; / 行同步时间长度(像素时钟数) /

vsync_len; / 场同步时间长度(行数) /

sync; / see FB_SYNC_* /

vmode; / see FB_VMODE_* */

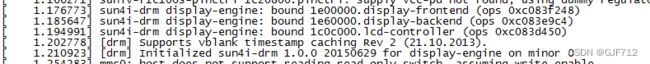

5、进行编译与运行

将编译后的zImage,suniv-f1c100s-licheepi-nano.dtb下载到sunxi-fel.exe同级目录下。

用两根type-c线将电脑与CherryPi-F1C200S连接起来,在串口终端以115200 8n1配置打开串口。

按一下板载RST键后,在windows命令终端进入到sunxi-fel.exe同级目录下,执行以下命令可以看到串口终端有log打印,LCD屏有log显示:

sunxi-fel -p uboot u-boot-sunxi-with-spl.bin write 0x80008000 zImage write 0x80c08000 suniv-f1c100s-licheepi-nano.dtb

QQ:763314235,会在第一时间处理。