2024届IC秋招兆易创新数字IC后端笔试面试题

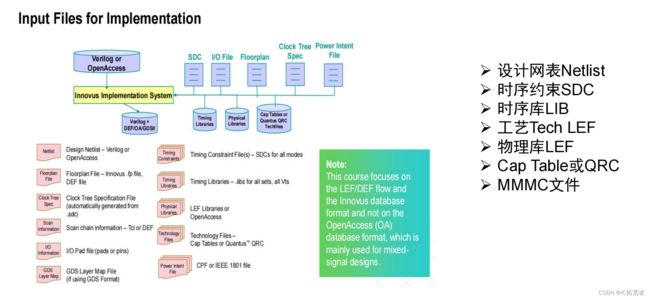

- 数字IC后端实现PR阶段设计导入需要哪些文件?

设计导入需要的文件如下图所示。这个必须熟练掌握。只要做过后端训练营项目的,对这个肯定是比较熟悉的。大家还要知道每个input文件的作用是什么。

- 在吾爱IC后端训练营Cortexa7core项目中,你认为哪个阶段是比较难的?为什么?

这道题大家可以自由发挥。一般建议从时钟树综合和PR阶段各步骤的timing一致性着手。

比如时钟树综合如何确保clock tree最短,clock skew最小。从时钟树结果分析时钟树质量出发,分享小编教大家的高亮物理路径最远的clock path的方法来确保clock tree不会整体被拖长。

timing一致性可以从咱们社区训练营案例出发,比如为何PostCTS(PostRoute)后的Timing突然会变差很多?这种两个阶段timing变化很大的问题分析思路和最终解决方案。

我们后端训练营课程直播也分享过我们powerplan metal方向和默认metal方向不一致导致的routing detour问题。这个问题也会引起不同阶段timing差异很大。

- 请列举你简历中低功耗四核A7 top这个项目中所采用的低功耗实现技术?

低功耗实现技术主要有下面这几种实现技术。咱们四核A7 top项目是用到了clock gating , Multi Vth,Power Gating,Multi-Voltage以及high effort flow的技术。

在innovus中使用high effort flow的方法见下面PPT所示。

- 在低功耗设计实现这个项目中,upf文件是在哪个阶段导入的?是通过什么命令来导入upf的?upf的主要内容包含哪些内容?

upf(Unified Power Format)文件可以在设计导入阶段读入,也可以在placement前导入。导入的命令如下:

UPF主要组成部分如下图所示。这里要求大家能够根据命令来画出下图中右侧的结构图。如果有参加低功耗训练营项目的同学,最好能够画出四核A7顶层top的对应低功耗框架图。

-

你这个后端项目包含哪些时钟?自己是否有分析过时钟结构?

一个CLK。时钟结构虽然简单,但是都学会了时钟trace的方法。

-

什么是NDR(Non-Default Rule) ? 为什么要用使用NDR? PR阶段是如何设置NDR的?

- 时钟树综合一般是采用clock inverter还是clock buffer来长clock tree? 为什么?PR工具如何控制这个长tree方式?

大部分都是使用clock inverter来做clock tree。主要是为了避免min pluse width问题。

PR阶段通过下面的命令来控制工具使用clock inverter来长tree。

set_ccopt_property use_inverters true

set_ccopt_property inverter_cells $cts_inv_cells

- 请描述Place阶段和PostCTS阶段Clock Uncertainty的组成部分 (setup和hold)

- 如果只考虑Timing,你会选用HVT,RVT和LVT中的哪类cell来优化时序?

仅仅从Timing角度考虑,肯定就使用低阈值电压的LVT cell。

- 功耗的组成部分有哪些?如何优化静态功耗和动态功耗?

- 请简单举例你写过的tcl脚本案例

可以分享咱们钉钉上分享的很多TCL脚本案例。当然最基础的就是比如我们cortexa7core的面积估算脚本。检查input floating的tcl脚本等等。

- 你有了解过除tcl外的其他脚本语言吗?

如果有学习过perl或者python,可以提一下。没有的话就说没有即可。

- 数字IC后端中的物理验证是干什么的?它主要检查哪些内容?

物理验证主要检查DRC,ERC和LVS。

- Hierarchical Flow的四核A7 Top整个flatten LVS是否pass?

是的,已经跑通整个flatten的DRC和LVS,结果均clean。

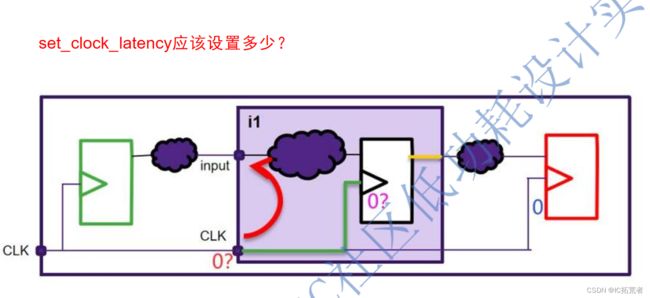

- Hierarchical Flow的四核A7 Top项目中子模块和顶层属于同步设计吗?如果是,子模块接口的时序如何保证?

是同步设计。子模块接口的时序主要涉及以下几方面工作:

1)通过子模块内部reg–>output的data path优化

2)通过子模块内部input–> reg的data path优化

3)顶层Clock root到子模块内部clock tree需要和顶层寄存器的tree做balance