【数字IC设计】VCS仿真DesignWare IP

DesignWare介绍

DesignWare是SoC/ASIC设计者最钟爱的设计IP库和验证IP库。它包括一个独立于工艺的、经验证的、可综合的虚拟微架构的元件集合,包括逻辑、算术、存储和专用元件系列,超过140个模块。DesignWare和 Design Compiler的结合可以极大地改进综合的结果,并缩短设计周期。Synopsys在DesignWare中还融合了更复杂的商业IP(无需额外付费)目前已有:8051微控制器、PCI、PCI-X、USB2.0、MemoryBIST、AMBA SoC结构仿真、AMBA总线控制器等IP模块。

DesignWare中还包括一个巨大的仿真模型库,其中包括170,000多种器件的代时序的功能级仿真模型,包括FPGAs (Xilinx, Altera,…), uP, DSP, uC, peripherals, memories, common logic, Memory等。还有总线(Bus-Interface)模型PCI-X, USB2.0, AMBA, Infiniband, Ethernet, IEEE1394等,以及CPU的总线功能仿真模型包括ARM, MIPS, PowerPC等。

如上图所示,在安装了DC综合工具后,我们可以在$SYNOPSYS/dw/sim_ver路径下找到Design Ware的仿真库文件。

下面以举两个例子,来说明如何在vcs仿真中使用dw ip库。

ram仿真

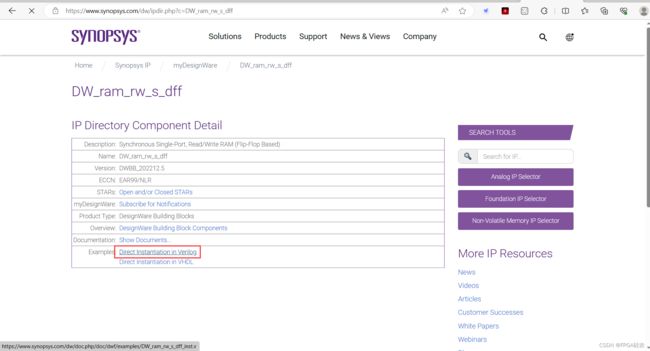

打开网站链接,搜索并找到下图所示的ram ip核。

点击下图所示区域,得到例化该IP核的示例代码:

编写测试代码如下:

module test;

parameter DATA_WIDTH = 8;

parameter DEPTH = 8;

parameter ADDR_WIDTH = $clog2(DEPTH);

parameter RST_MODE = 0;

//signal define

reg clk;

reg rst_n;

reg cs_n;

reg wr_n;

reg wr_busy;

reg start;

reg [2:0] rw_addr;

reg [DATA_WIDTH-1:0] data_in;

wire [DATA_WIDTH-1:0] data_out;

wire done;

//clk generate

initial begin

clk = 1'b0;

forever begin

#5 clk = ~clk;

end

end

//reset and chip enable

initial begin

rst_n = 1'b0;

cs_n = 1'b1;

#100

cs_n = 1'b0;

rst_n = 1'b1;

end

//start generate

initial begin

start = 1'b0;

#123

start = 1'b1;

#10

start = 1'b0;

end

always@(posedge clk or negedge rst_n) begin

if(~rst_n) begin

wr_busy <= 1'b0;

end

else if(start) begin

wr_busy <= 1'b1;

end

else if(wr_busy && rw_addr == DEPTH-1) begin

wr_busy <= 1'b0;

end

end

//wr_n, write enable

always@(posedge clk or negedge rst_n) begin

if(~rst_n) begin

wr_n <= 1'b1;

end

else if(start) begin

wr_n <= 1'b0;

end

else if(wr_busy) begin

if(rw_addr == DEPTH-1) begin

wr_n <= 1'b1;

end

else begin

wr_n <= 1'b0;

end

end

end

//rw_addr

always@(posedge clk or negedge rst_n) begin

if(~rst_n) begin

rw_addr <= 0;

end

else if(start) begin

rw_addr <= 0;

end

else if(wr_busy) begin

rw_addr <= rw_addr + 1'b1;

end

else if(rw_addr!=DEPTH-1) begin

rw_addr <= rw_addr + 1'b1;

end

end

//data_in

always@(posedge clk or negedge rst_n) begin

if(~rst_n) begin

data_in <= 0;

end

else if(wr_busy) begin

data_in <= data_in + 8'd3;

end

end

assign done = (wr_n == 1'b1 && rw_addr == DEPTH-1) ? 1'b1 : 1'b0;

//

initial begin

$fsdbDumpfile("ram.fsdb");

$fsdbDumpvars(0);

end

initial begin

#1000

$finish;

end

//ram inst

DW_ram_rw_s_dff_inst U

(.inst_clk(clk),

.inst_rst_n(rst_n),

.inst_cs_n(cs_n),

.inst_wr_n(wr_n),

.inst_rw_addr(rw_addr),

.inst_data_in(data_in),

.data_out_inst(data_out)

);

endmodule

编写makefile脚本如下:

all: listfile com sim verdi clean

listfile:

find -name "*.v" > filelist.f

com:

vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \

-f filelist.f -l com.log -kdb -lca -y ${SYNOPSYS}/dw/sim_ver +libext+.v

sim:

./simv -l sim.log

verdi:

verdi -f filelist.f -ssf *.fsdb -nologo &

clean:

rm -rf csrc *.log *.key *simv* *.vpd *DVE*

rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f

其中,make com加入了选项:

-y ${SYNOPSYS}/dw/sim_ver +libext+.v

这里,-y lib_dir用于指定搜索模块定义的verilog库目录; 在源代码中找不到相应模块或UDP定义的模块时,在定义的目录中查找对应的文件; +libext与-y配合,用来指定查找的文件的后缀,例如+libext+.v表示查找.v文件。

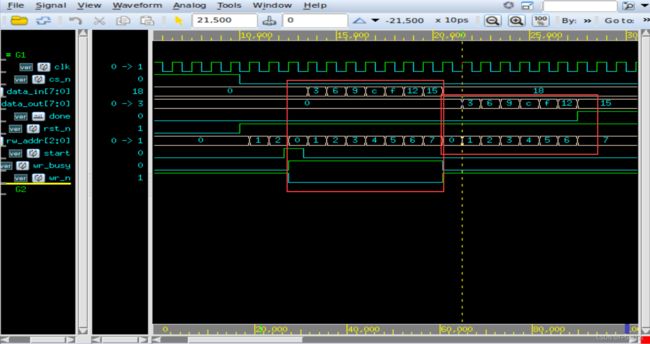

仿真结果如下图所示:

仿真bin2gray

按照仿真ram相同的步骤操作,得到例化该模块的示例代码:

需要注意的是,在例化该模块时,需要加入+incdir+$SYNOPSYS/dw/sim_ver+编译选项,这是因为在使用该IP的时候还需要用到相关的inc文件。

代码:

module test;

parameter DATA_WIDTH = 8;

reg [DATA_WIDTH-1:0] bin;

wire [DATA_WIDTH-1:0] gray;

initial begin

bin = 8'd0;

forever begin

#10 bin = $urandom % 256;

end

end

initial begin

$fsdbDumpfile("top.fsdb");

$fsdbDumpvars(0);

end

initial begin

#1000

$finish;

end

DW_bin2gray_inst U

(

.inst_b(bin ),

.g_inst(gray )

);

endmodule

makefile文件:

all: listfile com sim verdi clean

listfile:

find -name "*.v" > filelist.f

com:

vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \

-f filelist.f -l com.log -kdb -lca -y ${SYNOPSYS}/dw/sim_ver +libext+.v +incdir+${SYNOPSYS}/dw/sim_ver+

sim:

./simv -l sim.log

verdi:

verdi -f filelist.f -ssf *.fsdb -nologo &

clean:

rm -rf csrc *.log *.key *simv* *.vpd *DVE*

rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f

可以看到,在仿真该IP的时候,不仅加入了-y ${SYNOPSYS}/dw/sim_ver +libext+.v编译选项,还加入了+incdir+${SYNOPSYS}/dw/sim_ver+选项。这里,+incdir+dir1+dir2+…用于vcs从指定的目录当中查找源文件中所包含的include文件。

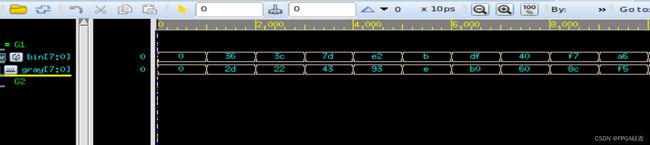

仿真结果如下: