FPGA----UltraScale+系列的PS侧与PL侧通过AXI-HP交互(全网唯一最详)附带AXI4协议校验IP使用方法

1、之前写过一篇关于ZYNQ系列通用的PS侧与PL侧通过AXI-HP通道的文档,下面是链接。

FPGA----ZCU106基于axi-hp通道的pl与ps数据交互(全网唯一最详)_zcu106调试_发光的沙子的博客-CSDN博客大家好,今天给大家带来的内容是,基于AXI4协议的采用AXI-HP通道完成PL侧数据发送至PS侧(PS侧数据发送至PL侧并没有实现,但是保留了PL读取PS测数据的接口)本实验完成了,PL侧自定义数据传输到PS侧,并在PS侧写加软件,完成了PL侧传入数据的求和功能,发挥了整个SoC的功能,为后续PL侧加速计算,PS侧数据分析奠定了基础。_zcu106调试https://blog.csdn.net/qq_37912811/article/details/128097813?spm=1001.2014.3001.5501但当时只是实现了PL侧向PS侧写入数据的功能。而本次给大家带来完整的PS侧与PL侧读写数据完整实验原理以及实现方法。

需要注意的是,本次实验数据接口均采用Xilinx的通用AXI4协议,还有不会的同学赶紧去学习。此外,Xilinx为方便用户调试AXI4协议,还提供了AXI Verification IP本次实验会讲到他的使用方法。

2、实验软硬件:Vivado、zynq UltraScale+系列板卡

3、实验步骤:

①依据上文1中提到的AXI-HP文章,在Block Design中搭建ARM侧的设计,编写相应的数据生成Verilog文件,然后进行仿真。然后在Vivado的SIMULATIN时,可以发现一个现象,就是可以进行正常的写操作,即FPGA可以向ARM写数据。但是在进行读操作时,即FPGA读取ARM侧数据的仿真时,ARM侧应当发送的rvalid信号时钟不能拉高。我一直以为是我代码的问题,我还特意去Xilinx社区问了一下。下面是帖子链接。这也是为什么我去年只做了写操作的教程,没有做读操作的教程。

Xilinx Customer Communityhttps://support.xilinx.com/s/question/0D54U00007BtXHuSAN/the-zcu106-board-uses-axihp-protocol-to-complete-the-communication-between-ps-and-plthe-write-function-is-normal-but-the-read-function-is-abnormal?language=zh_CN

相信大家在做FPGA的时候都会看一些网上的视频教程,比如B站黑金的教程,还会下载对应的程序,但是人家的视频都是针对特定板子开发的,对于我们这种使用Xilinx官方板子的开发者来说,代码啥的都需要再改改。就比如说他的AXI-HP通道读写DDR操作,我看完以后,我甚至以为是Vivado出现BUG了,因为他的Block Design中设置好AXI-HP通道后生成HDL wrapper竟然会有DDR接口,而我用的ZCU106根本不会生成这个DDR接口,只有AXI接口。大家有兴趣的可以自行下载一下,下面是视频链接以及代码链接。

【35】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—PL读写PS端DDR之Vivado创建过程_哔哩哔哩_bilibili1. 课程内容本套视频教程是ALINX公司基于Xilinx Zynq UltraScale+ MPSoC系列FPGA原创的视频教程,内容包含 裸机开发、Linux基础开发、Linux驱动开发、Vitis HLS开发、Vitis AI开发五大部分,详细讲述MPSoc系列FPGA芯片的各个部分开发的相关内容,视频基于ALINX公司自主设计的FPGA开发板进行讲解,理论结合实践,让大家可以充分理解开发的, 视频播放量 2747、弹幕量 3、点赞数 19、投硬币枚数 8、收藏人数 65、转发人数 8, 视频作者 ALINX官方, 作者简介 ,相关视频:【03】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—MPSoC开发之Vitis工程创建流程,【02】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—MPSoC开发之Vivado工程创建流程,【ALINX】FPGA ZYNQ视频教程——AX7010/AX7020教程——FPGA实验篇,【37】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—PS与PL交互之BRAM读写Vivado创建过程,【01】ALINX Zynq MPSoC XILINX FPGA视频教程 Linux基础开发—Petalinux定制Linux系统,【12】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—PS端UART读写例程,【ALINX】FPGA ZYNQ视频教程——AX7010/AX7020教程——SDK实验篇,【01】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—MPSoC架构介绍,【31】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—自定义IP之Vivado创建流程,【63】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—AD9280以太网传输及上位机显示波形实验https://www.bilibili.com/video/BV1UY4y1L7wb/?spm_id_from=333.788

- AX7010资料链接:

- 2017.4版 链接:https://pan.baidu.com/s/1xr3D1EED4zb1eyJHYTGRHg

- 提取码:3z1y

- 软件包链接:

- 2017.4版 链接:https://pan.baidu.com/s/1RiolZAHIi8hCskJJGrmSjg

- 提取码:1w8y

- ZYNQ视频链接:https://pan.baidu.com/s/11_oHUzEOZlBXWLllCdTf6A

- 提取码:3au6

- ubuntu16链接:

- 链接:https://pan.baidu.com/s/19TurvpRlmWdEb8Yo_QatIg?pwd=tpcx

- 提取码:tpcx

最后我得出的结论是,zynq UltraScale+系列板卡(ZCU系列),在Vivado中进行仿真时,rvalid信号确实不会自动拉高,只有在上板子之后他才会被拉高。那么问题来了,每次生成bit文件时间那么长,总不能每次都浪费吧?为了解决这个问题,我们可以使用Xilinx提供的AXI协议调试IPAXI Verification IP。由于调试的AXI-HP接口,因此,下面以FPGA为主机,ARM为从机进行测试(ARM为从机,即设置AXI Verification IP为从机即可)。

②在block design中搜索axi vip然后添加

③配置axi vip模块

上面的设置依据大家的具体情况设定即可,要想调试出的AXI接口直接可以上板使用,最好的方法是:先在block design中配置好ARM,然后生成HDL wrapper,查看HDL wrapper中的verilog文件的ARM的每个端口配置,然后依据这个设置axi vip配置即可。

配置好axi vip后,将下面这三根线引出,然后配追地址,需要注意的是,axi vip只有2M,因此不能大量读写数据。写的时候要看清楚地址,下面这个偏移起始地址是44A0_0000,但是我写的代码是从0000_0000开始的,仍然可以正常使用,具体原因不清楚。

④编写自己的数据生成代码已经AXI接口代码,可以去我上面提供的链接里面下载,也可以查看我之前的文章,自行编写。

⑤配置axi vip仿真文件。虽然上面添加了axi vip模块,但这并不代表可以直接进行仿真了,还需要添加一些仿真文件。

- 添加自定义的testbench.sv文件(sv文件哈,system verilog文件)

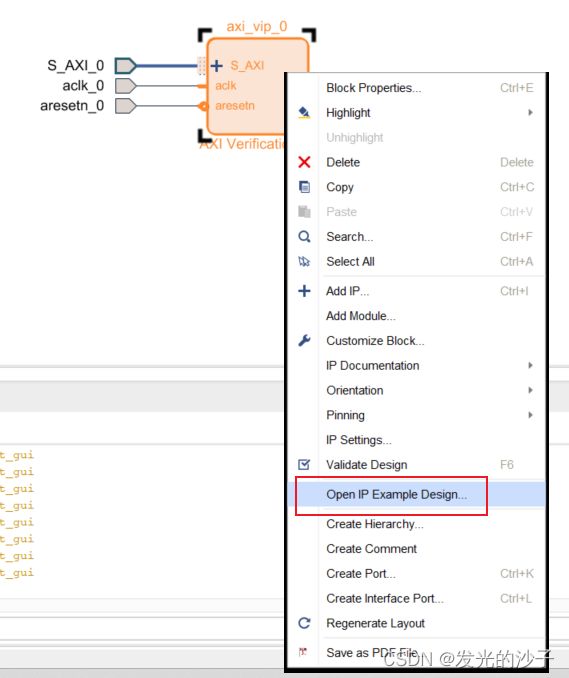

- 打开axi vip的设计例程

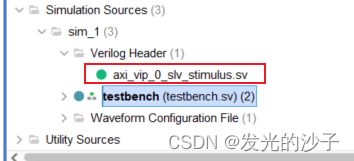

- 打开例子工程文件夹:x:\xxxx\xx\axi_vip_0_ex\imports,将这些文件夹复制到与testbench.sv同一个目录下,如:D:\vavado_project\AXI_VIP_SLAVE\AXI_VIP_SLAVE.srcs\sim_1\new

- 更改testbench.sv文件

- 回到vivado界面,打开TCL Console面板,输入:get_ips *vip*命令,然后复制出现IP名称,我这里是design_1_axi_vip_0_0。

- 修改下面红框部分,这是system Verilog语法,目的是找到axi vip这个模块

- 这样就配置好了,直接在Vivado中进行simulink即可。

- 需要注意的是,如果配置axi vip为主机,那么需要修改axi_vip_0_mst_stimulus.sv文件,将下面这段代码注释掉即可,不然会报错。

以上内容参考了知乎大神帖子,下面是传送门

【VIVADO IP】AXI Verification IP - 知乎0 前言本文记录关于VIVADO IP核【AXI Verification IP】的部分使用和配置方式,主要参考IP手册【PG267】和【 芯选】关于IP的介绍。IP内功能较为丰富,这里仅对使用到的部分进行记录,如果有错误的地方还请提醒。AX…![]() https://zhuanlan.zhihu.com/p/526968284

https://zhuanlan.zhihu.com/p/526968284

⑥直接进行上板调试即可,这里给大家一个PS与PL交互的思路:

4、我们完成了基于SoC(ARM+FPGA架构)的电力系统电磁仿真SDK,需要合作可以联系作者邮箱!