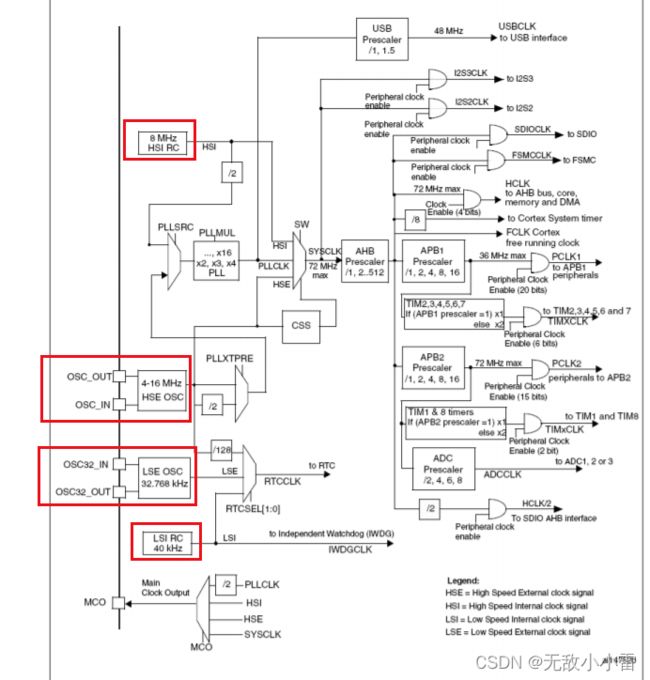

stm32f103——时钟树的分析与配置

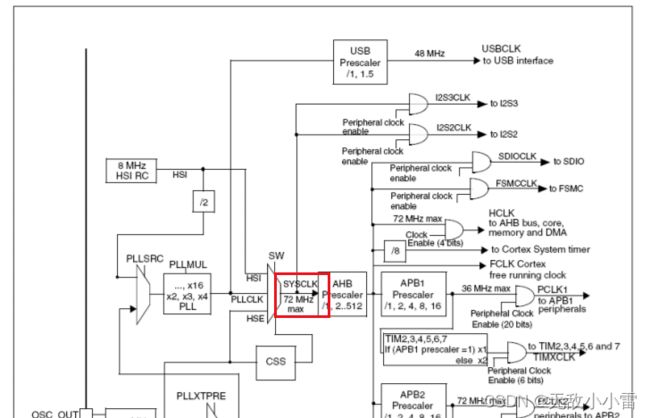

时钟树是用来对单片机系统和各个外设进行时钟配置的,因为不同的外设,其电路不同,对时钟频率的要求也就不同。所以需要我们对时钟源的频率进行改变,变成外设需要的时钟频率。

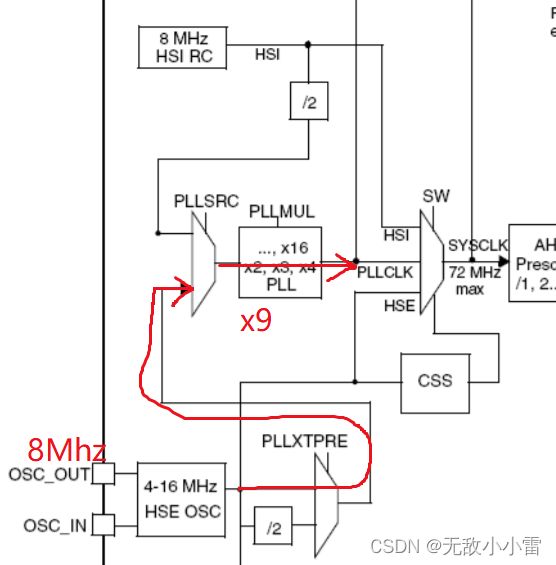

![]()

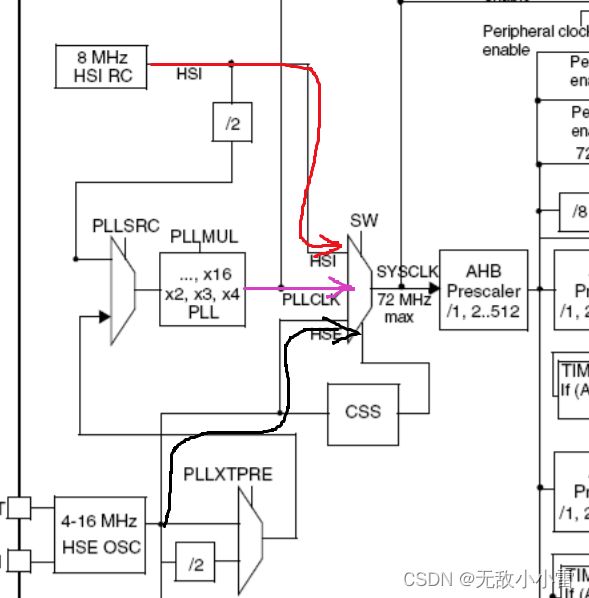

![]()

首先时钟树分为俩部分:

左边部分是时钟的来源,右边部分是时钟的去向:

各类时钟简括:

1.HSE时钟(高速外部时钟):来源为外部晶振,通常速度8Mhz。由RCC_CR时钟控制寄存器中的16:HSEON控制。

2.HSI时钟(高速内部时钟):来源为芯片内部,大小为8Mhz,当HSE故障时,系统时钟会自动切换到HSI,知道HSE启动成功,相当于HSE的替补。由RCC_CR时钟控制寄存器的位0:HSION控制。

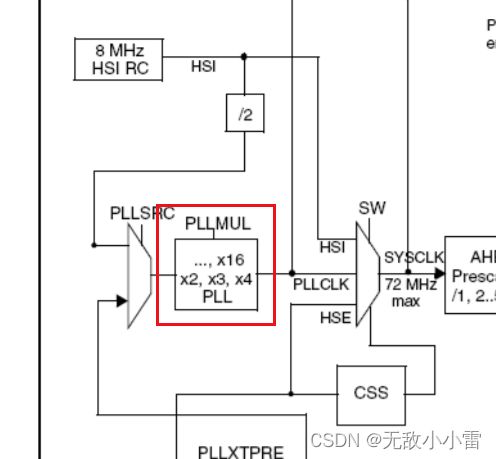

3.PLLCLK(锁相环时钟):来源为HSI/2或HSE,经过倍频所得。由CFGR(时钟配置寄存器)中PLLXTPRE、PLLMUL控制。

4.SYSCLK(系统时钟):来源为HSI或HSE或PLLCLK,最高速度为72M。由CFGR中的SW控制。

5.HCLK(AHB高速总线时钟):来源由系统时钟分频得到,速度最高为72M。由CFGR中的HPRE控制。

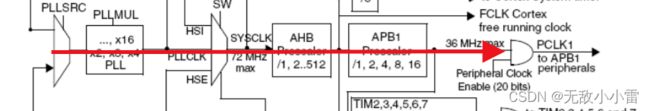

6.PCLK1(APB1低总线时钟):来源为HCLK分频得到,速度最高为36M ,为APB1总线上的外设提供时钟。由RCC_CFGR时钟配置寄存器的PPRE1位控制。

7.PCLK2(APB2高总线时钟):来源为HCLK分频得到,速度最高为72M,为APB2总线上的外设提供时钟。由RCC_CFGR时钟配置寄存器的PPRE2位控制。

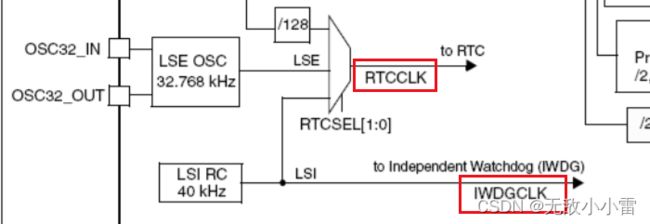

8.RTC时钟:来源为HSE_RTC(HSE分频得到)、LSE、LSI,为芯片内部的RTC外设提供时钟。由RCC备份域控制寄存器RCC_BDCR中RTCSEL控制。

9.MCO时钟输出 :来源为PLLCLK/2、HSE、HSI、SYSCLK,微控制器时钟输出引脚,由PA8复用所得。由CRGR中MCO控制。

我来看时钟树中几个重要部件:

4个时钟源:

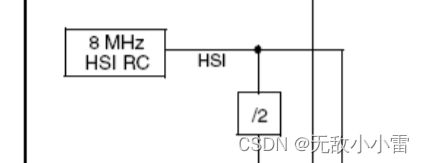

1.内部高速时钟HSI:

单片机内部自带有时钟源,其频率位8Mhz。但是,与外部时钟源不同的是,它是一个RC振荡器,它的精度和稳定性(受温度影响大)要低于外部晶振,所以它适用于在对时钟频率精度要求不高或者产品体积很小的场合使用。

当HSE故障时,系统时钟会自动切换到HSI。

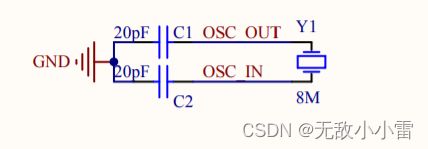

2.外部高速时钟HSE:

将外部晶振振荡电路(皮尔斯电路)作为时钟源,通常速度8Mhz ~ 12Mhz。由RCC_CR时钟控制寄存器中的16:HSEON控制。

由于其振荡频率高、精度高、稳定性较好,所以大部分场合使用的都是外部高速时钟。

3.外部低速时钟LSE:

外部低速时钟LSE,时钟源也是由外部晶振振荡电路提供。和外部高速时钟一样,只不过它的频率比外部高速时钟低很多。

4.内部低速时钟LSI:

内部低速时钟,只有40Khz。它是看门狗的时钟源。

5.系统时钟和非系统时钟:

系统时钟就是红框处的SYSCLK,由图可知,其最大频率只能是72Mhz,而且它的时钟来源可以是上述4个时钟源中任何一个,至于选择哪一个作为时钟源,就看我们自己的应用,不过我们一般将系统时钟的频率都配置为72Mhz来使用。

什么是系统时钟?它的作用是什么?

实际上,系统时钟就是机器周期(注意:是系统时钟的频率而不是外部晶振的频率),系统时钟为72Mhz ,那么 T = 1/f = 13ns(由1/1M=1us计算可知)。假设执行一条指令需要花费一个机器周期,那么执行一条指令就需要花费13ns的时间。

系统时钟的另外的作用就是配置各个外设的时钟。由图可知,外设的时钟都是来源于系统时钟。但是,有两个外设的时钟不是来源于系统时钟SYSCLK。即:看门狗和RTC(实时时钟),它俩的时钟来源是来自LSE和LSI。

为什么要单独提供一个外部时钟给RTC?因为,有些场合需要关机后还能计时,那就需要这个RTC来计时。

其他重要部件:

1.PLL(锁相环时钟):

倍频器。其作用就是将输入的时钟频率乘以倍频系数进行倍频。由CFGR(时钟配置寄存器)中PLLMUL控制。

来源路径:(三条路径)

HSI (8Mhz)------> HSI/2 (分频器) (4Mhz)------> PLLSRC(二选一选择器) ------> PLL

HSE ------> PLLXTPRE(二选一选择器) ------> PLLSRC(二选一选择器) ------> PLL

HSE(8Mhz) ------> HSE/2 (分频器)(4Mhz) ------> PLLXTPRE(二选一选择器) ------> PLLSRC(二选一选择器) ------> PLL

所以,PLL的输入来源,来自HSI或者HSE。

一般我们配置系统时钟为72Mhz,所以选择:8 * 9 = 72Mhz。注意:由上图知,系统时钟最大为72Mhz。

CSS为时钟安全检测标志,因为系统时钟最大为72Mhz,如果我们配置的频率超过72Mhz,那么CSS就会置位,提醒我们时钟已经不安全了。

2.三选一选择器、AHB总线、APB总线:

图中SW是三选一选择器,在HSI、PLLCLK、HSE三个中选择其中一个作为系统时钟SYSCLK的频率。

AHB Prescaler 是AHB预分频器,即:将输入的频率除以分配系数进行分频。预分频器和分频器不同,分频器的分频系数是固定的,而预分频器的分频系数可以设置。其输出的频率是提供给AHB总线使用的。

APB1 Prescaler 是APB1 预分频器。其输出的频率是提供给APB1总线使用的。

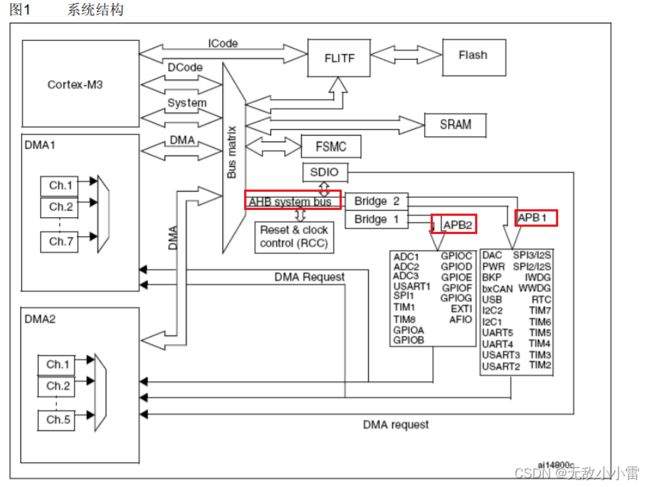

上图是单片机内部的总线架构。

AHB总线是高级高性能总线,其主要用于高性能模块之间的连接。(还有的单片机内部AHB还分为AHB1和AHB2,它俩各自连接不同的外设。)总体而言AHB的速度比APB的速度要高。

APB主要用于低带宽的周边外设之间的连接,由图中,我们可以看到APB分为APB1和APB2,它们分别连接着不同的外设。但是,注意:APB1总线的最大速度为36Mhz,而APB2总线的最大速度为72Mhz,所以,APB2总线实际上是高速总线,而APB1总线为低速总线。

不同的总线把不同的外设区分开来,可以实现对CPU的最高利用,比如CPU和RAM之间的交互,就需要高速访问。而CPU于定时器等低速设备就不需要那么快的速度,而且速度越快,功耗就越高,所以需要对速度进行区分开来,为了节省功耗。

3.USB预分频器:

USB Prescaler是USB预分频器,其将PLLCLK的时钟来源进行分频,注意:图中显示,USB最大传输时钟为48Mhz,如果配置时钟失败,则USB传输数据就会错误。

4.定时器:

定时器的倍频器有一些不同,它的倍频有条件。条件如下:

if(APB1 Prescaler = 1)

x1

else

x2

如果APB1预分频器的分频系数为1,那么定时器倍频器的倍频系数就为1。如果APB1预分频器的分频系数不为1,那么定时器倍频器的倍频系数就为2。

所以,假设AHB的频率为72Mhz,那么定时器的最大频率为72Mhz。因为,APB1最大频率为36Mhz,所以,APB1的分频系数

为2 而不为1。所以定时器的倍频系数就是x2,所以36 * 2 = 72Mhz。

面试题:定时器2、3、4、5、6、7的频率最大是多少hz? 答案是:72Mhz

4.ADC:

ADC模数转换,其频率最大为14Mhz,所以假设APB2的频率为72Mhz,那么72 / 6 = 12Mhz < 14Mhz

时钟树的配置

步骤:

RCC配置到72MHZ,编程步骤:

1,打开HSE

2,等待外部高速时钟稳定且就绪

3,设置PLL时钟源和倍频系数

4,使能PLL

5,等待PLL准备就绪

6,设置AHB预分频器

7,设置APB1预分频器

8,设置APB2预分频器

9,设置系统时钟

10,查看系统时钟是否设置正确

代码:

void RCC_ConfigTo72M(void)

{

// 1,打开HSE

RCC_HSEConfig(RCC_HSE_ON);

// 2,等待外部高速时钟稳定且就绪

while(SUCCESS!=RCC_WaitForHSEStartUp());

// 3,设置PLL时钟源和倍频系数

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

// 4,使能PLL

RCC_PLLCmd(ENABLE);

// 5,等待PLL准备就绪

while(SET!=RCC_GetFlagStatus(RCC_FLAG_PLLRDY));

// 6,设置AHB预分频器

RCC_HCLKConfig( RCC_SYSCLK_Div1);

// 7,设置APB1预分频器

RCC_PCLK1Config(RCC_HCLK_Div2);

// 8,设置APB2预分频器

RCC_PCLK2Config(RCC_HCLK_Div1);

// 9,设置系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

// 10,查看系统时钟是否设置正确

while(0x08!=RCC_GetSYSCLKSource());

}

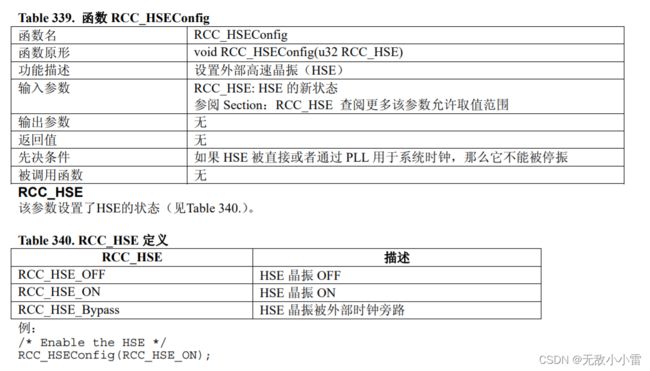

1.打开HSE

2,等待外部高速时钟稳定且就绪

我们需要等待外部时钟起振稳定后再开始进行时钟配置,否则配置出来的时钟频率有问题

3,设置PLL时钟源和倍频系数

4,使能PLL

5,等待PLL准备就绪

6,设置AHB预分频器

注意,这里有两点:

1.AHB预分频器是一个功能而不是一个物理器件,所以它不需要等带就绪。而PLL则是一个物理器件,相对于AHB来说,它有较大的延时,所以需要等待它准备好。

2.1分频(分频系数为1)就是不分频,千万不要写成0分频。

3.为什么这里是先设置预分频,而不是按照从左到右的顺序,先设置系统设置再来设置预分频器?

原因是,如果先设置好系统时钟,那么最后开启预分频器的那一瞬间,频率可能会出现短暂的错误。所以,我们先设置好各个外设的预分频器,让预分频器准备好了,最后再来设置并打开系统时钟,将频率输入给预分频器。而且有一些外设和功能的时钟来源是直接来自系统时钟。如果先开起系统时钟,那么这部分外设很可能会先工作,而预分频后面的外设需要再开启预分频后,才能工作,这样的话,可能会导致系统工作不正常。

7.设置APB1预分频器

我们需要用到APB1下的外设,所以需要设置APB1总线的时钟

8.设置APB2预分频器

9.设置系统时钟

设置完预分频后,最后再来设置和开启系统时钟。

10.查看系统时钟是否设置正确

防止系统时钟设置错误。