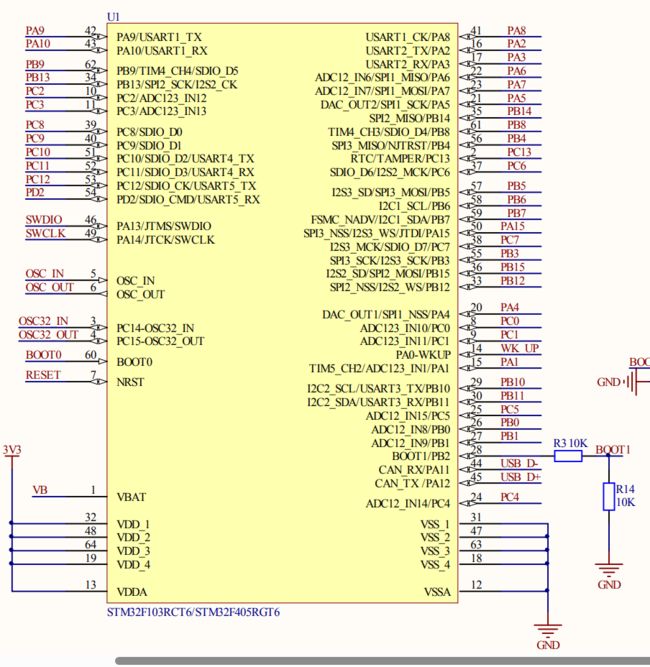

对stm32F103RCT6原理图解析(详细)

最近想了解一下原理图为什么这样设计,又发现网上虽然有相关的解析,但是不全面,所以唉还是自己动手,丰衣足食吧。

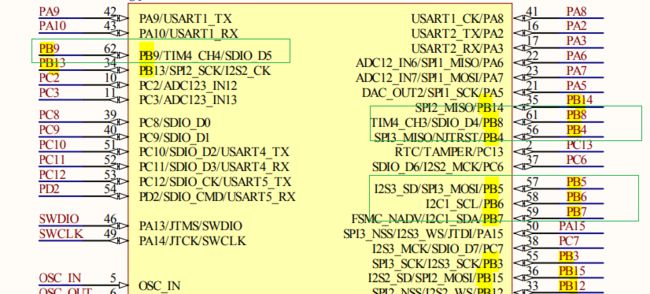

MCU部分

核心芯片STM32F103RCT6

(8条消息) stm32命名规则_BachelorTse的博客-CSDN博客

这里有芯片相关的命名规则

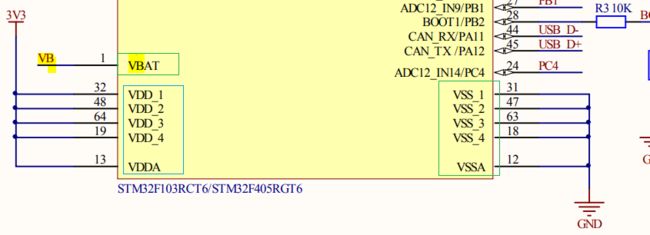

左下角供电部分:

VDD:D=device 表示器件的意思, 即器件内部的工作电压;

VSS:S=series 表示公共连接的意思,通常指电路公共接地端电压

VEE:负电压供电;场效应管的源极(S)

VBAT:当使用电池或其他电源连接到VBAT脚上时,当VDD 断电时,可以保存备份寄存器的内容和维持RTC的功能。如果应用中没有使用外部电池,VBAT引脚应接到VDD引脚上。

参考:(8条消息) 电源符号:VCC、VDD、VEE、VSS、VBAT_vdd在电路中代表什么_桂花很香,旭很美的博客-CSDN博客

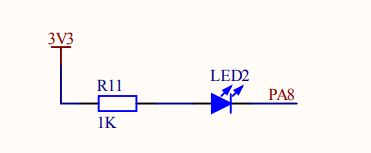

一、LED模块

所以如果我们想要让LED灯亮起,首先要经过连接在LED上的二极管,所以我们要让该二极管工作,从输入源里输入一个低电平,即可让二极管的负极一端引脚工作,相反输入高电平则二极管的负极一端不会产生任何作用!

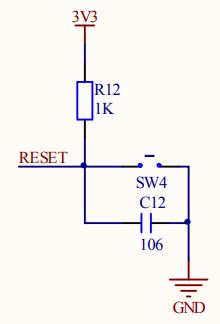

二、复位引脚NRST原理图

| 外围电路 | 引脚连接处 |

|

STM32F的NRST是异步复位脚。 复位就是让单片机重启,使其恢复到一个缺省的状态。当NRST输入低电平的时候,MCU处于复位状态,重设所有的内部寄存器,及片内几十KB的SRAM。 当NRST从低电平变高时,PC指针从0开始。 但是复位的时候不会将STM32F片内RTC的寄存器以及后备存储器重置,因为它们是用电池通过专门的VBAT脚供电。 STM32中的NRST有施密特功能。大概在输入电压低于1.V的时候将芯片复位。

上电的瞬间,电容C12两端电压可以认为是0,刚上电的时候电流会通过R12和C12到地,为C20充电,RESET会输出低电平,stm32处于复位状态,VCC3.3通过电阻R3给电容充电,当电容C12的电压升高到0.8V以上,stm32退出复位状态进入运行状态。

可以参考这里: STM32 复位电路设计

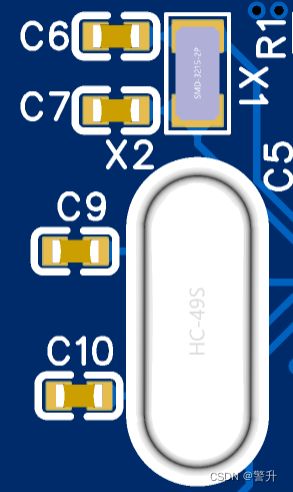

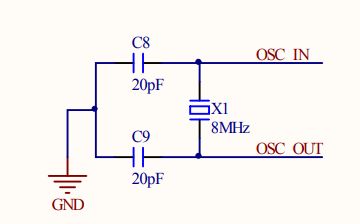

三、晶振引脚原理图

|

|

|

|

8Mhz晶振

高速晶振 8MHz 作为系统时钟的来源,可以由芯片内部的 HSI RC 时钟源或芯片外部的 独立时钟源 提供。

在STM32最小系统板上,8M晶振是用于提供系统时钟的外部晶体振荡电路之一。

高速晶振 8MHz 作为系统时钟的来源,可以由芯片内部的 HSI RC 时钟源或芯片外部的 独立时钟源 提供。由于芯片内部的 HSI RC 时钟源不够精准,我们通常采用外部独立时钟源来来为芯片提供系统时钟。

具体计算方法如下:

晶振频率 = 8MHz

晶振周期 = 1 / 晶振频率 = 0.125us

如果需要一个1秒的周期,需要多少个晶振周期?

1s / 0.125us = 8000000个周期

因此,如果使用8MHz晶振,系统需要运行8000000个晶振周期才能完成一个1秒的周期。

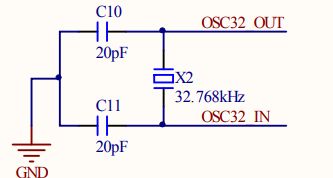

32.768K晶振

低速晶振 32.768kHz 连接LSE(low-speed external clock signal),最终到达RTC(real-time clock)。

RTC 是一个独立的定时器 1 。从 real-time clock(实时时钟)四字可以理解,RTC可以为系统实时记录当前系统时间和日期,不管芯片有没有掉电。如果想要使用 RTC 实时记录系统时间,芯片需要接入额外备用电源,通常为纽扣电池。这样以来,RTC 在芯片掉电后,可以由电池供电继续运行 2 。

对于掉电后不需要记录系统时间的电路板,我们将低速晶振 32.768kHz 舍去,节约板子空间,精简电路设计。

2的15次方正好等于32768,反过来讲,如果要把32.768K的时钟频率经过15次分频的话,得到的频率正好是1Hz。

晶振旁的俩个电容到底有啥作用

主要作用是平衡晶振引脚的电感的。因为晶振在高频工作时有寄生电感,为了平衡电感,起到谐振的作用。所以要用两个小电容来平衡电感。一般电容的选20pf–30pf的就可以了。具体的大小请参看晶振厂家提供的数据手册。

芯片晶振引脚的内部通常是一个反相器,芯片晶振的两个引脚之间还需要连接一个电阻,使反相器在振荡初始时处与线性状态,但这个电阻一般集成在芯片的内部,反相器就好像一个有很大增益的放大器,为了方便起振,晶振连接在芯片晶振引脚的输入和输出之间,等效为一个并联谐振回路, 振荡的频率就是石英晶振的并联谐振频率。

晶振旁边的两个电容需要接地,,其实就是电容三点式电路的分压电容,接地点就是分压点,以分压点为参考点,振荡引脚的输入和输出是反相的,但从晶振两端来看,形成一个正反馈来保证电路能够持续振荡。

芯片设计的时候,其实这两个电容就已经形成了,一般是两个的容量相等,但容量比较小,不一定适合很宽的振荡频率范围,所以需要外接两个负载电容。

晶振旁边的负载电容怎么选择?

负载电容需要根据晶振的规格来选择,晶振的规格书都会标示出负载电容的大小,一般都是几pF到几十pF。

假如晶振规格要求用20pF的负载电容,因为两个负载电容是串联的,理论上需要选择两个40pF的负载电容。

实际上MCU内部和PCB的线路上都会有一定的寄生电容,晶振的负载电容=[(C1*C2)/(C1+C2)]+Cic+△C,Cic+△C 为MCU内部电容和PCB线路的寄生电容,一般是35pF,所以,在实际应用中会考虑用30pF36pF的负载电容。

晶振和负载电容布线注意事项

为了让晶振能够可靠、稳定的起振,我们在布线时,需要让晶振和负载电容尽量的靠近芯片的晶振引脚。

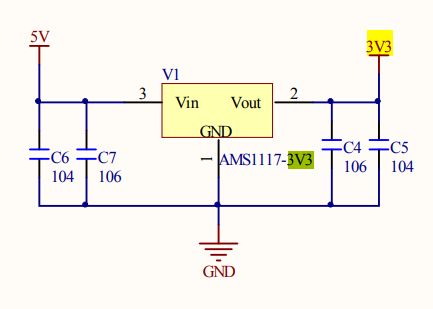

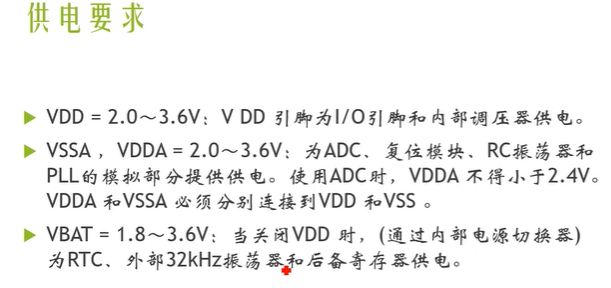

四、电源转换电路

我们可以发现电源转换电路是由一个稳压芯片AMS1117-3.3V、两个电解电容和两个贴片电容组成。

设计原因:STM32芯片的工作电压为2.0~3.6V,我们一般取3.3V。而通过USB接口输出的电源为5V,为防止STM32芯片损坏,需要我们通过该电源转换电路,把5V的输入电压降低到3.3V工作电压。

电容作用:C12和C15是输出滤波电容,作用是抑制自激振荡,如果不接这两个电容,通常线性稳压器的输出会是个振荡波形。C13和C14是输入电容,对于交流电压整流输入,它们的第一个作用是把单向脉动电压转换成直流电压,在本图中输入已经是+5V直流电源了,它们的作用就是防止断电后出现电压倒置,因此通常输入电容的容量应该大于输出电容。

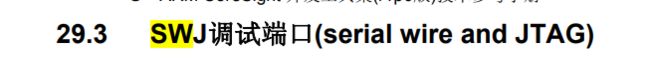

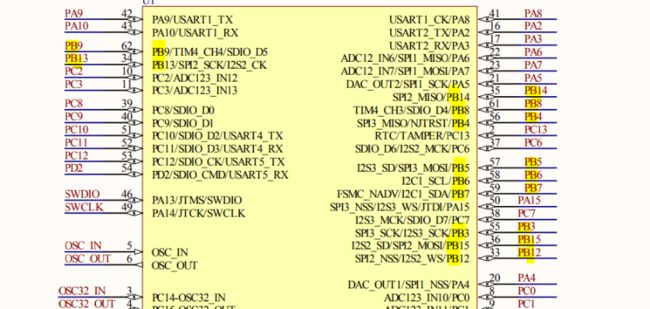

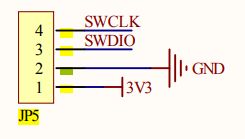

五、SW接口

| 外围电路 | 与芯片连接 |

|

|

探索者F4%20资料盘(A盘)/【正点原子】STM32F103最小系统板资料/8,STM32参考资料/8,STM32参考资料/STM32中文参考手册_V10.pdf

有对这个接口详细的描述

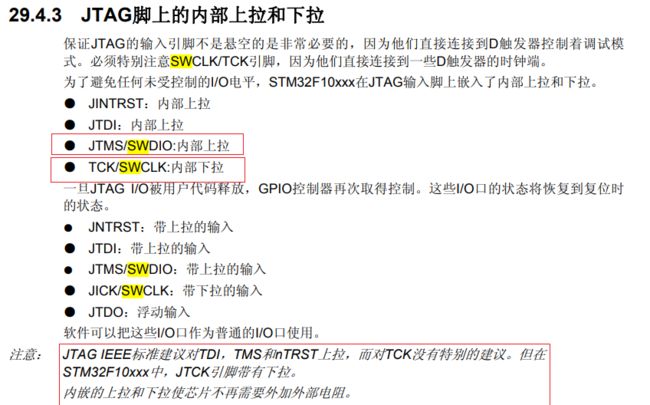

SWDIO,在芯片内部已经有上拉,但在电路板上必须再一次上拉(100k或者10k电阻)

SWCLK,在芯片内部已经有下拉,在电路板上没有特殊要求进一步下拉。

参考:(8条消息) STM32F407-学习STM32的SW与JTAG调试与下载电路的设计_stm32jtag接口电路图_Wallace Zhang的博客-CSDN博客

(8条消息) stm32使用SWD烧录_stm32swd烧录_梦屿_千寻的博客-CSDN博客

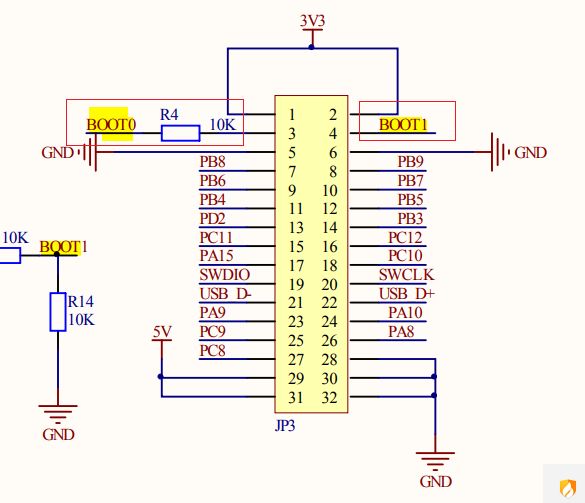

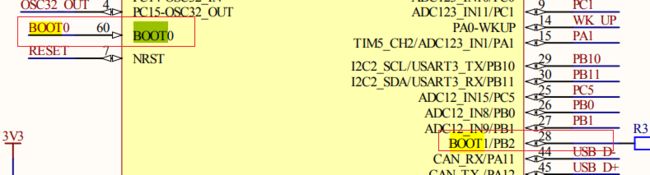

六、BOOT0和BOOT1

| 外围电路 | 与芯片相接引脚 |

|

|

BOOT决定的模式

(8条消息) STM32---BOOT0和BOOT1_stm32boot0和boot1接线图_bit er的博客-CSDN博客

这里原理比较复杂,如果想深入了解的话上面的链接有比较详细的介绍

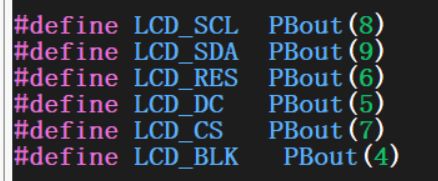

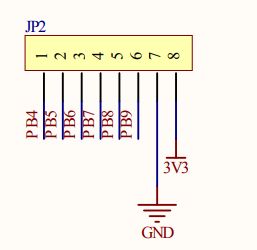

七、LCD外围电路

| 外围电路 | 与芯片引脚 |

|

|

最小系统板原理图如下图,LCD与STM32接线如下。

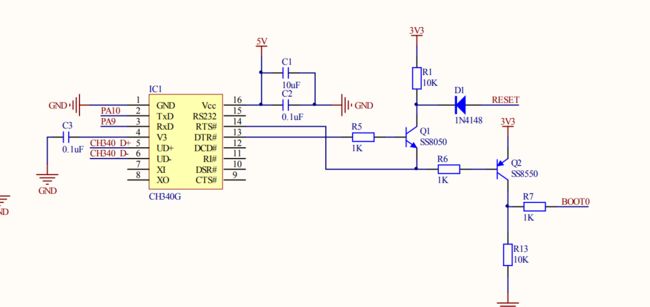

八、串口一键下载电路(CH340)

直接看这里就好,这个博主说的很清楚透彻了

以后有时间再回来补全细节。