中科亿海微浮点数转换定点数

引言

浮点数转换定点数是一种常见的数值转换技术,用于将浮点数表示转换为定点数表示。浮点数表示采用指数和尾数的形式,可以表示较大范围的数值,但存在精度有限的问题。而定点数表示则采用固定小数点位置的形式,具有固定的精度和范围。在某些应用中,特别是在嵌入式系统和数字信号处理领域,使用定点数表示可以更加高效地进行计算。然而,很多算法和库函数都是基于浮点数实现的,因此需要将浮点数转换为定点数才能在这些系统中使用。浮点数转换定点数的背景涉及到浮点数和定点数的表示方法、精度要求以及性能考虑等方面。在转换过程中需要考虑相应的位宽、小数点位置、舍入方式等参数的选择,以保证转换后的定点数能够准确地表示原始浮点数,并满足应用的要求。此外,浮点数转换定点数也可能涉及到溢出、舍入误差、舍入方式选择等问题。因此,在实际应用中需要仔细分析和评估转换算法的性能和精度,并根据具体的应用场景进行调整和优化。

背景

浮点数转换定点数的概念和技术并没有一个具体的发明者或起源人。它是在计算机科学和数字信号处理等领域的发展过程中逐渐形成和应用的。浮点数和定点数的概念最早可以追溯到计算机科学的早期发展阶段。在计算机领域的先驱们,如冯·诺依曼、约翰·冯·诺伊曼、阿兰·图灵等,对于数字表示和计算方法进行了深入研究,为后来的浮点数和定点数概念的发展奠定了基础。随着计算机技术的快速发展,浮点数和定点数的表示方法和转换技术也得到了更多的研究和应用。在数字信号处理领域,特别是在嵌入式系统和通信领域,浮点数转换定点数被广泛应用于各种算法和信号处理任务。因此,浮点数转换定点数作为一种技术和方法,并没有一个特定的发明者或起源人,而是在计算机科学和数字信号处理领域的长期积累和发展中形成的。不同的研究者和工程师在不同的应用场景中对该技术进行了不同的改进和优化,推动了该技术的应用和发展。

软核开发

module top (

input wire clk,

input wire rst_n,

input The_uart_en_w,

input [31:0] The_uart_data

);

wire [31:0] B;

wire [31:0] C;

wire valid;

wire complete;

wire [23:0] intpart; //结果整数部分

wire [23:0] decpart; //结果小数部分

assign B = 32'd0;

decimals u_decimals(

.clk (clk ),

.rst_n (rst_n ),

.valid (valid ), //转换开始使能

.symbol (C[31] ), //符号位

.exponent (C[30:23] ), //阶码

.trail (C[22:0] ), //尾数

.intpart (intpart ), //结果整数部分

.decpart (decpart ), //结果小数部分

.complete (complete ) //执行完成信号

);

floatingpoint32 u_floatingpoint32(

.clk (clk ),

.rst_n (rst_n ),

.en (The_uart_en_w ),//数据转换开始

.A (The_uart_data ),

.B (B ),

.C (C ),

.valid (valid )

);

endmodule module decimals (

input wire clk,

input wire rst_n,

input valid,

input symbol, //符号位

input [7:0] exponent, //阶码

input [22:0] trail, //尾数

output reg [23:0] intpart, //结果整数部分

output reg [23:0] decpart, //结果小数部分

output reg complete //执行完成信号

);

//------------------------------------------------------------------------------

//----------- Registers decpartlarations -------------------------------------------

//------------------------------------------------------------------------------

reg [3:0] state = 0;

reg [5:0] ctate = 0;

reg [2:0] mimi = 0;

reg [2:0] ter = 0;

reg [2:0] trai_ter = 0;

reg [7:0] exponent_reg_d0 = 0; //寄存1

reg [22:0] trail_reg_d0 = 0; //寄存1

reg [23:0] trail_reg_d1 = 0; //寄存2

reg [23:0] trail_reg_d2 = 0; //寄存2

reg [23:0] trail_reg_d3 = 0; //寄存3

reg [23:0] trail_reg_d4 = 0; //寄存4

reg trai1_one = 0; //单位寄存

reg trai2_one = 0; //单位寄存

reg trai3_one = 0; //单位寄存

reg trai4_one = 0; //单位寄存

reg trai5_one = 0; //单位寄存

reg trai6_one = 0; //单位寄存

reg trai7_one = 0; //单位寄存

reg trai8_one = 0; //单位寄存

reg trai9_one = 0; //单位寄存

reg trail0_one = 0; //单位寄存

reg trail1_one = 0;

reg trail2_one = 0;

reg trail3_one = 0;

reg trail4_one = 0;

reg trail5_one = 0;

reg trail6_one = 0;

reg trail7_one = 0;

reg trail8_one = 0;

reg trail9_one = 0;

reg trai20_one = 0;

reg trai21_one = 0;

reg trai22_one = 0;

reg trai23_one = 0;

reg trai24_one = 0;

reg chic = 0;

reg start = 0; //启动判断

reg etart = 0; //启动判断

reg judge = 0; //判断m有多少零

reg [5:0] cnt = 0;

reg [5:0] sum = 0;

reg [5:0] com = 0;

reg [5:0] count = 0;

reg [20:0] bucket = 0;

reg [5:0] select = 0;

reg [20:0] cno = 0;

reg [4:0] ltate = 0;

reg a0,a1,a2,a3,a4,a5,a6,a7,a8,a9;

reg a10,a11,a12,a13,a14,a15,a16,a17;

reg a18,a19 = 0;

reg ltate_done;

reg [35:0] cno_ride = 0;

reg [23:0] cno_ride_reg = 0;

reg s0,s1 = 0;

reg g0,g1 = 0;

//------------------------------------------------------------------------------

//----------- Wires decpartlarations -----------------------------------------------

//------------------------------------------------------------------------------

wire pos_valid;

wire pos_chic;

//------------------------------------------------------------------------------

//----------- Local Parameters -------------------------------------------------

//------------------------------------------------------------------------------

parameter idle = 'd0; //初始化状态

parameter expo = 'd1; //阶码计算

parameter trai = 'd2; //尾码计算

parameter trai_1 = 'd3; //尾码计算1

parameter trai_2 = 'd4; //尾码计算2

parameter trai_3 = 'd5; //尾码计算3

parameter decparti = 'd6; //数据结合

parameter resu = 'd7; //结果

parameter stop = 'd8; //结束

//------------------------------------------------------------------------------

//----------- Assign/Always Blocks ---------------------------------------------

//------------------------------------------------------------------------------

assign pos_valid = s0 & (!s1);

assign pos_chic = g0 & (!g1);

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

s0 <= 'd0;

s1 <= 'd0;

end

else

begin

s0 <= valid;

s1 <= s0;

end

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

g0 <= 'd0;

g1 <= 'd0;

end

else

begin

g0 <= chic;

g1 <= g0;

end

end

// 判断多少 0

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

judge <= 1'b0;

mimi <= 3'd0;

ter <= 3'd0;

cnt <= 6'd0;

end

else

case (mimi)

0:begin

if (start)

mimi <= 3'd1;

else

mimi <= mimi;

end

1:begin

if (ter == 5)

begin

ter <= 3'd0;

mimi <= 3'd2;

end

else

begin

ter <= ter + 1'b1;

cnt <= ctate;

end

end

2:begin

if (ter == 5)

begin

ter <= 3'd0;

mimi <= 3'd0;

judge <= 1'b0;

end

else

begin

judge <= 1'b1;

ter <= ter + 1'b1;

end

end

default : ;

endcase

end

always @ (*) begin

if (trail[0] == 1) ctate = 0;

else if (trail[1] == 1) ctate = 1;

else if (trail[2] == 1) ctate = 2;

else if (trail[3] == 1) ctate = 3;

else if (trail[4] == 1) ctate = 4;

else if (trail[5] == 1) ctate = 5;

else if (trail[6] == 1) ctate = 6;

else if (trail[7] == 1) ctate = 7;

else if (trail[8] == 1) ctate = 8;

else if (trail[9] == 1) ctate = 9;

else if (trail[10]== 1) ctate = 10;

else if (trail[11]== 1) ctate = 11;

else if (trail[12]== 1) ctate = 12;

else if (trail[13]== 1) ctate = 13;

else if (trail[14]== 1) ctate = 14;

else if (trail[15]== 1) ctate = 15;

else if (trail[16]== 1) ctate = 16;

else if (trail[17]== 1) ctate = 17;

else if (trail[18]== 1) ctate = 18;

else if (trail[19]== 1) ctate = 19;

else if (trail[20]== 1) ctate = 20;

else if (trail[21]== 1) ctate = 21;

else if (trail[22]== 1) ctate = 22;

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

intpart <= 'd0;

decpart <= 'd0;

exponent_reg_d0 <= 'd0;

trail_reg_d0 <= 'd0;

start <= 'd0;

sum <= 'd0;

trai1_one <= 'd0; //单位寄存

trai2_one <= 'd0; //单位寄存

trai3_one <= 'd0; //单位寄存

trai4_one <= 'd0; //单位寄存

trai5_one <= 'd0; //单位寄存

trai6_one <= 'd0; //单位寄存

trai7_one <= 'd0; //单位寄存

trai8_one <= 'd0; //单位寄存

trai9_one <= 'd0; //单位寄存

trail0_one <= 'd0; //单位寄存

trail1_one <= 'd0;

trail2_one <= 'd0;

trail3_one <= 'd0;

trail4_one <= 'd0;

trail5_one <= 'd0;

trail6_one <= 'd0;

trail7_one <= 'd0;

trail8_one <= 'd0;

trail9_one <= 'd0;

trai20_one <= 'd0;

trai21_one <= 'd0;

trai22_one <= 'd0;

trai23_one <= 'd0;

trai24_one <= 'd0;

trail_reg_d1 <= 'd0;

trail_reg_d2 <= 'd0;

count <= 'd0;

trail_reg_d3 <= 'd0;

trail_reg_d4 <= 'd0;

sum <= 'd0;

chic <= 'd0;

cno_ride <= 'd0;

cno_ride_reg <= 'd0;

com <= 'd0;

state <= idle;

complete <= 'd0;

trai_ter <= 'd0;

end

else

case (state)

idle:begin

if (pos_valid)

begin

trai1_one <= 'd0; //单位寄存

trai2_one <= 'd0; //单位寄存

trai3_one <= 'd0; //单位寄存

trai4_one <= 'd0; //单位寄存

trai5_one <= 'd0; //单位寄存

trai6_one <= 'd0; //单位寄存

trai7_one <= 'd0; //单位寄存

trai8_one <= 'd0; //单位寄存

trai9_one <= 'd0; //单位寄存

trail0_one <= 'd0; //单位寄存

trail1_one <= 'd0;

trail2_one <= 'd0;

trail3_one <= 'd0;

trail4_one <= 'd0;

trail5_one <= 'd0;

trail6_one <= 'd0;

trail7_one <= 'd0;

trail8_one <= 'd0;

trail9_one <= 'd0;

trai20_one <= 'd0;

trai21_one <= 'd0;

trai22_one <= 'd0;

trai23_one <= 'd0;

trai24_one <= 'd0;

intpart <= 'd0;

decpart <= 'd0;

exponent_reg_d0 <= 'd0;

trail_reg_d0 <= 'd0;

start <= 'd0;

etart <= 'd0;

sum <= 'd0;

count <= 'd0;

trail_reg_d1 <= 'd0;

trail_reg_d2 <= 'd0;

trail_reg_d3 <= 'd0;

trail_reg_d4 <= 'd0;

cno_ride <= 'd0;

cno_ride_reg <= 'd0;

com <= 'd0;

state <= expo;

complete <= 'd0;

trai_ter <= 'd0;

end

else

begin

complete <= 'd0;

state <= idle;

end

end

expo:begin

if ( exponent >= 127 )

begin

state <= trai;

exponent_reg_d0 <= exponent - 127;

end

else

state <= idle;

end

trai:begin

start <= 1'd1;

if (judge)

begin //删除后面0

trail_reg_d0 <= trail>>cnt;

start <= 1'd0;

state <= trai_1;

sum <= 23-cnt;

end

else

state <= trai;

end

trai_1:begin

if (trai_ter == 5)

begin

trai_ter <= 3'd0;

state <= trai_2;

end

else

begin

trai1_one <= 1'b1;

trai2_one <= trail_reg_d0[22-cnt];

trai3_one <= trail_reg_d0[21-cnt];

trai4_one <= trail_reg_d0[20-cnt];

trai5_one <= trail_reg_d0[19-cnt];

trai6_one <= trail_reg_d0[18-cnt];

trai7_one <= trail_reg_d0[17-cnt];

trai8_one <= trail_reg_d0[16-cnt];

trai9_one <= trail_reg_d0[15-cnt];

trail0_one <= trail_reg_d0[14-cnt];

trail1_one <= trail_reg_d0[13-cnt];

trail2_one <= trail_reg_d0[12-cnt];

trail3_one <= trail_reg_d0[11-cnt];

trail4_one <= trail_reg_d0[10-cnt];

trail5_one <= trail_reg_d0[9 -cnt];

trail6_one <= trail_reg_d0[8 -cnt];

trail7_one <= trail_reg_d0[7 -cnt];

trail8_one <= trail_reg_d0[6 -cnt];

trail9_one <= trail_reg_d0[5 -cnt];

trai20_one <= trail_reg_d0[4 -cnt];

trai21_one <= trail_reg_d0[3 -cnt];

trai22_one <= trail_reg_d0[2 -cnt];

trai23_one <= trail_reg_d0[1 -cnt];

trai24_one <= trail_reg_d0[0 -cnt];

state <= trai_1;

trai_ter <= trai_ter + 1'b1;

end

end

trai_2:begin

if (count == exponent_reg_d0) begin

trail_reg_d2 <= trail_reg_d1;

if (trail_reg_d2 == trail_reg_d1)

begin

state <= trai_3;

count <= count + 'd1;

end

else

trail_reg_d2 <= trail_reg_d1;

end

else if (count <= exponent_reg_d0)

count <= count + 'd1;

case (count)

0 : trail_reg_d1[exponent_reg_d0 - count] <= trai1_one;

1 : trail_reg_d1[exponent_reg_d0 - count] <= trai2_one;

2 : trail_reg_d1[exponent_reg_d0 - count] <= trai3_one;

3 : trail_reg_d1[exponent_reg_d0 - count] <= trai4_one;

4 : trail_reg_d1[exponent_reg_d0 - count] <= trai5_one;

5 : trail_reg_d1[exponent_reg_d0 - count] <= trai6_one;

6 : trail_reg_d1[exponent_reg_d0 - count] <= trai7_one;

7 : trail_reg_d1[exponent_reg_d0 - count] <= trai8_one;

8 : trail_reg_d1[exponent_reg_d0 - count] <= trai9_one;

9 : trail_reg_d1[exponent_reg_d0 - count] <= trail0_one;

10: trail_reg_d1[exponent_reg_d0 - count] <= trail1_one;

11: trail_reg_d1[exponent_reg_d0 - count] <= trail2_one;

12: trail_reg_d1[exponent_reg_d0 - count] <= trail3_one;

13: trail_reg_d1[exponent_reg_d0 - count] <= trail4_one;

14: trail_reg_d1[exponent_reg_d0 - count] <= trail5_one;

15: trail_reg_d1[exponent_reg_d0 - count] <= trail6_one;

16: trail_reg_d1[exponent_reg_d0 - count] <= trail7_one;

17: trail_reg_d1[exponent_reg_d0 - count] <= trail8_one;

18: trail_reg_d1[exponent_reg_d0 - count] <= trail9_one;

19: trail_reg_d1[exponent_reg_d0 - count] <= trai20_one;

20: trail_reg_d1[exponent_reg_d0 - count] <= trai21_one;

21: trail_reg_d1[exponent_reg_d0 - count] <= trai22_one;

22: trail_reg_d1[exponent_reg_d0 - count] <= trai23_one;

23: trail_reg_d1[exponent_reg_d0 - count] <= trai24_one;

default: ;

endcase

end

trai_3:begin

if (count == sum+1)

begin

state <= decparti;

trail_reg_d4 <= trail_reg_d3;

com <= sum - exponent_reg_d0;

end

else if ((count > exponent_reg_d0)&&(count<=sum))

count <= count + 'd1;

case (count)

0 : trail_reg_d3[sum] <= trai1_one;

1 : trail_reg_d3[sum-1] <= trai2_one;

2 : trail_reg_d3[sum-2] <= trai3_one;

3 : trail_reg_d3[sum-3] <= trai4_one;

4 : trail_reg_d3[sum-4] <= trai5_one;

5 : trail_reg_d3[sum-5] <= trai6_one;

6 : trail_reg_d3[sum-6] <= trai7_one;

7 : trail_reg_d3[sum-7] <= trai8_one;

8 : trail_reg_d3[sum-8] <= trai9_one;

9 : trail_reg_d3[sum-9] <= trail0_one;

10: trail_reg_d3[sum-10]<= trail1_one;

11: trail_reg_d3[sum-11]<= trail2_one;

12: trail_reg_d3[sum-12]<= trail3_one;

13: trail_reg_d3[sum-13]<= trail4_one;

14: trail_reg_d3[sum-14]<= trail5_one;

15: trail_reg_d3[sum-15]<= trail6_one;

16: trail_reg_d3[sum-16]<= trail7_one;

17: trail_reg_d3[sum-17]<= trail8_one;

18: trail_reg_d3[sum-18]<= trail9_one;

19: trail_reg_d3[sum-19]<= trai20_one;

20: trail_reg_d3[sum-20]<= trai21_one;

21: trail_reg_d3[sum-21]<= trai22_one;

22: trail_reg_d3[sum-22]<= trai23_one;

23: trail_reg_d3[sum-23]<= trai24_one;

default :;

endcase

end

decparti:begin

chic <= 'd1;

if (ltate_done)

begin

chic <= 'd0;

cno_ride <= cno*1000; //扩展1000倍

state <= resu;

end

else

state <= state;

end

resu:begin

cno_ride_reg <= cno_ride>>20;

state <= stop;

end

stop:begin

count <= 'd0;

intpart <= trail_reg_d2;

decpart <= cno_ride_reg;

complete <= 'd1;

state <= idle;

end

default: ;

endcase

end

always @ (*) begin

case (select)

// 小数放大 33554432 倍 (25个)

0: bucket = 524288; //0.5

1: bucket = 262144; //0.25

2: bucket = 131072; //0.125

3: bucket = 65536; //0.0625

4: bucket = 32768; //0.03125

5: bucket = 16384; //0.015625

6: bucket = 8192; //0.0078125

7: bucket = 4096; //0.00390625

8: bucket = 2048; //0.001953125

9: bucket = 1024; //0.0009765625

10:bucket = 512; //0.00048828125

11:bucket = 256; //0.000244140625

12:bucket = 128; //0.0001220703125

13:bucket = 64; //0.00006103515625

14:bucket = 32; //0.000030517578125

15:bucket = 16; //0.0000152587890625

16:bucket = 8; //7.62939453125e-6

17:bucket = 4;

18:bucket = 2;

19:bucket = 1;

20:bucket = 0;

default:;

endcase

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

cno <= 'd0;

select <= 'd20;

ltate <= 'd0;

a0 <= 'd0;

a1 <= 'd0;

a2 <= 'd0;

a3 <= 'd0;

a4 <= 'd0;

a5 <= 'd0;

a6 <= 'd0;

a7 <= 'd0;

a8 <= 'd0;

a10 <= 'd0;

a11 <= 'd0;

a12 <= 'd0;

a13 <= 'd0;

a14 <= 'd0;

a15 <= 'd0;

a16 <= 'd0;

a17 <= 'd0;

a18 <= 'd0;

a19 <= 'd0;

ltate_done <= 'd0;

end

else

case (ltate)

//8'b1000_1100;

0: begin

if (pos_chic)

begin

cno <= 'd0;

select <= 'd20;

ltate <= 'd1;

a0 <= 'd0;

a1 <= 'd0;

a2 <= 'd0;

a3 <= 'd0;

a4 <= 'd0;

a5 <= 'd0;

a6 <= 'd0;

a7 <= 'd0;

a8 <= 'd0;

a10 <= 'd0;

a11 <= 'd0;

a12 <= 'd0;

a13 <= 'd0;

a14 <= 'd0;

a15 <= 'd0;

a16 <= 'd0;

a17 <= 'd0;

a18 <= 'd0;

a19 <= 'd0;

end

else

begin

ltate_done <= 'd0;

ltate <= 'd0;

end

end

1: if (trail_reg_d4[com-1] == 1) begin ltate <= 'd21; select <= 'd0; a0 <= 'd1; end

else begin a0 <= 'd0; ltate <= 'd2; end

2: if (trail_reg_d4[com-2] == 1) begin ltate <= 'd21; select <= 'd1; a1 <= 'd1; end

else begin a1 <= 'd0;ltate <= 'd3; end

3: if (trail_reg_d4[com-3] == 1)begin ltate <= 'd21; select <= 'd2; a2 <= 'd1; end

else begin a2 <= 'd0;ltate <= 'd4; end

4: if (trail_reg_d4[com-4] == 1) begin ltate <= 'd21; select <= 'd3; a3 <= 'd1; end

else begin a3 <= 'd0;ltate <= 'd5; end

5: if (trail_reg_d4[com-5] == 1)begin ltate <= 'd21; select <= 'd4; a4 <= 'd1; end

else begin a4 <= 'd0;ltate <= 'd6; end

6: if (trail_reg_d4[com-6] == 1)begin ltate <= 'd21; select <= 'd5; a5 <= 'd1; end

else begin a5 <= 'd0;ltate <= 'd7; end

7: if (trail_reg_d4[com-7] == 1)begin ltate <= 'd21; select <= 'd6; a6 <= 'd1; end

else begin a6 <= 'd0;ltate <= 'd8; end

8: if (trail_reg_d4[com-8] == 1)begin ltate <= 'd21; select <= 'd7; a7 <= 'd1; end

else begin a7 <= 'd0;ltate <= 'd9; end

9: if (trail_reg_d4[com-9] == 1)begin ltate <= 'd21; select <= 'd8; a8 <= 'd1; end

else begin a8 <= 'd0;ltate <= 'd10;end

10: if (trail_reg_d4[com-10] == 1)begin ltate<= 'd21; select <= 'd9; a9 <= 'd1; end

else begin a9 <= 'd0;ltate <= 'd11;end

11: if (trail_reg_d4[com-11] == 1)begin ltate<= 'd21; select <= 'd10; a10<= 'd1;end

else begin a10 <= 'd0;ltate <= 'd12; end

12: if (trail_reg_d4[com-12] == 1)begin ltate<= 'd21; select <= 'd11; a11<= 'd1;end

else begin a11 <= 'd0;ltate <= 'd13; end

13: if (trail_reg_d4[com-13] == 1)begin ltate<= 'd21; select <= 'd12; a12<= 'd1;end

else begin a12 <= 'd0;ltate <= 'd14; end

14: if (trail_reg_d4[com-14] == 1)begin ltate<= 'd21; select <= 'd13; a13<= 'd1;end

else begin a13<= 'd0;ltate <= 'd15; end

15: if (trail_reg_d4[com-15] == 1)begin ltate<= 'd21; select <= 'd14; a14<= 'd1;end

else begin a14 <= 'd0;ltate <= 'd16; end

16: if (trail_reg_d4[com-16] == 1)begin ltate<= 'd21; select <= 'd15; a15<= 'd1;end

else begin a15 <= 'd0;ltate <= 'd17; end

17: if (trail_reg_d4[com-17] == 1)begin ltate<= 'd21; select <= 'd16; a16<= 'd1;end

else begin a16<= 'd0;ltate <= 'd18; end

18: if (trail_reg_d4[com-18] == 1)begin ltate<= 'd21; select <= 'd17; a17<= 'd1;end

else begin a17<= 'd0;ltate <= 'd19; end

19: if (trail_reg_d4[com-19] == 1) begin ltate<= 'd21; select<= 'd18; a18<= 'd1;end

else begin a18 <= 'd0;ltate <= 'd20; end

20: if (trail_reg_d4[com-20] == 1)begin ltate <= 'd21; select<= 'd19; a19<= 'd1;end

else begin a19<= 'd0;ltate <= 'd22; end

21: begin

if (a0) begin ltate <= 'd2; a0 <='d0; cno <= cno + bucket; end

else if (a1) begin ltate <= 'd3; a1 <='d0; cno <= cno + bucket; end

else if (a2) begin ltate <= 'd4; a2 <='d0; cno <= cno + bucket; end

else if (a3) begin ltate <= 'd5; a3 <='d0; cno <= cno + bucket; end

else if (a4) begin ltate <= 'd6; a4 <='d0; cno <= cno + bucket; end

else if (a5) begin ltate <= 'd7; a5 <='d0; cno <= cno + bucket; end

else if (a6) begin ltate <= 'd8; a6 <='d0; cno <= cno + bucket; end

else if (a7) begin ltate <= 'd9; a7 <='d0; cno <= cno + bucket; end

else if (a8) begin ltate <= 'd10;a8 <='d0; cno <= cno + bucket; end

else if (a9) begin ltate <= 'd11;a9 <='d0; cno <= cno + bucket; end

else if (a10) begin ltate <= 'd12;a10<='d0; cno <= cno + bucket; end

else if (a11) begin ltate <= 'd13;a11<='d0; cno <= cno + bucket; end

else if (a12) begin ltate <= 'd14;a12<='d0; cno <= cno + bucket; end

else if (a13) begin ltate <= 'd15;a13<='d0; cno <= cno + bucket; end

else if (a14) begin ltate <= 'd16;a14<='d0; cno <= cno + bucket; end

else if (a15) begin ltate <= 'd17;a15<='d0; cno <= cno + bucket; end

else if (a16) begin ltate <= 'd18;a16<='d0; cno <= cno + bucket; end

else if (a17) begin ltate <= 'd19;a17<='d0; cno <= cno + bucket; end

else if (a18) begin ltate <= 'd20;a18<='d0; cno <= cno + bucket; end

else if (a19) begin ltate <= 'd22;a19<='d0; cno <= cno + bucket; end

else begin cno <= cno + bucket; ltate <= ltate; end

end

22: begin ltate_done <= 'd1; if (state == resu) ltate<= 'd0; else ltate <= ltate; end

default: ;

endcase

end

endmodule // 二进制数转浮点数 , A或B 使用一个即可

module floatingpoint32(

input clk,

input rst_n,

input en,

input[31:0] A,B,

output reg [31:0] C,

output reg valid

);

reg[7:0] AE=0,BE=0,CE=0,DE=0;

reg AS=0,BS=0,CS=0,DS=0;

reg[24:0] AF,BF,CF;

reg[7:0] index=0;

reg drag_0,drag_1,drag_2;

integer in;

integer tem;

always @(A or B)//上升沿触发

begin

if(en==1)

begin

AE=A[30:23]; // 阶码8位 用的是移码表示 +127 01111111

AF={2'b01,A[22:0]};//把缺省的1给补上 同时考虑做加法时 有可能产生进位 所以补齐23+1+1 共25位

AS=A[31]; // 最高位 即符号位

BE=B[30:23];

BF={2'b01,B[22:0]};

BS=B[31];

//如果某一方阶码大,则符号位一定是在大的一方

if (A[30:0]==0) //如果A是0,则结果就是B了

begin

CS=BS;

CE=BE;

CF=BF;

end

else if(B[30:0]==0) //如果B是0,则结果就是A了

begin

CS=AS;

CE=AE;

CF=AF;

end

else //A、B都不为0的情况下

begin

if(AE>BE) //A的阶码大于B的阶码

begin

CE=AE; //对阶

DE=AE-BE; //阶码做差

BF=(BF>>DE); //右移

if (AS==BS) //如果A、B符号位相同,就做加法

begin

CS=AS;

CF=AF+BF;

end

else if (AS!=BS) //如果A、B的符号位不相同,就做减法

begin

CS=AS;

CF=AF-BF;

end

end

else if(AE>DE); //右移

if (AS==BS) //如果A、B符号位相同,就做加法

begin

CS=AS;

CF=AF+BF;

end

else if (AS!=BS) //如果A、B的符号位不相同,就做减法

begin

CS=BS;

CF=BF-AF;

end

end

else if(AE==BE) //A的阶码等于B阶码

begin

CE=AE; //首先确定结果的阶码

if (AS==BS) // 如果A、B符号位相同,就做加法

begin

CS=AS;

CF=AF+BF;

end

else //如果A、B的符号位不相同,就做减法

begin

CS=BS;

CF=BF-AF;

end

end

//归一化,寻找CF第一个1,并将其前移

in=24;

tem=0;

while(tem==0&&in>=0)

begin

if(CF[in]!=0)//如果尾数最高位CF[24]即尾数第25位不为0,则可以进行尾数规一化。

begin

tem=1;

index=in; //index指示的就是尾数为1的那位 就是CF[index]=1

end

in=in-1; //这里要注意在找到index之后 in还会减一次

end //while循环这里结束了

if(in<0)//相加得0或者相减的结果就是0 也是指尾数运算结果为25位的0

begin

CS=0; //运算结果就是0了

CE=0;

CF=0;

end

else if(index==24)//如果在24位,则尾码右移,阶码加一

begin

CE=CE+8'b1; //结果C的阶码要加1

CF=(CF>>1); //尾数要向右移一位 1.xxxxxxxxxx

end

else

begin

index=8'd23-index; //index指示的是需要移位数

CE=CE-index; //阶码减去左移的尾数

CF=(CF< 实验结果

结果对比

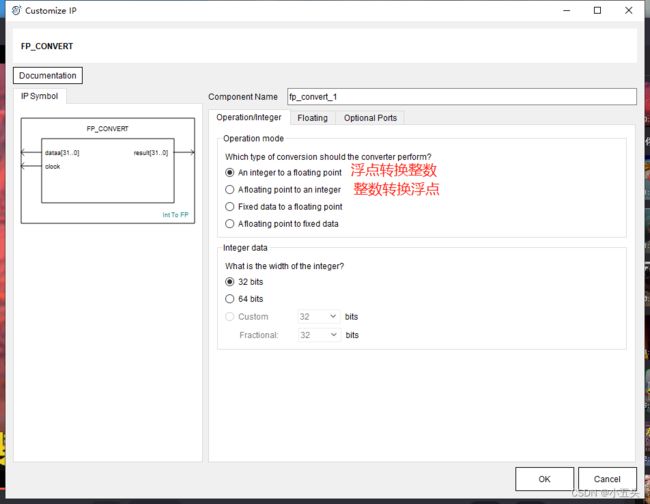

使用eLinx工具进行开发

module FD(

input wire clk

);

wire [31:0] dataa = 520;

wire [31:0] result;

fp_convert_1 u_fp_convert_1(

.clock (clk),

.dataa (dataa),

.result (result)

);

endmodule

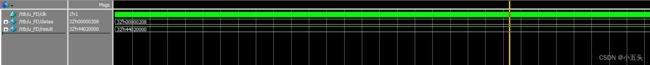

实验结果

结果对比

结论

精度和范围:定点数的精度和范围是固定的,所以在进行浮点数到定点数转换时,需要确定合适的位宽和小数点位置,以满足应用的精度要求和数值范围。舍入方式:在进行浮点数到定点数转换时,需要选择适当的舍入方式。常见的舍入方式包括向上舍入、向下舍入、四舍五入等。选择合适的舍入方式可以在精度和性能之间进行权衡。运算延迟:定点数运算的延迟可能与浮点数运算有所不同。在进行浮点数到定点数转换后,需要对设计进行重新评估,以确保其满足时序要求。特别是在高速计算或实时系统中,这一点尤为重要。协议和接口:如果你的设计需要与其他模块或设备进行通信,确保你了解并遵循相应的协议和接口规范。有时,浮点数转换定点数可能涉及到数据格式的转换和解析,这需要与其他模块进行正确的数据交互。测试和验证:在进行浮点数转换定点数的设计时,确保进行充分的测试和验证。这包括对各种输入情况和边界条件进行测试,以确保转换的正确性和性能。优化和资源利用:定点数表示通常可以更好地利用 FPGA 的资源,但需要注意设计中的资源使用情况。在进行浮点数转换定点数时,考虑优化算法和数据结构,以提高资源利用率并满足性能要求。

参考资料

-

《数字信号处理》(Digital Signal Processing)一书,作者:John G. Proakis, Dimitris G. Manolakis。该书介绍了数字信号处理的基本概念和技术,包括浮点数和定点数表示以及相应的转换方法。

-

《嵌入式系统设计与优化》(Embedded Systems Design and Optimization)一书,作者:Wayne Wolf。该书讲解了在嵌入式系统中使用定点数进行计算的技术和优化方法,包括浮点数转换定点数的相关内容。

-

《FPGA原理与应用》(FPGA Prototyping by VHDL Examples)一书,作者:Pong P. Chu。该书介绍了在FPGA上进行数字系统设计的基本原理和方法,其中包括浮点数转换定点数的实现和应用。

-

IEEE标准754-2008《二进制浮点算术标准》(IEEE Standard for Floating-Point Arithmetic)是关于二进制浮点数算术的国际标准。它详细描述了浮点数的表示方法、转换规则以及相应的运算规范。

-

学术论文和研究文章:可以通过学术搜索引擎如Google Scholar、IEEE Xplore等搜索相关的学术论文和研究文章,了解最新的浮点数转换定点数的研究成果和应用实践。