高速PCB基础-电源分配网络

电源分配网络

电源分配网络又称为电源配送网络 (PDN) ,包含从稳压模块 (VRM) 到芯片的焊盘,再到裸芯片内分配本地电压和返回电流的片上金属层在内的所有互连。其中有稳压模块、体去耦电容器、过孔、互连、电路板上的平面、板外附加电容器、封装的焊球或引脚、装在电路板上的封装中的互连、键合线或 C4 焊球、芯片上的内部互连等。

电源分配网络的首要和基本要求:保持芯片焊盘间的供电电压恒定,并使它能够维持在一个很小的容差范围内通常在 5% 以内。

电源分配网络的作用有3个:保持芯片焊盘问的供电电压恒定,使地弹最小化,使电磁干扰问题最小化。

在大多数设计中,用于供应电力的电源、分配网络互连也总是用于运送信号线的返回电流。这些电源分配网络互连的第二个作用是提供一个低阻抗的信号返回路径。

提供低阻抗路径的最简单方法是使互连足够宽从而使返回电流尽可能地分布开,并且让信号线保持分离,使得它们的返回电流不会相互重叠。若不满足这些条件,则返回电流将会聚

集,不同信号的返回电流将会互相重叠。其结果就是产生地弹,也称为同时开关躁声 (SSN)开关噪声。

问题的根源

电压出现下沉,不能使用稳定度更高的芯片来解决,因为电压下沉来源于互连的阻抗。

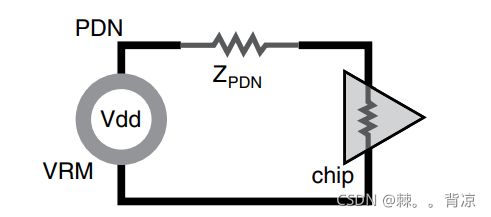

从稳压模块经电源分配网络连到芯片焊盘。电压分配网络的阻抗造成了压降。

从片上焊盘看过去的电源分配网络阻抗,通常是一个与频率相关的阻抗,记为 Z ( f ) Z(f) Z(f)

当具有一定频谱宽度的电流 I ( f ) I(f) I(f)流过该电源分配网络时,电源分配网络上将产生电压降:

V ( f ) = I ( f ) × Z ( f ) V(f)=I(f)\times Z(f) V(f)=I(f)×Z(f)

电源分配网络上的这一压降表明稳压器输出的恒定电压是芯片得不到的,在进入芯片前已被改变。芯片焊盘上的电压变化必须在给定的电流波动下小于某一电压噪声容差,就是通常所说的纹波。这就要求电源分配网络阻抗必须低于某一最大容许值,即目标阻抗:

V r i p p l e > V P D N = I ( f ) × Z P D N ( f ) V_{ripple}>V_{PDN}=I(f)\times Z_{PDN}(f) Vripple>VPDN=I(f)×ZPDN(f)

Z P D N ( f ) < V r i p p l e I ( f ) = Z t a r g e t ( f ) Z_{PDN}(f)<\frac{V_{ripple}}{I(f)}=Z_{target}(f) ZPDN(f)<I(f)Vripple=Ztarget(f)

其中 V r i p p l e V_{ripple} Vripple芯片的电压噪声容差(V);

V P D N V_{PDN} VPDN电源分配网络互连上的噪声压降(V);

I ( f ) I(f) I(f)芯片消耗电流的频谱(A);

Z P D N ( f ) Z_{PDN}(f) ZPDN(f)芯片焊盘看过去的电源分配网络阻抗曲线(Ω);

Z t a r g e t ( f ) Z_{target}(f) Ztarget(f)电源分配网络所容许的最大阻抗(Ω)

电源分配网络导体上的轨道塌陷或电压噪声的根本原因在于流过电源分配网络阻抗的芯片电流导致电源分配网络互连上产生了电压降。

假定芯片中的电流产生了波动,如果要保持芯片焊盘之间的电压稳定,就需要保持电源分配网络阻抗低于目标阻抗值。这是电源分配网络设计中最根本的指导准则。

电源分配网络稳定时,电压恒定,如果电流改变(即出现电流),那么互连阻抗会分去一部分电压,导致电压下降。

电源分配网络的设计准则

1、.让电源和地平面成为相邻的平面层,平面之间的介质要尽量薄,并且还要让平面尽可能靠近电路板层叠结构的表面层;

2、在去耦电容器焊盘和连往内层电源/地平面腔的过孔之间,使用尽可能短而宽的表层走线,并在具有最低回路电感的位置放置电容器;

3、使用 SPICE 选择最佳的电容器容值及其个数,以使阻抗曲线低于目标阻抗。

如何确定目标阻抗

电源分配网络的最大阻扰,即目标阻扰,就是形成小于可接受纹波压降的最大阻抗。可以由下式得到:

Z P D N × I t r a n s i e n t = V n o i s e < V D D × r i p p l e Z_{PDN}\times I_{transient}=V_{noise}

即:

Z t a r g e t < V D D × r i p p l e I t r a n s i e n t Z_{target}<\frac{V_{DD}\times ripple}{I_{transient}} Ztarget<ItransientVDD×ripple

I t r a n s i e n t I_{transient} Itransient表示最坏情况下的瞬间电流,

Z t a r g e t Z_{target} Ztarget表示目标阻抗

ripple表示可容许的波纹

V D D V_{DD} VDD表示特定轨道的供电电压

最佳的电源分配网络阻抗值应低于但不应远低于目标阻抗值。

芯片手册中没有提供最坏的瞬间电流,但是一般给出每个电压轨道的峰值电流,可以根据经验法则粗略的估计瞬时电流。即:

I t r a n s i e n t = 0.5 I m a x I_{transient}=0.5I_{max} Itransient=0.5Imax

I m a x I_{max} Imax表示芯片最大的总电流。

同时也可以用最坏的功耗情况来估计,此时有: Z t a r g e t ( f ) < 2 V d d 2 × r i p p l e P m a x Z_{target}(f)<2\frac{V_{dd}^2\times ripple}{P_{max}} Ztarget(f)<2PmaxVdd2×ripple

一些FPGA公司,如Altera公司会提供计算工具,下表时Altera公司的Stratix II GX FPGA器件的分析结果:

下图是一个成功设计的阻抗曲线

当电源分配网络的阻抗曲线(下图)低于目标阻抗时,最坏情况下的电压噪声(上图)就低于对纹波的要求。其中方波信号是芯片消耗电流而平滑的曲线是供电轨道上的电压。

但是如果阻抗曲线上有一个峰值超过了目标阻值的指标要求,并且最坏情况下的电流的峰值刚好落在该阻抗峰值的位置,波纹就有可能超标。

当电源、分配网络的阻抗曲线超过目标阻抗的指标要求(下图) ,并且电流的峰值频率与阻抗峰值重叠时,就会产生过冲(上图)。)。上图中的方波是流过芯片的消耗电流。振铃波形是供电轨道上的电压。内嵌的图形是在该电源分配网络中测得的电压噪声,显示了电源分配网络阻抗曲线峰值引起的典型振铃响应

不能盲目的将一种产品的电源分配网络盲目的移到其他产品的电源分配网络中。

电源分配网络工程化建模

电源分配网络可以在频域里划分5个成简单区段。

在低于10kHz的频率范围内,稳压模块的性能对电源分配网络阻抗起决定性的作用。

在10~100kHz的范围,体去耦电容器对电源分配网络的阻抗起决定作用,通常是一些在稳压模块作用频率范围上提供低阻抗的电解电容及钽电容。

最高频率时的阻抗取决于片上电容,这一容性阻抗是芯片在GHz所看到的电源分配网络的唯一特性。

任何芯片与电路板的接口都存在一些寄生电感。这通常取决于封装、过孔,以及过孔到电源/地平面连接处的扩散电感。

板级电源分配网络设计的频率范围约从 100 kHz 到100 MHz 。这正是电路板平面和多层陶瓷贴片电容器 (MLCC) 发挥作用的频率范围。

稳压模块

稳压模块 (VRM) 决定了电源分配网络的低频阻抗。下图给出了一个所测典型稳压模块的阻抗曲线。此外也给出了一个简单双电容模型的阻抗曲线。

在10Hz到40MHz 的频率范围内用Ultimetrix 阻抗分析仪测量一个典型稳压模块得到的阻抗曲线。图中显示了稳压模块在开启和关闭时的测量阻抗以及稳压模块基于双电容器模型的仿真阻抗

可以看出在大约4kHz,稳压模块的输出阻抗由无源电容器决定,有源稳压器对阻抗不起作用,无论稳压器是开或关,输出阻抗都相同。

片上电容

片上去耦电容决定了最高频率时的电源分配网络阻抗。片上电容有3个成因:电源和地轨道金属层之间的电容,所有的 p/n 管的栅极电容,以及各种寄生电容。

高频时片上电容为电源分配网络提供了低阻抗。

如果目标阻抗为 10 mΩ 那么片上电容将会在高于 100 MHz 的频率时起到显著的去耦作用。

封装屏障

封装引脚中存在串联的电感。其阻抗为 Z = 2 π f L Z=2\pi fL Z=2πfL,这将导致无论板级电源分配网络怎么设计,都不可能将芯片看到的电源分配网络阻抗减小到比封装引脚更小。

一般情况下,封装与目标阻抗一起把板级阻抗的有效频率限制在 100 MHz 以下。除非有其他反面的佐证信息,这就是板级电源分配网络设计目标通常设置为不高于 100 MHz 频率的原因。