ARM处理器核心概述

一、基于ARM处理器的嵌入式系统

- ARM核深度嵌入SOC中,通过JTAG口进行外部调试。

- 计通常既有外部内存又有内部内存,从而支持不通的内存宽度、速度和大小。

- 一般会包含一个中断控制器。

- 可能包含一些Primece外设,需要从ARM公司取得授权。

- 总线使用ARM的标准如AMBA总线。

二、ARM处理器存储器子系统相关术语

- MPU(内存保护单元)

- 面向实时控制领域

- 控制内存访问权限

- 控制器内存区域的属性(Cacheable,bufferable)

- ARM的IO空间和主存空间是统一编址。

- IO空间不能设置缓存,主存可以设置缓存

MMU(内存管理单元)

面向复杂的APP的processor,如移动终端

具有MPU的所有特性

提供虚拟地址到物理地址的转换,提供操作系统的续存管理

嵌入式LINUX是支持MMU的

Cache(高速缓存)

快速本地内存

存放最近被访问过的内存副本

TCM(紧耦合内存)

快速本地内存

特定地址范围

Write buffer(写缓存区)

减少写数据到外部内存的次数

三、ARM处理器体系结构的发展

注意:相同体系可能有完全不同的实现

ARM7TDMI-arch v4T.冯诺伊曼结构,3级流水线

ARM920T-arch v4T.哈佛结构,5级流水线,具有MMU

四、典型ARM CPU核

4.1 ARM7TDMI

T:Thumb架构扩展,从而提供两个独立指令集:

ARM指令,均为32位

Thumb指令,均为16位

根据运行状态选择指令集

D: 内核具有Debug扩展结构

M:增强乘法器(32 x 8)支持64位结果

I:EmbeddedCE逻辑

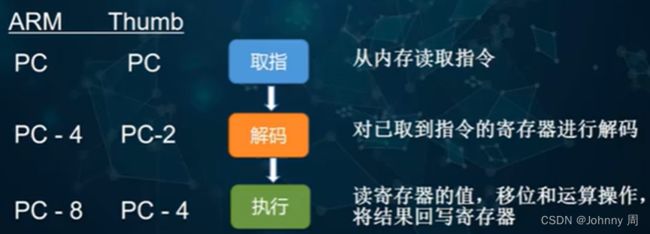

3级流水线:取值解码执行,从而允许 一些操作同时运行。Pipeline

需要注意的是,PC指向的是将要被预取的指令,而不是执行的指令。一般调试工具会隐藏这个细节。

理想的3级流水线

- 所有的操作都是在寄存器进行(单独一个周期执行)

- 6个时钟周期执行了6条指令

- Clock cycles per instruction (CPI) = 1

- 存在一个LDR的内存读取操作指令

- 6个时钟周期执行了4条指令

- Clock cycles per instruction (CPI) = 1.5

4.2 ARM9TDMI

- V4T架构,5级流水线,CPI约为1.5

- 时钟频率得到最大提高

- 哈佛体系,增加了可访问内存的带宽,可同时对指令内存和数据内存进行访问。

- 一般支持内置Cache.

ARM9TDMI的流水线技术

ARM9TDMI的理想流水线

LDR指令不会引起流水线互锁

6个时钟周期执行了6条指令

Clock cycles per instruction (CPI) = 1

紧接着LDR指令后用相同寄存器的数据操作会引起互锁,原因使用相同的寄存器,后面的指令执行依赖相同寄存器。

7个时钟周期执行了6条指令,CPI=1.2

4.3 ARM11

ARM V6架构,8级流水线,支持静态和动态的分支预测以及返回堆栈

低延迟的中断模式

内部可配置的TCM

支持64位内存接口

集成的VFP处理器(可选)