485规范详解

485接口器件经常用,但却很少对其规范有过深入学习,现对照规范详细分解。

概述:

485规范的全程是ANSI/TIA/EIA-485-A,于1998年发布。

本规范和ISO/IEC 8482:1993规范兼容,和上阶段规范(EIA RS-485)相比,无新增技术内容,可兼容。

本规范没有定义信号质量、时序、协议、引脚定义、供电电压、工作温度等参数,推荐被引用于提供了详细电性能参数的标准或详细规范。

几个基本的参数定义:

- 共模电压VCM:定义为一堆差分线对地电压的中值,实际总线中,由地电位差、发送器失调电压以及长导线引起的噪声电压组成;

- 差模电压:定义为一堆差分线只差;

- 发送器,传输信号元,generator;接收器,receiver;收发器,transceiver。

发送器:

包含被动(passive)、逻辑0和逻辑1三种基本状态,被动状态相当于一个单位负载(UL,此规范并没有说明单位负载的阻值,根据其他芯片手册判断,应为12kΩ,即485总线要求带32个12kΩ的负载)。

4.2.1 开路输出电压:

空载时,差模电压绝对值在1.5V~6.0V之间,单根对地电压不超过6.0V。

4.2.2 差分、失调输出电压:

并联54Ω电阻,差模电压绝对值在1.5V~5.0V之间,两种不同逻辑的差分电压差值不超过0.2V,失调电压(电阻中点接地测量)在-1.0V~+3.0V,两种不同逻辑之间的差值不超过0.2V。

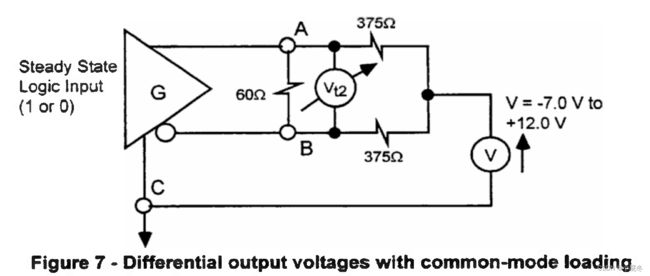

4.2.3 差分输出电压+共模负载:

并联60Ω负载,能承受-7.0V~12.0V的外部共模电压,在此范围内差分电压值为1.5V~5.0V。

4.2.5 短路输出特性:

差分线间短路不应损坏芯片,单根差分线能承受-7.0V~+12.0V的外部共模电压而不损坏。

4.2.6 电压过冲特性:

被动状态的发送器和接收器需要能够承受短时冲击(正常输出的发送器能否承受短时冲击,规范并没有指出,待定),冲击条件为±25V/15us/1%占空比,且源阻抗为100Ω。

4.2.7 输出信号波形:

并联54Ω和50pF电容作为负载,有如下信号质量要求:

(1)上升时间(0.1~0.9)不超过0.3tui(tui为0或1持续的时间,不是整个周期);

(2)超调不得超过Vss的10%;

(3)差分电压之在任何情况下都不能超过5.0V。

接收器:

4.3.1 输入电压范围:

单端对地可承受-7V~12V的外部输入电压,差分电压不超过6V。

4.3.2 输入阈值:

±200mV,可以加严,但是不能不满足(SN65LBC175A的门限为-10mV/-200mV)。

4.3.3 输入平衡测量:

当差分电压在±0.4V范围内波动时,逻辑值不可翻转(待定)。

4.3.5 电压过冲特性:

同发送器。

总结:

1. 对发送器的要求

(1)单端对地电压(任意一根差分线)不能超过6.0V(空载 or 带载),并且要能够承受-7.0V~12.0V的共模电压而不损坏;

(2)差分输出电压差在1.5V~5.0V之间(空载时为1.5V~6.0V),即32个节点或54Ω负载时差分电压不得低于1.5V;

(3)共模电压:范围在-1.0V~3.0V之间,但要能够承受-7.0V~12.0V的共模电压而不损坏;

(4)电压冲击:要能承受±25V/15us/1%占空比的脉冲冲击而不损坏;

(5)信号质量:上升/下降时间不超过0.15T,超调不超过10%。

2. 对接收器的要求

(1)单端对地电压要能够承受-7.0V~12.0V而不损坏;

(2)要能够承受6V以下的差模电压,逻辑翻转阈值为±200mV;

(3)共模电压:能承受的最大共模电压为-6.9V~11.9V之间(为了保证收到的信号有效,所以不是-7V~12V);

(4)电压冲击:要求同发送器。

3. 拓扑:

规范规定总线最大传输速率为10Mbps,实际上已经出现了超过10Mbps的收发器。

485总线上最多挂在32个节点(一收一发算一个节点),节点之间推荐菊花链式、手牵手连接方式,stub长度尽量短,不推荐任何其他拓扑方式(星型、树形、树杈型等)。