EDA07--VCS仿真验证(一)

这里写目录标题

- 一、VCS 简介

- 二、VCS 流程

- 三、VCS第一步 编译

-

- 3.1 -help

- 3.2 -o filename

- 3.3 -f file

- 3.4 -line

- 3.5 -system verilog

- 3.6 -Mupdate[=0]

- 3.7 -debug

- 3.8 -R

- 3.9 -s

- 3.10 +v2k

- 3.11 -I

- 3.12 +vcsd

- 3.13 +cli+level_number选项

- 3.14 race选项

- 四、VCS第二步 VCS 运行

- 五、VCS第三步 VCS 调试

-

- 5.1 DVE简介

- 5.2 DVE交互式

- 5.2 DVE后处理模式

- 6.1 覆盖率类型

- 6.2 覆盖率步骤

- 6.3 覆盖率统计

-

- 6.3.1 代码覆盖率仿真

- 7.3.2 代码覆盖率查看

一、VCS 简介

VCS用于在Linux下仿真.v代码,vcs六大功能:

·System Verilog

·OVA

·NTB

·DVE调试环境

·覆盖率统计

·DirectC

·增量编译

·64-bit模式

·混合信号仿真

本文讲解VCS的知识内容,具体操作步骤单独写一篇…

二、VCS 流程

VCS-DVE仿真由三步构成:编译、仿真、调试。提前编写好设计文件和Testbench的.v文件。

首先经过编译程序,(这一步检查代码有无语法错误,类似于Modelism里面的complier功能)编译的默认结果命名为simv ;

然后运行上一步得到的simv既可以得到仿真结果;采用互动模式时,每一步执行与否又使用者决定,采用后处理模式时,程序根据.v文件设计自动开始执行、自动决定何时停止仿真(通常仿真不再变化或者执行到 s o o p / soop/ soop/finish)。

最后调试即就是查看波形。

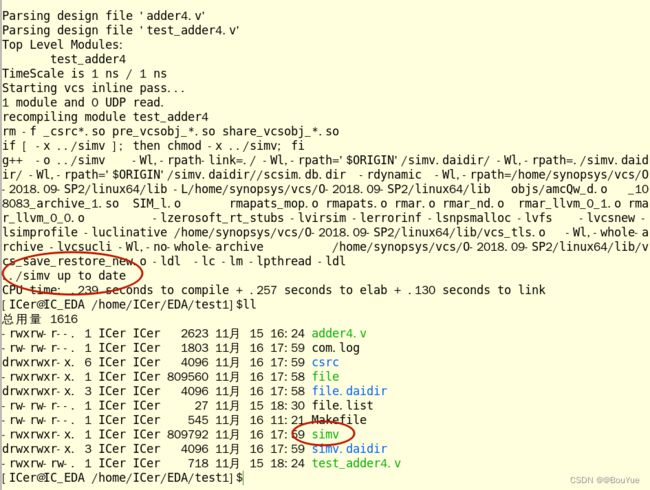

编译成功会提示:…/simv up to date;

仿真成功会提示:$finish called from file “./test_adder4.v”, line 38.

$finish at simulation time 46400

如图:

三、VCS第一步 编译

编译格式:

vcs [若干可选项] [若干.v文件或者文件路径列表] -l com.log

理论上讲最简单的一句 vcs - debug_all adder.v adder_tb.v 就可以实现编译,但由于软件环境不一样(有可能是虚假机,也有可能是VCS软件安装,因为刚开始学,具体我也不知道,以后搞明白了再说明),总之再编译时需要加上一些选项才能保证编译的顺利进行。例如:

vcs -full64 -debug_all -timescale=1ns/1ns adder4.v test_adder4.v +v2k -l com.log

-full64 表示在64位的Linux系统中运行;

-debug_all 编译命令;

-timescale=1ns/1ns 仿真时间精度;

adder4.v test_adder4.v 设计.V文件;

+v2k 支持verilog2001特性;

-l com.log 把VCS编译和运行信息的保存在com.log文件中。

常用的编译选项有很多,这里介绍一些常用的:

3.1 -help

格式示例:

vcs -full64 -help

空格翻页,ctrl+c退出。

3.2 -o filename

格式示例:

vcs -full64 -debug_all -o file -timescale=1ns/1ns adder4.v test_adder4.v +v2k -l com.log

编译产生的可执行文件名,默认为simv,同时产生simv.daidir文件。

可自行改变仿真文件simv的名为file,同时simv.daidir文件改名为file.daidir。

3.3 -f file

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k -l com.log

vcs -full64 -debug_all -timescale=1ns/1ns adder4.v test_adder4.v +v2k -l com.log

这两行命令一个结果,即当我们设计文件太多时,逐个列举显然麻烦,故用-f lile把所有的设计.v文件的相对路径打包起来,以提高命令书写效率。命令结果不展示了,这里展示file.list ,使用命令find -name “*.v” > file.list即可产生,文件内部:

3.4 -line

格式示例:

vcs -full64 -debug_all -line -timescale=1ns/1ns -f file.list +v2k -l com.log

3.5 -system verilog

格式示例:

vcs -full64 -debug_all -line -system -timescale=1ns/1ns -f file.list +v2k -l com.log

这行命令使能system verilog 语法功能,当设计.v文件有system verilog时,必须有这行。

3.6 -Mupdate[=0]

格式示例:

vcs -full64 -debug_all -line -system -timescale=1ns/1ns -f file.list +v2k -Mupdate[=0] -l com.log

默认情况下每次编译后更新Makefile文件,如果希望每次编译后不更改,则增加=0,缺少为默认情况,启动增量编译,每次编译更新Makefile文件。

3.7 -debug

-debug有很多选项,这个以后再讲。这里先无条件加在后面,能DVE和UCLI调试功能,几乎每个都有,必须要加,不然编译不过去。

3.8 -R

格式示例:

vcs -full64 -R -debug_all -line -system -timescale=1ns/1ns -f file.list +v2k -Mupdate[=0] -l com.log

在编译执行完成后立即运行生产的可执行文件,启动仿真器。相当于一次性走两步,如下:

3.9 -s

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k +cli -R -s -l com.log

在仿真一开始就停止,同时进入CLI交互模式,一般情况下,-s -R +cli一起使用,并且这是一个运行选项,即需要后续操作。

3.10 +v2k

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k -l com.log

启动verilog IEEE1364-2001标准,源代码用到了verilog IEEE1364-2001标准则必须加。(一般都用到了,加上就对了)。

3.11 -I

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k -I -l com.log

前一个是I,后一个是l,只有在采用交互或者后处理调试使用该选项。

3.12 +vcsd

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k -I -R +vcsd -l com.log

使能VCS直接通道仿真接口,默认为程序语言接口(PLI),可以加快VCS和VirSim之间通信。同样只有在采用交互或者后处理调试使用该选项。

3.13 +cli+level_number选项

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k +cli+4 -l com.log

使能CLI交互调试命令,级数表示使能命令程度,分为1-4。

cli+1或cli:

只能读线网和寄存器,以及写寄存器命令。

cli+2:

cli+1的功能+信号回调命令,该命令在信号改变时能够进行某些处理,例如break signal_name。

cli+3:

上述功能+对线网强制赋值与释放。

cli+4:

上述功能+对寄存器强制赋值与释放。

3.14 race选项

格式示例:

vcs -full64 -debug_all -timescale=1ns/1ns -f file.list +v2k +race -l com.log

检查设计是否有竞争,并将结果写入race.out文件中,无竞争则不产生。

四、VCS第二步 VCS 运行

编译完成后会提示一句**…/simv up to date和一系列文件,其中最主要是一个simv**文件,运行VCS其实就是运行生产的svim文件。基本格式为:

simv [选项]

选项表示如何来运行simv文件,主要有:

1、-l log_name.log

此选项用于产生日志文件,并将运行过程所有信息输出到log_name.log文件中。

2、-s

此选项用于仿真一开始就停止,并进入CLI交互模式中。

演示:

此时说明编译成功,输入仿真指令:simv -l sim.log,如下图说明运行仿真成功。

此时说明编译成功,输入仿真指令:simv -l sim.log,如下图说明运行仿真成功。

五、VCS第三步 VCS 调试

VCS仿真工具存在三种调试模式,CLI交互调试模式、VirSim交互调试模式和VirSim后处理模式。这里介绍VirSim,即使用VCS图形化集成调试环境。

5.1 DVE简介

DVE是VCS的一个图形化的集成调试环境,可以提供波形、结构、代码级的调试。DVE具有两种运行方式:交互方式(Interactive)和后处理模式(Post-process mode)。

交互方式是在完成VCS编译后,启动DVE,在DVE界面中进行仿真,可以对仿真过程进行控制。通俗来讲就是仿真跑多长时间是通过命令输进去的(run 100之类),输多长时间,跑多长时间。

后处理方式则是在 VCS 编译并仿真结束后,启动DVE 来调用、检查仿真结果。通俗来讲就是按照仿真文件Testbench内部initial模块所施加的激励来逐句运行,直到运行到 f i n i s h 或 者 finish或者 finish或者stop结束仿真。把仿真得到的波形文件存储到文件中,用DVE来查看结果波形。

5.2 DVE交互式

1、利用下命令完成源文件编译:

vcs -full64 -sverilog -debug_all -timescale=1ns/1ns adder4.v test_adder4.v -l com.log

2、启动DVE观察波形,利用下命令启动DVE:

dve &

3、手动操作仿真时间(DVE中输入命令{run 1000}),查看波形。

5.2 DVE后处理模式

后处理是仿真得到的波形文件存储到文件中,用DVE来查看结果波形。其步骤:

1、生产VCD+文件;利用下命令完成源文件编译:

vcs -full64 -sverilog -debug_all -timescale=1ns/1ns adder4.v test_adder4.v -l com.log

利用下命运行仿真器生产.vcd或者.vpd文件:

simv

2、启动DVE观察波形;利用下命令启动DVE:

dve

六、代码覆盖率

6.1 覆盖率类型

代码覆盖率用于指示硬件代码有多少经过验证,即到什么程度才算设计达标,一般验证有以下指标:

1、line 行覆盖, 检查是否执行了所有语句;

2、cond 条件覆盖, 检查是否执行了所有条件组合;

3、fsm 状态机覆盖, 检查是否执行了所有状态转移;

4、tgl 翻转覆盖, 检查信号是否由0到1和由1到0;

5、path 路径覆盖, 检查if 和case条件表达式是否为真,以及又该条件控制的initial和always块中过程赋值语句执行过程;

6、branch 分支覆盖, 检查if 、case、 (?:)所建立分支语句执行情况;

7、assert SVA断言覆盖率;

8、obc 可观察覆盖率。

6.2 覆盖率步骤

1、编译,在编译时加入覆盖统计选项,指出要编译时覆盖率统计的类型。例如:

vcs -f file.list -timescale=1ns/1ps -full64 +v2k -cm line+cond+fsm+tgl -debug_all

2、仿真,在仿真时加入覆盖统计选项,指出要仿真时覆盖率统计的类型。例如:

simv -cm line+cond+tgl+fsm -l sim.log

3、启动cmView,在批处理模式下生成报告,或启动GUI模式查看结果。

6.3 覆盖率统计

6.3.1 代码覆盖率仿真

用vcs进行代码覆盖率统计时,基本选项有四个:

1、-cm<option> 统计代码覆盖率类型,包括7.1讲的8个,用+好连接;

2、-cm_dir<directory_path_name> 指定代码覆盖率结果存放路径,不指定默认sim.vdb文件

3、-cm_hier<filename> 指定代码覆盖率统计范围,可以指定module名称、层次名和源文件。

一个例子:

一个例子:

vcs \

-f file.list \

-timescale=1ns/1ns \

-full64 +v2k \

-debug_all \

-cm line+cond+fsm+tgl \

-cm_dir cm_test

运行完之后会产生一个cm_test.vdb的文件夹,用于存放统计结果。

7.3.2 代码覆盖率查看

查看覆盖率有两种方法,第一种利用DVE打开覆盖率文件查看,另一种打开HYML文件。

命令:

dve -full64 -cov -dir simv.vdb