【以太网硬件二十一】USXGMII是什么?-Part2

个人主页: highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

PCS功能细节

XGMII到USXGMII的映射

带内配置和状态信号

自协商相关

电气特性

PCS功能细节

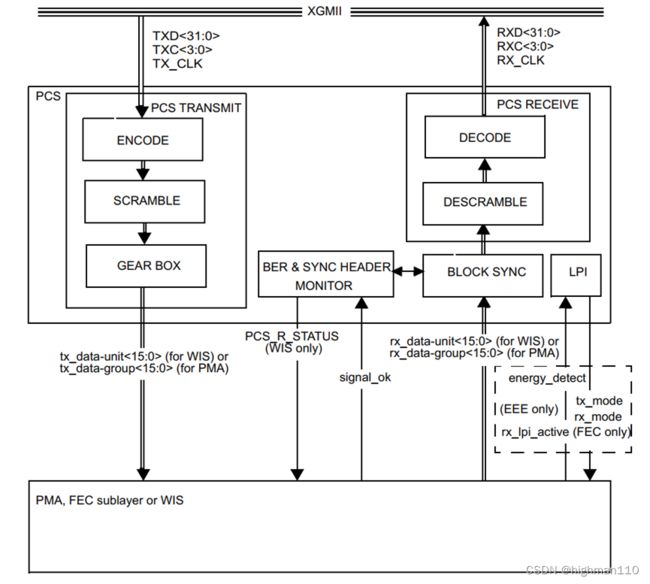

USXGMII把并行的XGMII转成了串行输出,为了保证链路的可靠传输,必然要对传输数据进行一定处理,这就是PCS层的主要功能:编码,USXGMII沿用10Gbase-R PCS的设计,现在把10Gbase-R PCS规范框图贴出来:

从上图可以看到PCS由发送模块(包括编码、加扰、gearbox)、接收模块(解码、解扰)、block同步模块、BER和同步头监控模块组成。

PCS发送过程如下图:

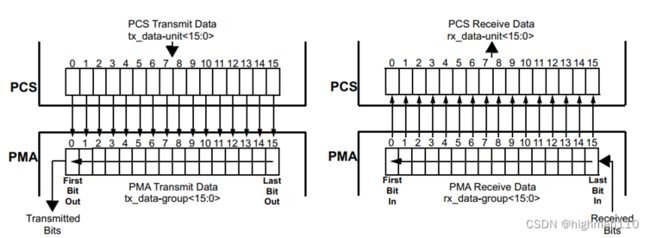

XGMII两次传输的64bit数据或控制字符经过扰码,然后添加2bit的同步头组成一个66bit的block,同步头为01表示数据block,同步头为10表示控制block。可以看到同步头是整个block中唯一确定会发生0,1跳变的位置,所以同步头可以用来做block同步。block然后经过gearbox将66bit数据以16bit的并行接口发给PMA。注意上图中的箭头,传输顺序是bit0先发,最后是bit65,且同步头是不经过扰码的。下图是PCS到PMA之间的16bit接口传输示意:

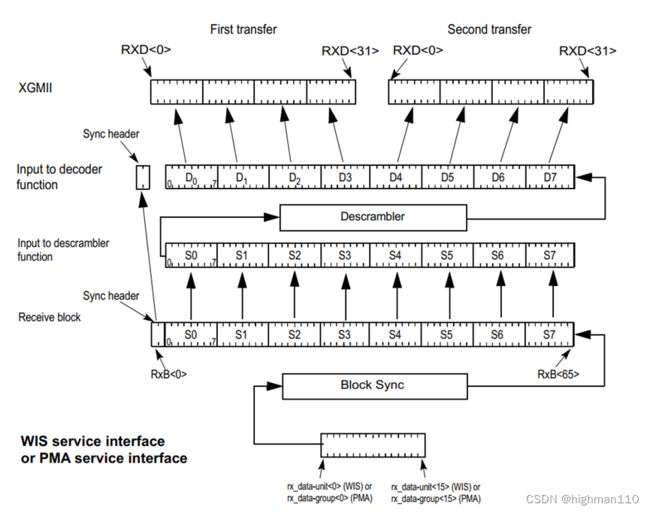

如下是PCS接收侧框图:数据从16位的并口从PMA传上来后,先通过侦测同步头获得block同步,恢复得到66bit的block,然后将除同步头外的64bit载荷进行解扰,得到64bit数据,再按顺序送给XGMII接口。

从上面的过程可以看到,所谓64/66b编码,其实从严格意义上来说并没有做什么编码动作,只是将数据扰码然后加上同步头。这与8/10b有很大区别,8/10b是从1024个代码组合中挑出了一部分来表示原来的256组代码组,挑选的代码组是可以达成直流平衡的目的,编码后的代码组和编码前的代码组没有严格的数学上联系,是为了直流平衡人为定义的编码对应关系。所以说在采用了8/10b编码的接口规范中,扰码器是个可选项,没有扰码也没有关系,而在64/66b中,扰码是必选项,只有通过扰码才能使信号尽量多的跳变,达成直流平衡和接收端时钟恢复的目的。

从上面的过程可以看到,所谓64/66b编码,其实从严格意义上来说并没有做什么编码动作,只是将数据扰码然后加上同步头。这与8/10b有很大区别,8/10b是从1024个代码组合中挑出了一部分来表示原来的256组代码组,挑选的代码组是可以达成直流平衡的目的,编码后的代码组和编码前的代码组没有严格的数学上联系,是为了直流平衡人为定义的编码对应关系。所以说在采用了8/10b编码的接口规范中,扰码器是个可选项,没有扰码也没有关系,而在64/66b中,扰码是必选项,只有通过扰码才能使信号尽量多的跳变,达成直流平衡和接收端时钟恢复的目的。

XGMII到USXGMII的映射

从以上64/66b PCS的编码过程可以看到,XGMII上的64b数据或控制信息将被编码形成66b的block。接下来看一下block的构成。

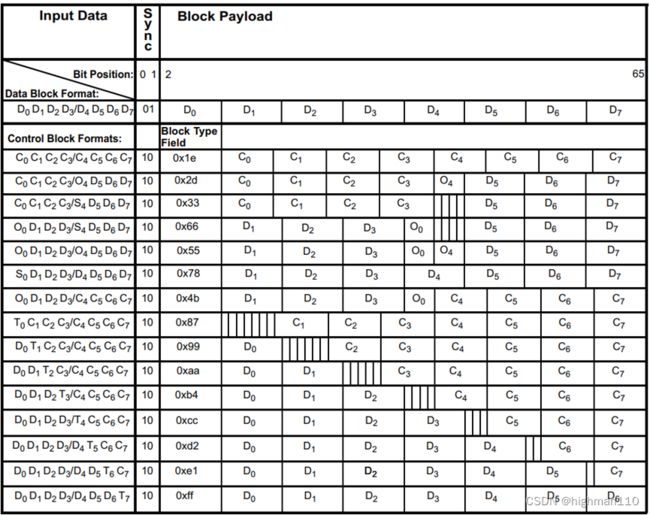

纯数据block就是同步头加八个数据载荷字符,这个没什么好说的,见下图第一行。

控制block以8位block类型字段开始,该字段指示block的剩余部分的格式,只要带有任意一个控制字符的block都叫控制block。对于包含“开始”(下图中的S,即对应XGMII的开始字符0xFB)或“终止”(下图中的T,即对应XGMII的开始字符0xFD)字符的控制block,这两个字符包含在block类型字段中。其他控制字符被编码在7位控制码C或4位O码(0xF)中。每个控制block包含八个字符。具体的block格式如下图所示:

在上表中可以看到,block分数据block和控制block,最左边一列是XGMII过来的输入数据,共8个字节,用8个字符表示,如D表示数据、C表示控制,就是前面说的XGMII上的数据或控制信号。当XGMII的TXC或RXC为0时,传输的是数据字符,当TXC或RXC为1时,传输的是控制字符。第二列是同步头,数据同步头是10,控制同步头是01。第三大列是载荷,数据载荷就是8个数据字符,控制载荷第一列是类型字段,剩下的控制载荷由控制字符或数据字符或Order set字符组成。图中的细长条空格是单bit字符,没有定义标签,发送端是填0发送,并在接收端忽略。

举几个控制block的例子,比如第2行,全是C码,可以理解为帧间隙,这里的C都是idle码型;再比如第4行,前面4个C表示帧间隙idle,后面跟着起始字符S,接下来是数据。

这里需要注意,每个字段的最低有效位对应的是block中本字段编号最低的位置,如第一个控制block的类型字段0x1e,对应的block bit 2到bit 9为,0111 1000,而不是0001 1110。发送的时候也是按0111 1000的顺序发送。

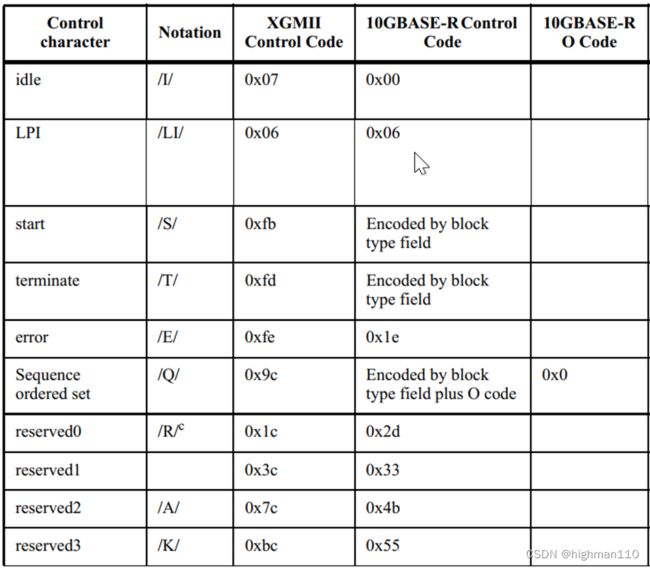

下面介绍控制block中的各类码型。XGMII和10GBASE-R PCS支持相同的控制字符集,这个相同指的是控制字符类型相同,具体的二进制值会有差异,两者是对应关系。从上面的表格可以看出,XGMII的控制字符都是8bit的(左边的64bit输入都是用8个字符表示),而10Gbase-R的控制字符有变化,C码为7bit,O码为4bit,D码仍为8bit。

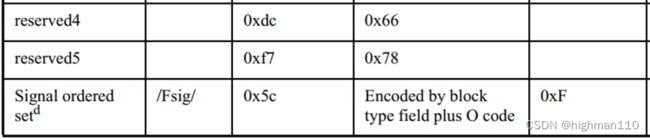

控制字符类型如下图所示:

UXSGMII上的block中的控制码型和上表中的10Gbase-R控制码是一样的,因为PCS是复用的,和XGMII的控制字是一个意思,这里再啰嗦一遍:

I码:当从XGMII收到idle控制字符时,PCS将发送I码,通过添加或删除I码可以用来实现PCS到PMA的速率适配(进PCS是XGMII接口,两组XGMII接口数据编码成66bit,而出口到PMA的接口是16bit,相当于出入数据接口宽度为16:33,所以需要进行速率适配)。I码以4个为一组的形式进行插入或删除,可以在I码或ordered set之后添加,不能在数据接收时添加,当删除I码时,T码之后的头4个字符不能删除。

LI码:低功耗请求。

S码:表示数据包的起始,此分割符仅在XGMII的lane0 bit[7:0]上有效,如果在其他bit上接收到起始字符,则表示接收错误。从上面的block格式表中可以看到,左边的XGMII输入,S字符只出现在第0个字节或第4个字节。编码后的S字符被隐藏在block类型字段中。

T码:表示数据包的结束,有数据包可以是任意长度,所以T码可以出现在XGMII接口的任意八位字节和块的任意字符上,同样,编码后的T字符被隐藏在block类型字段中。

Q码:表示序列有续集,有序集控制字符/O/表示有序集的开始,如上block格式图中的第7种控制block,输入/O/字符开头的序列有续集,被编码为类型字段+第4段4bit的/O/字符。关于这些个ordered sets在10Gbase-R中到底具体起什么作用,我在802.3-2018 clause 49.2中没有看到详细描述,只提到了PCS可以删除有续集来做时钟速率适配,这似乎与上面的I码功能重叠,我猜测是/O/+数个/I/构成一个序列有续集Q,规范里面目前还没看到在哪里有描述,这个规范里面的内容太多,大家有兴趣可以自动查阅。

其他的E码表示错误,A、K、R用与XAUI接口时表示空闲,这里不多提了。

另外这里有个疑问,既然XGMII的数据信号到串行接口上直接扰码就行了,为什么控制信号要搞这么多事情,不仅码组变换了,还分了这么多类型字段?我这边理解这和起始字符S、ordered sets Sequence的位置要求、控制报文的长度、帧间隙的长度等有关系,举个例子,起始字符S可以在lane0,也可以在lane4,如果在串行化的block里不用类型字段区分这两种情况,那在接收端就无法知道这个起始字符改对齐到lane0还是lane4。

带内配置和状态信号

带内控制和状态信号以IEEE 802.3 clause 46(XGMII)中定义的有序集进行传输。这里定义的有序集为3字节,802.3中XGMII定义了两个这样的消息——Local Fault(0x00、0x00和0x01)和Remote Fault(0x0、0x000和0x02)。如下图:

在USXGMII中,沿用了Local Fault和Remote Fault这两个ordered sets用来报告故障信息,另外还定义了新的有序集以支持以下功能:

1、自协商功能,支持在ASIC和PHY之间传送自协商信息;

2、数据包信息报文:能够发送数据包类型、子端口ID和扩展字段类型/扩展字段,这是可选功能。

自协商相关

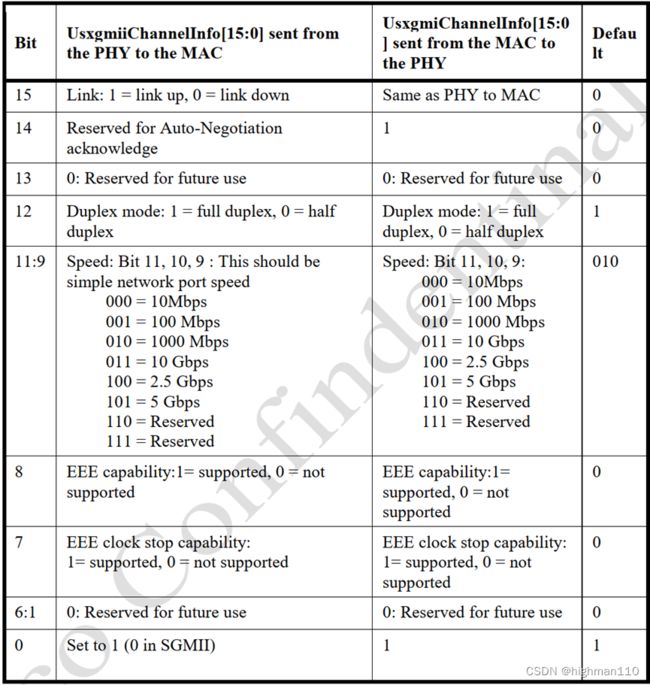

我们先看PHY芯片内部靠近线路侧的情况,从上面的框图中可以看到外部端口的自协商是和端口相关的PHY子层(图中蓝色小框)完成的,如果是标准GMII或XGMII到MAC,那协商结果将通过标准接口直接上报,如果是USXGMII到MAC,则必须先要通过MDIO给PHY芯片做一个USXGMII使能配置来选通USXGMII模式,USXGMII两端也是需要协商的,规范约定的serdes速率支持5G和10G,不协商怎么知道应该跑多快的速率,毕竟可以用来省功耗。USXGMII的自协商模块沿用的是802.3 clause 37的规范,协商配置信息有些许不同,毕竟速率能力就不一样。

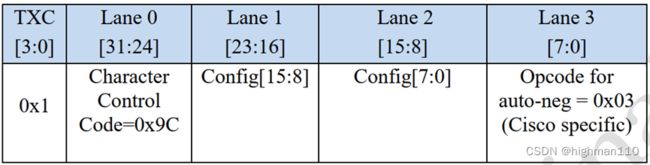

当使用USXGMII时,XGMII定义了如下ordered set来传输自协商的配置信息:

与SGMII一样,UsxgmiiChannelInfo使用1.6ms链路定时器。链路状态的任何变化都需要PHY重新发送UsxgmiiChannelInfo消息,直到接收到自动协商确认位设置为1,或者1.6ms链路定时器超时还没有收到自动协商确认位为1,也会重新发送UsxgmiiChannelInfo消息。

电气特性

USXGMII的电气特性要求与10Gbase-KR一致,见802.3 72.7章节和附录69B。USXGMII规范提出了如下要求:

1、IP供应商必须提供AMI模型并支持内部眼图(能够在RX采样锁存器处测量眼图)

2、IP供应商必须提供BER下的眼宽和眼高标准要求

3、使用NRZ编码

4、连接为点对点平衡差分对

5、100欧姆标称差分阻抗

6、每个差分对上为单向信号

7、嵌入时钟,接收器中需要CDR

8、链路的误码率应为10-15

9、驱动器和接收器之间需要交流耦合

如下是10Gbase-KR的发送接收电气特性:

发送特性:

接收特性:

好了,USXGMII的介绍就先到这里。本篇的内容有点细,一些码型、控制字符一般来说在工程上没必要扣这么细,毕竟这是规范,厂家基本都会按此实现,一般只需要了解其功能框架就可以帮助我们较好地理解一些应用常规的应用场景了。

好了,USXGMII的介绍就先到这里。本篇的内容有点细,一些码型、控制字符一般来说在工程上没必要扣这么细,毕竟这是规范,厂家基本都会按此实现,一般只需要了解其功能框架就可以帮助我们较好地理解一些应用常规的应用场景了。