用Zybo调试CY7C68013A核心板的Slave FIFO模式

用Zybo调试CY7C68013A核心板

- 简介

- CY7C68013A核心板

- CY7C68013程序设计

-

- 硬件连接

- 主要代码

- Zybo程序设计

- 心得

简介

最近在调试CY7C68013A核心板的Slave FIFO模式时,因为电路板的丝印bug,绕了一大圈。最终不但调试成功,也发现了用Zybo调试其它电路板的便利之处。在这里分享下调试过程和心得。

CY7C68013A核心板

淘宝购买的最便宜的核心板,有两个用户LED,硬件版本为HW-274。实物如下图:

根据原理图和实物细节照片,发现丝印SLWR和SLRD搞反了。也即丝印RDY0实际上是RDY1引脚,丝印RDY1实际上是RDY0引脚。具体如下图所示:

红圈处的引脚实际为RDY1/SLWR,但是丝印错误,搞成了RDY0。

蓝圈处的引脚实际为RDY0/SLRD。

最开始是用STM32作为主控,读写CY7C68013的FIFO。但是因为开始没有发现这个错误,就转而使用Zybo调试了。用Zybo的原因是因为它在调试时能够很方便地使用ILA IP进行逻辑分析。正因为这个错误让我认识到了Zybo的额外利用价值。

CY7C68013程序设计

硬件连接

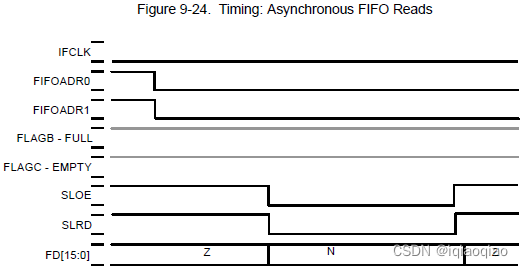

在调试CY7C68013的Slave FIFO模式时,为了简化硬件电路连接和控制端代码,采用了异步模式。根据EZ-USB的TRM文档,异步Slave FIFO读写硬件电路和时序为:

主要代码

CYPRESS提供了FX2LP的固件框架,使得固件开发只需修改TD_Init和TD_Poll(如果采用中断,那就修改中断函数)两个函数即可。针对CY7C68013 的固件程序,只需要修改bulkloop项目中的bulkloop.c文件里的TD_Init和TD_Poll函数。

void TD_Init(void) // Called once at startup

{

//设置8051的工作频率为48MHz

CPUCS = 0x12; // CLKSPD[1:0]=10, for 48MHz operation, output CLKOUT

SYNCDELAY;

//Slave使用内部48MHz的时钟

IFCONFIG = 0xEB; //Internal clock, 48 MHz, output IFCLK, Slave FIFO ASYNC mode

//IFCONFIG.3=ASYNC, 1=async, 0=sync

SYNCDELAY;

//配置FIFO标志输出,FLAG B配置为EP6 IN FIFO空标志

PINFLAGSAB = 0xE0; // FLAGB - EP6FF

SYNCDELAY;

//配置FIFO标志输出,FLAG C配置为EP2 OUT FIFO满标志

PINFLAGSCD = 0x08; // FLAGC - EP2EF

SYNCDELAY;

//PA7=FLAGD

PORTACFG = 0x00;

SYNCDELAY;

FIFOPINPOLAR = 0x00; // set all slave FIFO interface pins as active low

SYNCDELAY;

//将EP2断端点配置为BULK-OUT端点,使用4倍缓冲,512字节FIFO

EP2CFG = 0xA0; //out 512 bytes, 4x, bulk

SYNCDELAY;

//将EP6配置为BULK-OUT端点,

EP6CFG = 0xE0; // in 512 bytes, 4x, bulk

SYNCDELAY;

EP4CFG = 0x02; //clear valid bit

SYNCDELAY;

EP8CFG = 0x02; //clear valid bit

SYNCDELAY;

//复位FIFO

FIFORESET = 0x80; // activate NAK-ALL to avoid race conditions

SYNCDELAY; // see TRM section 15.14

FIFORESET = 0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET = 0x04; // reset, FIFO 4

SYNCDELAY; //

FIFORESET = 0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET = 0x08; // reset, FIFO 8

SYNCDELAY; //

FIFORESET = 0x00; // deactivate NAK-ALL

SYNCDELAY;

// handle the case where we were already in AUTO mode...

// ...for example: back to back firmware downloads... //

EP2FIFOCFG = 0x00; // AUTOOUT=0, WORDWIDE=0

// core needs to see AUTOOUT=0 to AUTOOUT=1 switch to arm endp's

SYNCDELAY; //

EP2FIFOCFG = 0x11; // AUTOOUT=1, WORDWIDE=1

SYNCDELAY; //

EP6FIFOCFG = 0x0D; // AUTOIN=1, ZEROLENIN=1, WORDWIDE=1

SYNCDELAY;

}

void TD_Poll( void )

{ // Called repeatedly while the device is idle

// ...nothing to do... slave fifo's are in AUTO mode...

}

Zybo程序设计

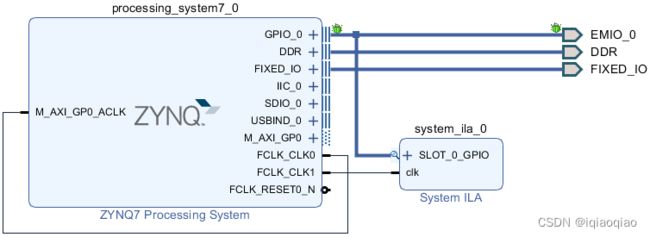

Zybo的BD设计如下:

EMIO为24位,ILA的深度为16K,FCLK_CLK1的频率为10MHz。生成bit文件后导出到SDK,SDK的Application中,添加如下main.c文件:

// main.c

#include "xgpiops.h"

#include "sleep.h"

#define ADDR1 54

#define ADDR0 55

#define SLOE 56

#define FLAGC 57

#define FLAGB 58

#define SLWR 59

#define SLRD 60

int main()

{

static XGpioPs psGpioInstancePtr;

XGpioPs_Config* GpioConfigPtr;

int xStatus;

//-- Init. EMIO

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

if(GpioConfigPtr == NULL)

return XST_FAILURE;

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr, GpioConfigPtr->BaseAddr);

if(XST_SUCCESS != xStatus)

print(" PS GPIO INIT FAILED \n\r");

//--config EMIO as output/input

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 62 ,0); //

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 63 ,0); //

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 64 ,0); //

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 65 ,0); //

XGpioPs_SetDirectionPin(&psGpioInstancePtr, ADDR0 ,1); // ADDR0

XGpioPs_SetDirectionPin(&psGpioInstancePtr, ADDR1 ,1); // ADDR1

XGpioPs_SetDirectionPin(&psGpioInstancePtr, SLOE ,1); // SLOE

XGpioPs_SetDirectionPin(&psGpioInstancePtr, SLWR ,1); // SLWR

XGpioPs_SetDirectionPin(&psGpioInstancePtr, FLAGB ,0); // FLAGB

XGpioPs_SetDirectionPin(&psGpioInstancePtr, FLAGC ,0); // FLAGC

XGpioPs_SetDirectionPin(&psGpioInstancePtr, SLRD ,1); // SLRD

//enable EMIO output

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, ADDR1,1);

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, ADDR0,1);

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, SLOE ,1);

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, SLWR ,1);

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, SLRD ,1);

// XGpioPs_WritePin(&psGpioInstancePtr, ADDR1, 0);

// XGpioPs_WritePin(&psGpioInstancePtr, ADDR0, 0);

// XGpioPs_WritePin(&psGpioInstancePtr, SLOE, 0);

//

XGpioPs_WritePin(&psGpioInstancePtr, ADDR1, 1);

XGpioPs_WritePin(&psGpioInstancePtr, ADDR0, 0);

XGpioPs_WritePin(&psGpioInstancePtr, SLOE, 1);

while(1)

{

// if(XGpioPs_ReadPin(&psGpioInstancePtr, FLAGC)) // Not Empty

// {

// XGpioPs_WritePin(&psGpioInstancePtr, SLRD, 0);

// usleep(1);

// XGpioPs_WritePin(&psGpioInstancePtr, SLRD, 1);

// usleep(1);

// }

// else

// {

// XGpioPs_WritePin(&psGpioInstancePtr, SLRD, 1);

// }

if(XGpioPs_ReadPin(&psGpioInstancePtr, FLAGB)) // Not Full

{

XGpioPs_WritePin(&psGpioInstancePtr, SLWR, 0);

usleep(1);

XGpioPs_WritePin(&psGpioInstancePtr, SLWR, 1);

usleep(1);

}

else

{

XGpioPs_WritePin(&psGpioInstancePtr, SLWR, 1);

}

}

return 0;

}

在CY7C68013下载完程序后,启动Zybo,SDK进入Debug模式。在Vivado界面,点击左侧的PROGRAM AND DEBUG。因为ILA的时钟频率为10MHz,那么JTAG频率必须低于4MHz,否则会出错。

右键点击Refresh Server重置JTAG连接,然后设置JTAG频率,如下图设置为3MHz。

或者在Tcl中运行:

refresh_hw_server {localhost:3121}

set_property PARAM.FREQUENCY 3000000 [get_hw_targets localhost:3121/xilinx_tcf/Digilent/210279572355A]

在测试Zybo读CY7C68013的Slave FIFO时,hw_ila_1的设置和捕获的波形如下图

其中,0~6的引脚分别连接CY7C68013的ADDR0、ADDR1、SLOE、SLWR、FLAGB、FLAGC和SLRD。

心得

- 使用了两块电路板才调试CY7C68013成功,最后才发现是丝印的问题,这告诉我 有时候还真不是自己的错 。

- Zybo的PS+PL用起来方便,不论什么时序,PS和PL,总有一款适合你 。