SV中的随机化约束

1.多个变量相互依赖,如何进行随机化?

采用solve before

(1)constraint c_valid_write_data {

solve access_type before data;

solve burst_length before data;

(access_type == TVIP_AXI_WRITE_ACCESS) -> data.size() == burst_length;

(access_type == TVIP_AXI_READ_ACCESS ) -> data.size() == 0;

foreach (data[i]) {

(data[i] >> this.configuration.data_width) == 0;

}

}

(2) constraint c_write_data_delay {

solve access_type, burst_length before write_data_delay;

if (access_type == TVIP_AXI_WRITE_ACCESS) {

write_data_delay.size() == burst_length;

}

else {

write_data_delay.size() == 0;

}

foreach (write_data_delay[i]) {

`tvip_delay_constraint(write_data_delay[i], this.configuration.write_data_delay)

}

}分步求解1:

有三个数组,每个元素的取值范围是1-9,三个数组的和是100,三个数组中5的个数不能超过10个。

拆分,需要随机的内容包含:(1)变量取值范围(2)变量和的范围(3)变量个数(4)数组中5的个数不超过10个。

(1)~(3)都可以设定一个变量,通过变量来约束

(4)两种解决方案,第一个就是随机的过程中不随机5,随机完了之后再去插入5;通过调整权重,然后进行永久循环随机,通过find_index with找到5,并且总的数组含量大于5的情况下在退出随机,否则就一直进行随机

参考博客:[SV]Constraint 遇到的问题_随机约束 父类和子类冲突_lbt_dvshare的博客-CSDN博客

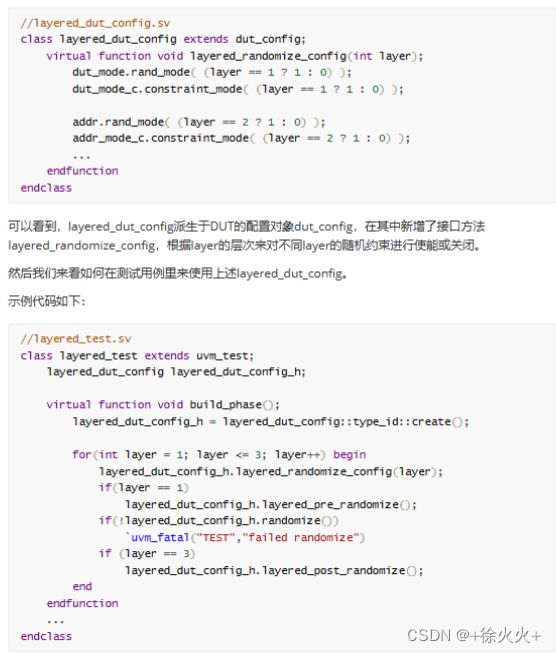

分步求解2:

分三层进行随机(具体分几层由变量和变量之间的层次关系决定)

核心在于不借助solve before的方式进行随机

class packet;

rand bit [7:0] addr0;

rand bit [7:0] addr1;

rand bit [7:0] addr2;

bit[1:0] layer;

function void pre_randomize();

if(layer == 'd0)begin

addr1.rand_mode(0);

addr2.rand_mode(0);

end

else if(layer == 'd1)begin

addr0.rand_mode(0);

addr2.rand_mode(0);

end

else if(layer == 'd2)begin

addr0.rand_mode(0);

addr1.rand_mode(0);

end

endfunction

endclass

不仅仅可以使用rand mode也可以使用constrain mode

有个问题,每次随机的时候,上一个变量的rand mode关闭了,还需要重新打开吗???

代码踩坑:

1

rand a ;

rand b ;

rand c ;

`uvm_do_on_with{

a = b + c ;

a = b ;

a = {b,c} ;

}2.

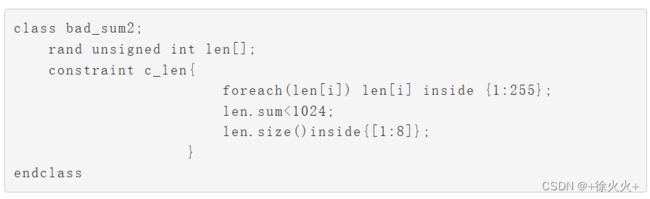

(1)针对有符号变量相加过程中随机到负值->改为无符号变量(int是有符号变量)

(2)针对无符号变量相加过程中随机出现溢出的情况->sum值位宽大一位

注意,再比如a+b == 10的约束中,10没有明确指定位宽的化此时会采用默认的32bit位宽。所以需要改为a+b == 33'b10的约束形式。

(3)数组随机,在使用sum函数的时候一定要注意,为了避免上面两种情况,一定要县约束每个变量大致范围,在使用sum函数进行约束

参考链接:

SV学习笔记—变量及数组随机化约束常犯的错误-爱代码爱编程 (icode.best)

这里有个问题,如果这样做,这三个随机不是并行执行的吗,不会出现问题吗??

SV学习笔记—变量及数组随机化约束常犯的错误_Verification_White的博客-CSDN博客

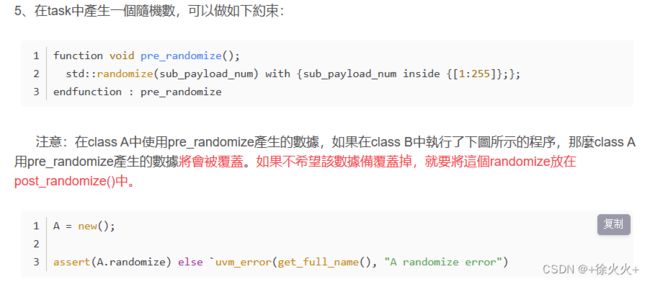

4.使用uvm_do_on_with的时候也会调用pre randomize或者post radomize函数吗???

5.在uvm_do_on_with的时候如果使用同名变量进行约束随机的时候 ,需要考虑域的问题,建议使用local解决;

`uvm_do_with中constraint不生效的原因及解决方案_@constraint不生效的场景_城外南风起的博客-CSDN博客

这里引出一个问题,this和local,日后详细补。

6.约束冲突时:

(1)后来的约束覆盖前者约束(2)子类约束覆盖父类约束(3)外部约束覆盖内部约束

(4)强约束覆盖soft约束(5)如果两个soft 约束冲突,按上述3条处理且随机是可以成功

7.使用 $urandom_range系统函数进行随机的时候,发现产生的数值与预期不符。原因可能是urandom_range随机范围上限是32 bit,上限数值max位宽很大的话只取低32 bit

8.

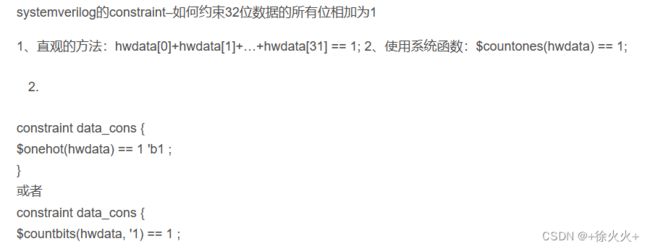

8.如何约束一个多位宽数据只有一个位宽数据为1:

9.当修饰符为randc时,不要使用sovle…before…,因为randc默认最先计算,使用sovle…before…可能会带来未知错误。

9.当修饰符为randc时,不要使用sovle…before…,因为randc默认最先计算,使用sovle…before…可能会带来未知错误。

10.子类会把父类中同名的约束覆盖。

sv 继承的同名constraint会覆盖_BlackDogv的博客-CSDN博客