硬件总线基础06:PCIe总线基础(1)

说在开头:关于我的世界(2)

我们理性所能把握到的知识(科学)受到了限制,那么通过人的感官所感受到的经验知识,能否把握到事物的本质呢?我们无法从感性上理解原子(我们听到电子绕原子核运动,就想到了地球绕太阳运行,但是如量子论中所描述,电子绕原子核的运动我们只能“看到”它在某一位置出现的概率,而不能看到其整个运行轨迹),而且对大至星系级别的也无法想象(举个栗子:银河系有2000亿~4000亿颗恒星,10万光年的空间跨度,在我脑子里就只有这组数字,并没有形象概念了),更不用说可观测宇宙还有几千亿个“银河系”。其它还有我们通过间接手段无法发现的暗物质和暗能量,就不用说去理解它了。

那么,就算我们能够感知到东西,就一定能对它有真正地认知了么?例如电场。电子工程师对电场肯定都不陌生,上过高中物理的同学应该对电场有印象,电场是什么样的(在我的印象中就是:手扶静电球后头发炸毛)?大家会说电场不就是如下图这样子的么。

但电场真的是这样么?这只是便于我们理解与记忆的想象示意图,我们无法具象化电磁场因为它看不见摸不着,从来没有人见过这东西,正如我们无法理解暗物质、暗能量,高维空间一样。举个栗子:假如有个岛国上的土著人从来没有喝过茶,我们跟他描述世界上存在这么一个东西:茶;并详述茶的物质成分和各种分子结构,他听了之后说:哦,我知道这个茶了。但是如果有一天他真正的体验到茶:用眼睛看到,用手触摸到,用鼻子闻到,并喝到了一杯热茶(感官体验到了茶)。那么对于我们来说,茶是本质是什么?是那些组成它的分子结构,还是实实在在喝到的那一杯茶?我们对世界的认知并非完全是理性和逻辑推理带给我们的结论,而更多的是个人对世界的感性体验。

那我们再一次将这个讨论范围缩小:只关注我们感官所感受到的世界。那就有两个问题了:

1. 我们所有的人都能感受到同样的一个世界么?如果不同谁的是真实的?

大部分人能看到的颜色是彩虹色的:红橙黄绿青蓝紫;但是并非所有人都能看到这7种颜色,一般我们认为色盲或色弱的人是由于其眼睛功能的缺陷,因为人类的大多数决定了话语权。但是如果世界上有一半的人只能分辨黑白,那么该如何界定谁看到的才算是真实的?

就算同属于“正常人”,我们每个人的感知多少会有些差别,你我所感受到的并非相同,甚至是完全相反的。记得多年前在网上流传了一条蓝黑或白金色的裙子(如下左图所示),各大阵营吵的不可开交,有人说看到白金(比如我),有人笃定是蓝黑,还有人说有时看到白金有时看到蓝黑,那到底是谁错了呢?或则谁都没有错,因为我们的感知本来就是不一样的。再深入想一下:你眼中的天空颜色同别人眼中是一样的么?还是说别人跟你说天空是“蓝色”的,你就认为那个颜色就是“蓝色”?我们无法证明自己看到的蓝色是否跟其它人看到的是一样的。

2. 对我个人来说,是否能根据眼睛自身的功能真实地反映世界呢?

眼睛是否就像是一个照相机,将图像传递给大脑,虽然每个人的“照相机”有所差别,但是大脑看到的照片是眼睛对真实世界的拷贝。然而事实上正好相反,是大脑决定了眼睛能看到什么(心灵决定感官能感知到的东西)。如上右图中A和B区域中的颜色是一样的,只是我们的大脑自动对图片进行了处理。记得有一天中午跟同事在园区逛,突然发现有对面大楼的墙上写了一句硕大的标语,我很惊讶的问:这个标语啥时候写上去的?他的回答说:几年前来公司的时候就已经有了啊。这不是我的眼睛没有看到,而是我的脑子“不想”看到它(有一个有意思的问题:镜子和照片(无ps)中的自己,哪个更真实呢?)。

每个人对外部世界的感知(看到、听到、感受到的),不仅仅是个人感觉器官的作用,更重要的还受到了母语本身、社会时代背景、教育、家庭背景、性格、情绪等等影响。我们的“内在世界”决定了我们眼睛所看到的,正如电影中的那只鸡:说一位导演进行了一次试验,向一个从未接触过现代文明的原始部落人群放一部关于现代文明纪录片,里面展示了现代文明的成果:高楼大厦,飞机、火车以及各种高科技产品。导演本来以为能看到那群土著对现代文明震惊的表情,结果影片放映完成以后,这群观众正热情洋溢的在谈论一只鸡。导演就纳闷了,他亲手剪辑并看过无数遍的电影,里面并没有什么鸡的画面啊。于是他只好放慢影片速度,一格一格回放检查,发现这只鸡只出现在了8格画面中(一帧24格画面,0.3秒),而且竟然被所有的部落人捕捉到了!与世隔绝的原始人部落人只能认识他们世界内有的东西:那只“鸡”。 对于原始部落的人来说,再丰富的画面场景对他们来说都是空气,所以能排除一切“杂物”,而看到那只一闪而过的鸡。

那对于我们自己来说,谁的世界中不存在着这只“鸡”呢?

一,PCIe总线概述

PCI总线一经推出取得了巨大的成功,有“富二代”的因素,但不可否认的是其自身的“打铁”技术够硬。一晃过了十年,x86系列处理器从80386/486时代到了奔腾时代末期,PCI总线虽然也在不断地升级,位宽和频率从最初的32bit/33MHz扩展到了64bit/66MHz,但它疲态尽显,已经不能满足处理器日益发展的需求。

1. 按照64bit/66MHz计算,理论上来说PCI总线的最大传输带宽是532MB,但它是共享总线,PCI总线树下的所有PCI设备必须共享PCI 总线带宽;

——另外,PCI总线协议也有开销,所以PCI总线实际数据带宽远小于最大传输带宽。

2. PCI总线提升位宽和总线频率,同时也大大地提高了设计成本:

1,支持大带宽PCI总线芯片的管脚数量大增,封装面积增大,芯片制造价格更高;

2,PCB走线数量更多,占用PCB面积更大、层数更多,PCB价格更高。

3. PCI总线频率的提升也带来了一系列信号完整性的问题,同时也影响到了PCI总线的负载能力;33MHz的PCI总线最大可驱动10个负载,而66MHz的PCI总线最多只能驱动4个负载,到了133MHz(PCI-X总线)只能驱动2个负载;

4. 一些特殊需求的PCI设备:实时数据采集卡,音频/视频卡等,对PCI总线提供连续带宽的要求较高,但PCI总线上的设备只能轮流占用PCI总线,当其它设备长期占用时,将会被影响到传输质量。

PCI总线有如此多的限制,它也尝试这在这条老路上进行突破:PCI-X总线;总线带宽也达到4GB/s,但终归逆改不了历史的洪流,所以PCI-X最终也只是昙花一现,但并不是说PCI-X总线是做了无用功,其在PCI总线上的一些改进和创新在PCIe总线上被保留了下来。

PCIe总线应运而生了,它作为一种串行总线,与早期的串行总线(举个栗子: InfiniBand(IB) 或Fiber Channel(FC))有许多的共同点,但是它最重要的一点是:在软件层面上完全保持了对 PCI 的前向兼容。那么PCIe凭什么能替代掉PCI呢?如下图所示,一对PCIe差分线(x1,4根信号线)在不同PCIe版本下支持的带宽,而且这个带宽是独占而非共享的。如果需要更高的带宽,可以支持x2、x4、x8、x16、x32模式,PCIe 1.0版本最大可支持8GB/s带宽。虽然PCIe相对于PCI总线来说,其协议开销相对来说更大一些,数据时延也更大一些。

——PCI总线通过独立管脚的带外管理,现在都通过PCIe链路的带内进行,而且PCIe协议本身更加复杂,所以PCIe开销会更大。

——PCIe是串行总线,需要在发送端经过并串转换,且在接收端串并转换后才能处理,所以这一过程的延时会相对更大。

1,PCIe总线硬件基础

如其它串行高速总线一样,PCIe 使用双向连接的方式,可以在同一时间进行信息的收发操作;这种传输模型被称为双单工连接,因为每个接口都有一个单工发送路径和一个单工接收路径;如下图所示。因为数据流可以同时进行双向传输,因此在技术层面上来说两个设备间的通信其实是全双工的。

设备之间信号的传输路径称为:Link(链路),它由一个或以上的收发对组成;这样的一对接收和发送被称为:Lane(通道);协议规范允许一条Link可以有 1、2、4、8、12、16 或 32 个Lane,所以一条Link由多条Lane组成,链路内Lane的数量称为链路宽度;通常用 x1、x2、x4、x8、x16 以及 x32 来进行表示;那么实际设计中到底要使用多少通道呢?思路其实很简单:使用更多的通道可以增加带宽,但是也会增加成本、增加空间占用以及增加功耗。

1.1 串行传输模式

我们知道并行总线正是由于有很多数据线,所以其传输带宽是总线位宽的倍数;那么如果我们用串行的传输方式,那么单根信号线上的数据速率要比并行总线高的多,才能达到相同的传输带宽。这看起来非常困难,但这并不难(具体请参考《电平设计基础》和《从公交车到总线概念》章节相关内容),采用合适的电平以及编码方式,现在串行数据传输速率已经高达56Gbps以上。

我们知道并行总线的性能被一些问题所限制:并行总线使用公共时钟;信号在一个时钟沿被输出,然后在下一个时钟沿被接收方接收;

1. 第一个问题来自于信号从发送端传输到接收端所花费的时间(传输延时),传输延时必须小于一个时钟周期,否则将会出问题,这使得难以通过继续减小时钟周期来提升速度;

——若需要继续减小时钟周期,为了让信号传输延时依然小于时钟周期,需要更短的布线并减少负载的设备数量,但是最终会到达极限并且实现起来越来越困难。

2. 造成并行模型性能受限的因素是使用公共时钟时,时钟到达发送方和接收方的时刻不一致,这称为时钟偏斜。

——电路板设计人员尽力去减小时钟偏斜的值,因为时钟偏斜将会降低信号传输时序预算(建立/保持时间),但是这种偏斜永远无法彻底消除。

3. 信号偏斜:指的是多比特位宽数据的各个位到达接收端的时刻存在差异;并行数据的所有的比特都到达且稳定之前都不能被接收端采样,要求必须去等待最慢的那一比特。

然而PCIe的串行传输方法是如何处理这些问题的呢?

1. 传输延时在PCIe总线上不是个问题,因为用于指示接收端锁存数据的时钟现在已经被内置入数据流中,不在需要额外传输线来传输参考时钟;

——内置在数据流中的时钟是与数据一起到达接收端的。

2. 时钟偏斜的问题将不再存在,这还是因为时钟被内置入数据流中,接收方通过恢复出数据流中的时钟来进行数据采样,自然不存在时钟偏斜的问题;

3. 信号偏斜的问题在一个通道内被消除了,因为一个通道一次只传输 1 比特数据;在多通道设计中,虽然也存在信号偏斜的问题,但是接收端自动对其进行了纠正,很大程度上补偿了偏斜。

PCIe单条Lane已经可以支持较高的带宽,不同版本的PCIe链路支持的速率如下表格所示。我们知道知道PCIe 1.0 比特率是2.5GT/s而PCIe 2.0的比特率是5GT/s,它们采用的是经典的8b/10b编码(具体为什么要物理编码?且编码的具体内容,参考《从公交车到总线概念》相关章节),实现了Gen2相比于Gen1的总线速率翻倍;PCIe 3.0为了实现数据速率的再次翻倍,将频率提升到了8GT/s(频率相对于PCIe2.0并未翻倍),而采用了新的编码方式:128b/130b。

对于上述表格中的 PCIe 带宽大小,可以参照如下的计算方法:

1. PCIe 1.0 带宽 =(2.5Gb/s x 2 directions)/ 10bits per symbol = 0.5GB/s;

2. PCIe 2.0 带宽 =(5.0Gb/s x 2 directions)/ 10bits per symbol = 1.0GB/s;

——采用8b/10b编码,所以除以10bit;即,要传输8bit有效数据,实际需传输10bit。

3. Gen3 PCIe 带宽 =(8.0Gb/s x 2 directions)/ 8bits per byte = 2.0GB/s。

——Gen3 速率的计算中除以的是 8bits 而不再是 10bits 了,这是因为 Gen3 中不再使用 8b/10b 编码方式,而是 128b/130b 编码方式;这种编码方式每 128位 引入 2 比特开销,这个开销非常小以至于我们暂且可以将它在我们的计算中忽略。

1.2 PCIe 差分信号

PCIe的每个通道都使用差分信号进行传输,其每次传输一个信号时同时发送正、负两个信号(D+ 和 D-:信号幅度相同、相位相反),如下图所示。差分信号相对于单端信号而言,在高速传输上有两个明显的优点:1,提高了噪声容限(共模噪声);2,并降低了信号电压。

另外,PCIe 链路不再像 PCI 一样使用公共时钟,它使用了一个源同步模型,这意味着需要由发送端给接收端提供一个时钟来用于对输入数据进行锁存采样。对于 PCIe 物理链路来说,并没有输出时钟信号,而是将时钟通过 8b/10b 编码来嵌入数据流中,然后接收端将会从数据流中恢复出这个时钟,并用于对输入数据的锁存。这一过程听起来非常神秘,但是其实很简单。如下图所示在接收端中的PLL 电路(Phase-Locked Loop 锁相环)将输入的比特流作为参考时钟,并将其时序或者相位与一个输出时钟相比较,这个输出时钟是 PLL 按照指定频率产生的时钟。

——PLL 自身会产生一个指定频率的输出时钟,然后用比特流作为的参考时钟与自身产生的输出时钟相比较;基于比较的结果,PLL 将会升高或者降低输出时钟的频率,直到所比较的双方频率相互匹配,此时可以称 PLL 已锁定,且输出时钟(恢复时钟)的频率已经精确地与发送数据的时钟相匹配。PLL 将会不断地调整恢复时钟,快速补偿修正由温度、电压因素对发送端时钟频率造成的影响。

关于时钟恢复,需要注意的是:PLL 需要输入端的信号跳变来完成相位比较。如果很长一段时间数据都没有任何跳变,那么 PLL 的恢复时钟可能会偏离正确的时钟频率。为了避免这种问题,8b/10b 编码中的设计目标之一就是要确保比特流中连续的 1 或者 0 的数量不能超过 5 个(具体8b/10b编码原理参考《从公交车到总线概念》相关章节)。

一旦线路时钟被恢复出来,就可以使用它来锁存输入数据流的比特,并将锁存到的结果给到解串器。那这个恢复时钟能否作为接收端的所有逻辑所使用的工作时钟呢?胖友们可以思考一下。

1.3 PCIe 其它信号

PCIe使用了两种电源信号供电:Vcc和Vaux;其中Vcc是主电源,PCIe设备的主要模块使用该电源供电;而与电源管理相关的逻辑模块使用Vaux供电,这些模块的寄存器内容就算在Vcc被移除的情况下也不会发生改变。PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间,PCIe设备可以在Vcc重新供电后快速恢复到正常工作状态。除此之外,PCIe总线还使用了很多辅助信号:

1. PERST#:全局复位信号,由处理器系统提供;处理器系统需要提供PCIe插槽和PCIe设备该复位信号,PCIe设备使用该信号复位内部逻辑;

——PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset与PERST#信号相关。

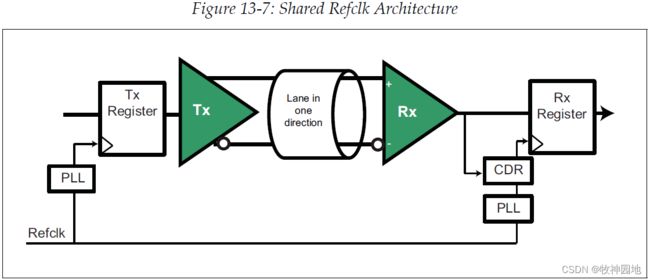

2. REFCLK+/-:PCIe设备需要使用参考时钟,其时钟频率为100MHz;处理器系统需要为每一个PCIe设备(包括PCIe插槽、MCH以及Switch)提供该参考时钟,该时钟可以是同源(如下图),也可以使用独立的时钟源;

——在PCIe设备配置空间的Link Control Register中的“Common Clock Configuration”位,当该位为1时表示该设备与PCIe链路的对端设备使用“同相位”参考时钟;如果该位为0,表示该设备与PCIe链路的对端设备使用“异步”参考时钟。

3. WAKE#:主要用于节能要求非常高的场景(举个栗子:电池供电),PCIe总线专门提供了这么一个边带管理信号,用于唤醒PCIe设备,使用该信号时必须使用辅助电源Vaux供电,当然也可以不使用该信号;WAKE#信号可以直接连接处理器系统也可以通过Switch传输;

——WAKE#信号是OD门输出信号,处理器系统可以将所有设备的WAKE#信号线与后接入系统的电源控制器(PME);当WAKE#信号拉低时,它将一直保持,直到PME_Status位被软件清除。

4. SMCLK/SMDAT:X86处理器的SMBus总线;预留在PCIe插槽上,用于设备管理通道。

2,PCIe总线拓扑结构

PCIe 链路不像 PCI 总线的共享总线,而是点对点的连接的;由于一条链路只能连接两个接口,因此需要一种扩展连接的方法来构建一个系统,如果直接将所有设备都采用直接的两两相连,那么会使得整个系统十分复杂,需要在 PCIe 中通过交换机(PCIe Switch)和桥接来实现,这两者可以灵活的构建系统拓扑。如下图所示为典型PCIe总线拓扑结构,主要由RC(Root Complex),PCIe Switch(或PCIe Bridge)和EP(End Point)组成。

1. RC:Root Complex(根组件),CPU 与 PCIe 总线之间的接口可能包含一系列的组件(处理器接口,DRAM 接口等,甚至是包含多个芯片),将这些组件合起来称这一组的组件为根组件(Root Complex);RC 自身的内部可以非常复杂,但是它通常会实现一个内部总线结构以及一些桥接结构,以便将拓扑扇出到几个端口;

——RC 的内部总线将被配置软件视作 PCI 总线 0,且 RC 上这几个 PCIe 端口将被视作是 PCI-to-PCI 桥,这种内部结构其实并不是一个实际的 PCI 总线,但是它在软件中看起来就是这种结构。

——RC 存在于 PCI 树状拓扑的“根部”,代表 CPU 与系统的其余部分通信;但PCIe 协议规范并没有对 RC 进行严格定义,而是给出了一个 RC 必需功能与可选功能的列表;所以从广义上说,根组件可以被理解为系统 CPU 与 PCIe 拓扑之间的接口,这个 PCIe 端口即是 RC,在配置空间中被标记为“根端口”。

——不同处理器的RC设计并不相同,只有x86才存在PCIe总线规范定义的“标准RC”,而其它很多处理器并不存在真正意义上的RC,而只是PCIe总线控制器。

——RC与HOST主桥并不相同,RC除了完成地址空间的转换之外,还需要完成物理信号的转换(举个栗子:FSB信号协议与PCIe总线的电气特性不兼容,总线事务也不同,必须进行信号协议和总线事务的转换)。

2. PCIe Switch,提供了扇出以及聚合能力:使得单个 PCIe 端口上可以连接更多的设备,它作为数据包路由器的角色,可以根据所给数据包的地址或者其他路由信息来识别这个数据包要走哪条路径;

1, 一个标准的PCIe Switch有一个上游端口和多个下游端口:上游端口与RC或则其它Switch的下游端口相连;下游端口可以与EP或其它Switch的上游端口相连;

2,PCIe总线规范支持一种特殊的连接方式:Crosslink;使用这种方式时Switch的下游端口可以与其它Switch的下游端口直接连接,或则两个Switch的上游端口相互连接;

3,从软件的角度来看,PCIe Switch的内部由多个PCI-to-PCI桥组成,每一个上游和下游端口都对应一个虚拟PCI桥;即PCIe Switch中有多少个端口,其内部就有多少个虚拟PCI桥以及对应的配置空间;

4,PCIe Switch需要处理PCIe总线传输过程中的QoS问题,需要区别对待优先权不同的数据报文,保证优先级高的通道/报文获得额定的数据带宽。

(1)采用虚拟通道(VC)技术,每一条链路最多可支持8个独立的VC,每个VC设置独立的缓冲,用来接收和发送数据报文;

——VC0~VC7,其中VC7优先级最高,VC0优先级最低。

(2)这些数据报文中设定TC(Traffic Class)标签,TC有3bit组成(8类),这8类数据报文可以根据需要选择不同的VC进行传递;

(3)TC和VC紧密连接,它们之间是多对一的关系。

——一个VC可以传递不同TC的数据报文,而相同TC的数据报文只能在指定的VC传递;许多处理器只支持一个VC。

3. PCIe Bridge:提供了一个通往其他总线的接口(举个栗子: PCI 或PCI-X,甚至是其他的 PCIe 总线);下图所示的桥被称为“前向桥”,它使得一个旧的 PCI 或者 PCI-X 板卡可以插入一个新系统中(PCIe 系统);而与前向桥相反类型的桥称为“反向桥”,它使得新的PCIe 板卡可以插入到旧的 PCI 系统中。现在使用PCI总线的场景应该已经不多,不做扩展分析。

4. EP:EndPoint(端点)是 PCIe 拓扑中的既不是交换机也不是桥的设备,它们可以作为总线上事务的发起者也可以作为事务的完成者;端点存在于树状拓扑的分支的底部,仅实现一个上行端口(Upstream Port,与 RC 的连接方向),这里的上行指的是拓扑结构的向上,表示端点已经是树的分支的端点,不再产生下级分支。相比之下,一个交换机可以有几个下行端口(Downstream Port);PCIe端点可以分为两类:

1,“传统 PCIe 端点”:用于老式总线(例如 PCI-X)的设备,如今拥有了可供它们使用的 PCIe 接口,这种 PCIe 接口将在配置寄存器中将自身标识为“传统 PCIe 端点”;

——它们使用了在 PCIe 设计中被禁止的东西,举个栗子: IO 空间、支持 IO 事务以及支持锁定请求。

2,“原生 PCIe 端点”:从一开始就被设计用来在 PCIe 系统中使用的,这区别于在旧的 PCI 设备上添加 PCIe 接口。原生 PCIe 端点设备是内存映射设备。

3,PCIe设备配置空间

PCIe总线保持对PCI总线软件兼容性的方法是:保持端点和桥的配置首部(Header)与 PCI 一致。如下图所示,PCIe设备兼容了PCI设备的64 Byte基本配置空间:0x00~0x3F,该64 Byte是所有PCI/PCIe设备必须支持的;此外PCI/PCI-X和PCIe设备还扩展了0x40~0xFF配置空间(192 Byte),主要存放MSI或MSI-X中断机制和电源相关的Capability结构。

PCIe设备还支持0x100~0xFFF段扩展配置空间,PCIe设备使用扩展配置空间最大为4KB,在该扩展配置空间中,存放PCIe设备所独有的一些Capability结构,而且PCI设备不能使用这段空间。在x86处理器中,使用常规的CONFIG_ADDRESS寄存器与CONFIG_DATA寄存器来访问PCIe配置空间:0x00~0xFF,而使用ECAM方式访问0x100~0xFFF这段空间。

PCIe总线规范要求设备必须支持Capabilities结构,包括与电源管理相关、PCIe总线相关的结构、与中断请求相关的Capability结构、PCIe Capability结构和PCIe扩展的(Extended)Capability结构:

1. Capabilities Pointer寄存器:存放Capabilities结构链表的头指针;

——每个PCIe设备中有多个Capability结构,这些寄存器组成一个链表。

2. ID号:不同Capability结构有唯一的ID号;

3. 指针:指向下一个Capability结构,从而构成一个单向链表结构,该链表的最后一个Capability结构的指针为0。

3.1 PCIe Power Management Capability结构

PCIe总线使用的软件电源管理机制需使用Power Management Capability结构,该结构由PCIe总线的电源管理相关寄存器组成:PMCR(Power Management Capabilities Register)和PMCSR(Power Management Control and Status Register);具体结构如下图所示。

PCMR寄存器由16bit组成,其中所有的bit和字段都是只读的,其主要目的是记录当前PCIe设备的物理属性,系统软件需要从PCMR寄存器中获得当前PCIe设备的信息后,各对PCMSR寄存器进行修改;寄存器定义如下图所示。

1. Version字段:记录Power Management Capability结构的版本号;

2. PME Clcok位:PCIe总线不使用,只用于PCI总线中当PME#信号需要使用PCI Clock时置位1;

3. RsvdP字段:系统保留字段;

4. DSI(Device Specific Initialization):某些PCIe设备需要重新配置运行在与上电时工作不同的模式,此时该设备需要使用该bit位表示,该设备可以使用自定义的电源工作方式;

5. AUX(Auxiliary Device):表示PCIe设备需要使用辅助电源Vaux的电流强度;最大值为375mA,最小值为0;

6. D2和D1位,D2位表示PCIe设备支持D2状态,D1位表示支持D1状态;

——PCI PM机制规定PCIe设备科支持4中状态(D0~D3):PCIe设备D0状态时功耗最高,D3状态时最低;多参数设备仅支持D0和D3状态,而D1和D2可选。

7. PME Support:存放PCIe设备支持的电源状态;

1,Bit 27为1时:表示PCIe设备处于D0状态时,可以发送PME消息;

2,Bit 28为1时:表示PCIe设备处于D1状态时,可以发送PME消息;

3,Bit 29为1时:表示PCIe设备处于D2状态时,可以发送PME消息;

4,Bit 30为1时:表示PCIe设备处于D3状态时,可以发送PME消息;

5,Bit 31为1时:表示PCIe设备处于D3cold状态时,可以发送PME消息;

——关于D状态(D0~D3)和L状态(L0~L3),后续章节会详细介绍。

系统软件通过PMCSR寄存器,完成PCIe设备状态的迁移,其寄存器结构如下图所示。

8. Power State(读写):记录PCIe设备所处的状态,0xb00对应D0,0xb01对应D1,0xb10对应D2,0xb11对应D3;系统软件改变该字段用于改变PCIe设备的电源状态;

9. No_Soft_Reset(只读):如果该位为1,PCIe设备从D3cold状态迁移到D0装填时,并不需要进行内部复位操作,PCIe相关寄存器由PCIe设备自己保存而不需要系统软件干预;当该位为0时,PCIe设备从D3cold状态迁移到D0状态时,需要进行复位操作;

10. PME Enable(读写):该位为1时,PCIe设备可以发送POME消息;当为0时,不能发送PME消息;

11. Data Select(读写):系统软件通过该组字段读取/计算PCIe设备处于不同状态下的功耗;

12. PME Status位(只读/写1清除):该位为1时表示PCIe设备可以正常发送PME消息,系统软件对此位写1时将该位清除;

13. PCIe总线没有实现对B2/B3 Support和Bus Power/Clock Control Enable位,这些只用于PCI总线的电源和时钟管理。

3.2 PCI Express Capability结构

PCI Express Capability结构存放了与PCIe总线相关的信息,包括PCIe链路和插槽的信息;该字段中:Cap ID为PCI Express Capability结构使用的ID号,其值为0x10;Next Capability字段为存放下个Capability寄存器的地址。其寄存器组成如下图所示。PCI Express Capabilities Register中存放了与PCIe设备相关的一些参数:

1. Capability Version(Bit3~0):存放PCIe设备的版本号;

——举个栗子:设备基于PCIe总线规范2.x,那么该字段值为0x2;若基于PCIe总线规范3.x,那么该字段值为0x3。

2. Device/Port Type(Bit7~4):存放PCIe设备的属性;0xb0000:EP;0xb0001:传统PCIe总线的EP;0xb0100:RC的Root Port;0xb0101:Switch的上游端口;0xb0110:Switch的下游端口;0xb0111:PCIe桥片;0xb1000:PCI/PCI-X to PCIe桥片;0xb1001:RC中集成的EP;

3. Slot Implemented(Bit 8):该位为1时,表示和当前端口相连的是一个PCIe插槽;

4. Interrupt Message Number(Bit13~9):该字段存放MSI/MSI-X中断机制所需要的Message Date字段。

具体的Device、Link、Slot相关的Capabilities寄存器定义,请参考PCIe协议。这些寄存器定义了PCIe总线链路、设备的工作模式、状态,以及设备管理信息等等。在后续的章节中会涉及到。